基于USB和FPGA的多功能等效器設計

蘇虎平,沈三民,劉文怡,葉 勇,張 昊

(中北大學電子測試技術國家重點實驗室,儀器科學與動態測試教育部重點實驗室,山西 太原 030051)

責任編輯:時 雯

等效器是一種自動測試系統,是用以產生各種模擬、正弦、串行數字、時間指令脈沖等控制和測試信號,并進行事后數據分析和處理的自動測試平臺。等效器由計算機進行整體控制,由上位機下發命令到等效器的等效功能模塊產生所需要的各種測試信號,并將需要檢測的數據讀回來存儲、分析、處理,本文設計的等效器的多功能性體現在它不僅可以提供控制和測試信號給遙測設備的地面系統測試中,還可以對被測設備(遙測系統)進行實時監控、功能檢測和故障定位診斷等。

傳統的通信接口通常采用PCI總線或者是RS-232總線。PCI總線有較高的傳輸速率,可達132 Mbit/s,也可以即插即用,但是其擴展槽有限且插拔不方便;RS-232連接比較方便,但是傳輸速率太低。由于USB具有有傳輸速度快、占用資源少、真正的即插即用,且與PC產業的一致性和成本低廉等優點,使其迅速在市場中流行。FT245RL是FTDI公司的快速USB通信接口解決方案之一,它無需編寫片內固件程序,PC機使用FTDI公司提供的官方驅動程序D2XXDRIVER,FT245RL芯片的主要功能是在內部硬件邏輯的作用下實現USB串行數據與并行數據的雙向轉換。因此,基于FT245RL的USB設備在測試系統中有很大的優越性。本文上位機通過USB接口與FT245RL進行數據交換,FT245RL則通過并行方式與等效器主控 FPGA 通信[1-2]。

1 系統整體設計思路和結構簡介

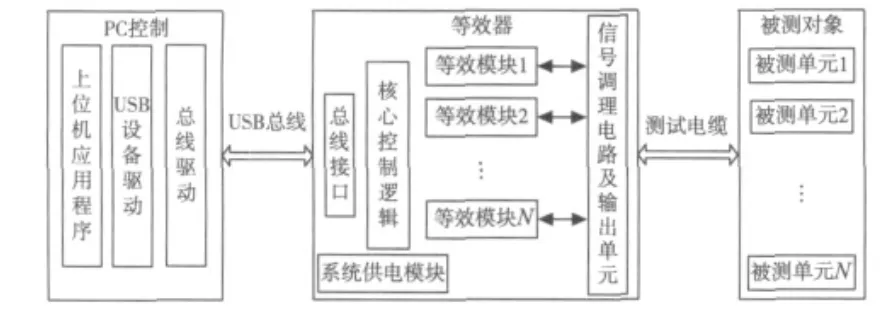

設計采用FT245RL和FPGA實現數據的通信,FPGA作為主控制器,FT245RL作為與PC機的USB通信接口。FPGA通過FT245RL接收上位機傳輸的命令、數據,然后根據上層通信協議判斷命令和數據類型,轉發上位機命令、數據到各功能模塊以實現不同的功能。為了匹配USB讀數速率和422異步串行通信發送數據速率的不同,采用FPGA內部實現FIFO緩存通信數據。本設計盡量進行模塊化設計、彈性設計,可隨時對系統進行升級改進,擴大如圖1中所示的等效模塊,系統整體架構見圖1。

2 硬件模塊設計

2.1 基于FT245的USB接口部分設計

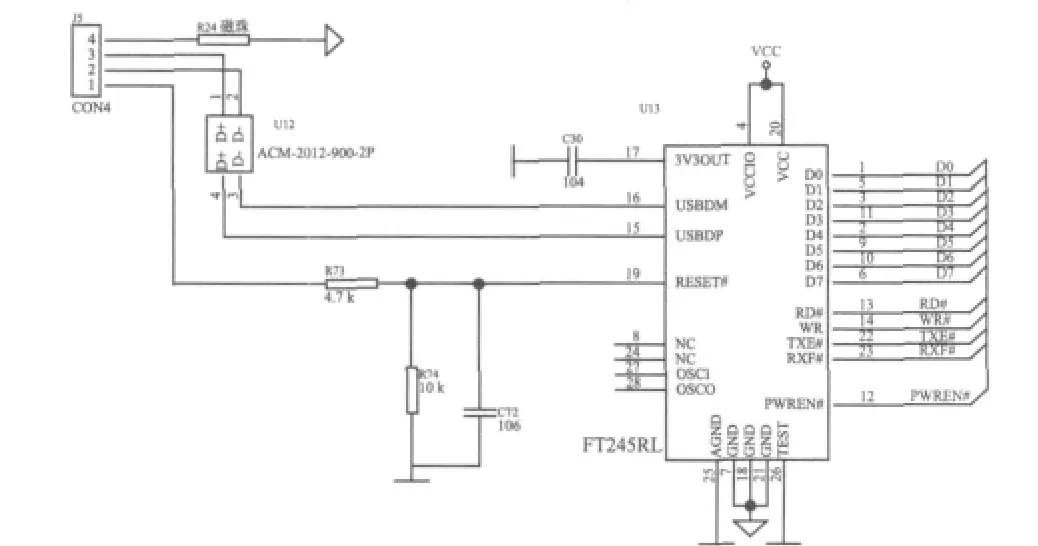

圖2為FT245RL的USB接口電路。FT245RL 內含兩個FIFO數據緩沖區。一個是128 byte的接收緩沖區,另一個是384 byte的發送緩沖區,它們用作USB數據與并行I/O口數據的交換緩沖區。FIFO主要是通過8根數據線DO~D7、讀寫控制線RD和WR、FIFO發送緩沖區空標志TXE和FIFO接收緩沖區非空標志RXF的配合來完成數據的交互。本設計采用自供電方式,上電復位,采用內部晶振。圖中ACM-2012-900-2P共模電感和磁珠是為了減少主機和設備的干擾,PWREN管腳用于判斷USB總線是處于掛起狀態還是正常狀態,D0~D7是8根數據線,、WR是FT245與FPGA相連的控制線。

圖1 等效器系統整體結構圖

圖2 等效器系統USB接口電路

2.2 直流量部分設計

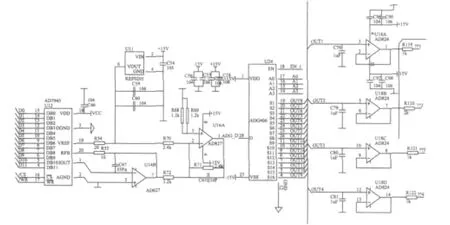

系統設計了16路模擬信號的輸出電路,對于不同電壓值可調的直流量信號,最好的選擇就是用D/A轉換電路產生小幅值電壓,然后運用信號調理電路產生所需要的電壓值。對于如此多路直流信號,如單獨實現每一路直流信號則會造成太大的浪費和成本的提高,因為各直流量信號的變化速度相對有限,因此本設計用模擬開關分時切換進行多路信號的輸出,這樣只需運用一片D/A轉換電路就可產生多路模擬直流信號。本設計由D/A轉換電路、運算調理電路、模擬電子開關、電壓保持電路組成。其具體電路如圖3所示。

DAC電路的設計需要考慮主要因素主要有轉換精度、轉換速度、電源要求等。此外溫度特性、數據耦合、焊接毛刺和非線性誤差的影響也不容忽視。本設計選用ADI公司的AD7945作為DAC芯片,它是12位乘法型并行輸入、單通道的電流輸出型低功耗數模轉換芯片,具有低溫漂、良好線性度的特性,采樣速率可達l.7 MSample/s,轉換時間最大值為760 ns,可直接與TTL或CMOS邏輯電平進行連接,本設計由REF0205輸出穩定的5 V電壓來作為基準電壓,分辨力約為0.00122 V,精準度高。

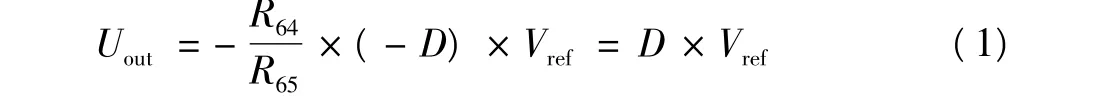

圖3 D/A轉換電路

因為要輸出模擬電壓值,需將AD7945的輸出電流轉換為電壓。設計時輸出經兩級反相運放轉換為需要的電流。前一級I/U轉換,后一級為利用反相比例放大電路設計的一階低通濾波器,輸入阻抗較小。由運算放大電路的運算公式可知

式中:Uout為AD7945轉換輸出并調理后的模擬量采樣幅值電準電壓;D為模擬電平的量化值。

如上文所述,任務要求產生多路模擬直流信號,因此本設計將D/A轉換電路調理輸出的電壓值經過模擬開關分時輸出以“同時”產生多路直流信號。系統采用ADI公司的模擬開關ADG506,其具有16路模擬數據通道,電壓輸出范圍寬泛、功耗低,并且兼容CMOS/TTL電平標準,最大導通時間400 ns,開啟時間為50 ns,導通電阻一般為280~600Ω。因為要保證各通道獨立持續輸出模擬量,所以使用存儲芯片SRAM對各通道要轉換的數字量進行存儲。FPGA的進程觸發后,從SRAM中一次讀取數字量,并控制模擬開關切換到相應的通道。模擬開關的A0~A3值與SRAM的地址線是同一數字線,這樣不同的SRAM存儲單元對應不同的通道號。

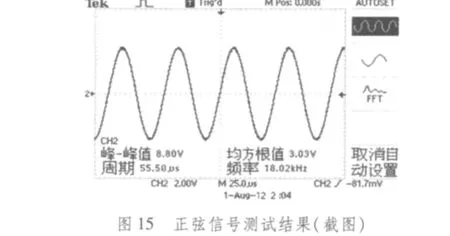

2.3 正弦信號部分設計

AD558是電壓輸出型的D/A轉換器,輸出電壓范圍為0~10 V,再經過由運算放大器構成的差動減法電路,實現電壓范圍從0~10 V到-5~+5 V的轉換,這個差動減法電路還具有電壓放大的功能,將轉換的電壓放大兩倍,實現-5~+5 V到-10~+10 V范圍的電壓輸出;再經過其后由RC和電壓跟隨器電路構成的簡易有源低通濾波器,實現電壓平滑輸出,使用電壓跟隨器是因為其輸入阻抗很大,輸出阻抗很小,實現前后電路阻抗的匹配,電壓的完整輸出。首先上位機軟件將所需要產生的一定頻率、幅值的正弦波形量化,采樣256個點,計算出每個點的電壓;然后通過USB接口將量化數據傳送給主控FPGA,主控FPGA將這些數據寫入正弦波形存儲RAM;再由FPGA根據接收到的正弦波形的頻率等參數計算出正弦波形的周期以及每兩個點的時間間隔,將時鐘分頻到所需的周期,按照頻率參數讀取RAM中的數據送往D/A轉換電路輸出,從而產生所需正弦交流信號,圖4為正弦信號產生電路。

圖4 正弦信號產生電路

2.4 特定幀結構的異步串行通信部分設計

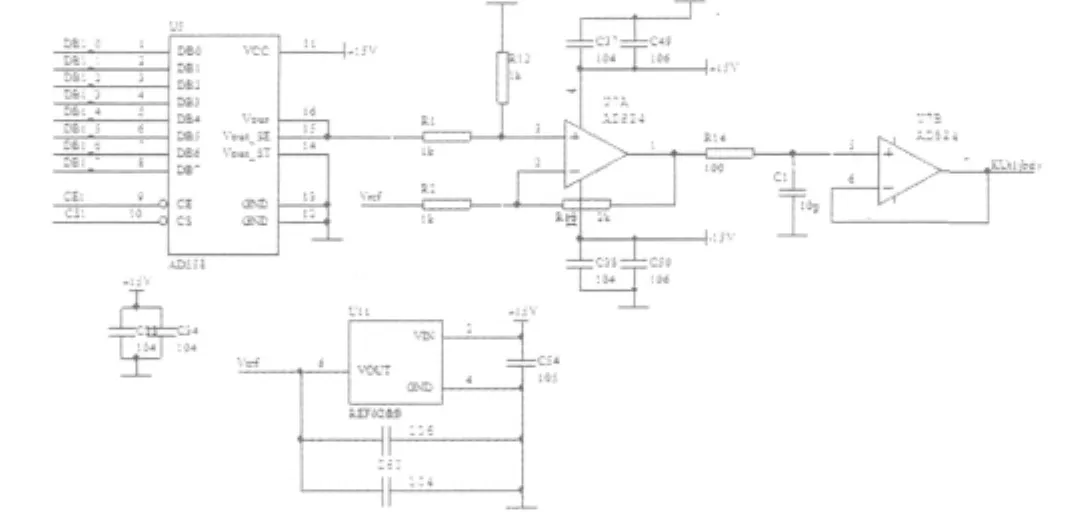

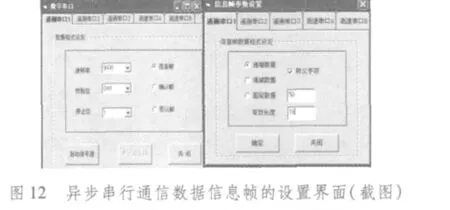

設計選用DS26C31作為RS-422發送控制器,用FPGA控制產生所要求幀結構的異步串行數據。硬件電路如5圖所示,在發送端分別串聯50Ω的限流保護電阻,為了防止大電流對輸入端的影響。DS26C31的作用是將輸入端TTL/CMOS電平轉換為RS-422電平,具體的異步串行通信的數據發送波特率、時序和幀結構等特性都由FPGA來實現。對于異步串行通信來說,數據的傳送涉及眾多的參數:對于每一字節數據設計的參數有:波特率、數據位的數量、停止位的數量、奇偶校驗位等;對于數據幀來說涉及的參數有:幀類型、一幀數據的數量、幀數據的組織方式等。本設計按照任務要求的RS422異步串行通信數據幀格式為:波特率可變(可選擇為4800,9600,19200,38400,115200,1152000),數據字節校驗方式可變(可選擇為奇校驗、偶校驗),停止位數量可變(1位停止位或2位停止位);幀結構類型可選擇(信息幀、確認幀、否認幀),信息幀組織形式可變(遞增數據、遞減數據、固定數據),信息幀數據數量可變,信息幀起始字節可設置等[3]。

圖5 RS-422電平轉換電路

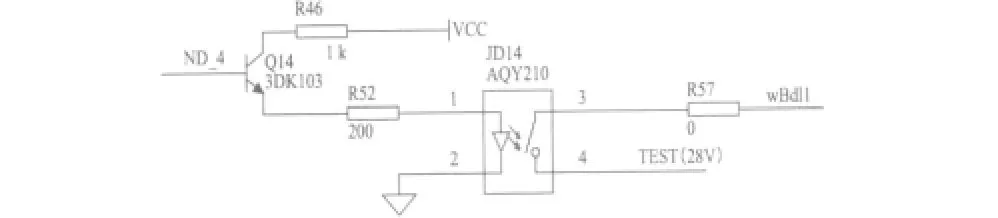

2.5 時間指令脈沖信號部分設計

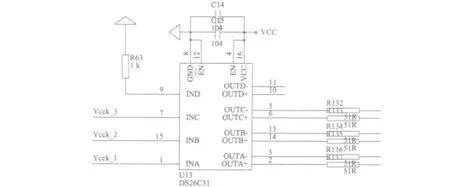

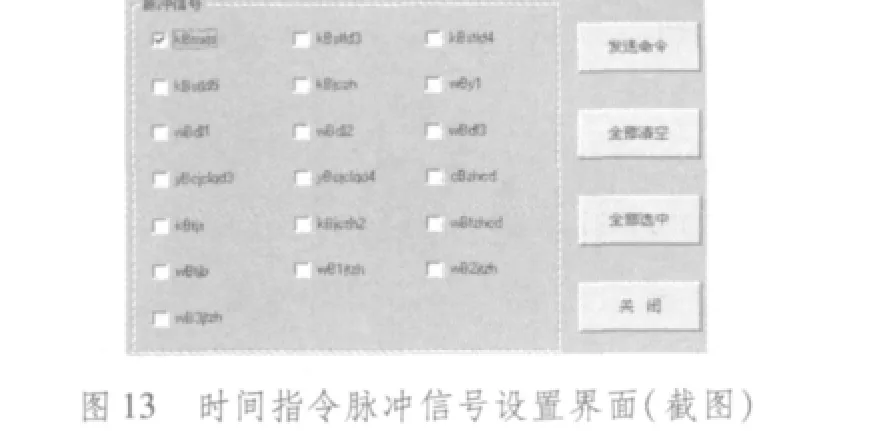

本設計由FPGA控制光耦AQY210來實現所需的時間指令(包括帶點指令和不帶點指令)。帶電不帶電時間指令信號電路設計類似,只不過帶電指令信號的供電電壓由等效器提供;而不帶電指令信號的供電由測量系統來提供。AQY210具有噪聲低、速度快、體積小、壽命長、觸發電壓低等優點,常用于信號的傳遞、電器隔離的場合。本設計采用此電路實現了時間指令信號。用FPGA管腳接到三極管3DK103的基極來控制三極管的通斷:當FPGA輸出“0”電平時,三極管工作在截止狀態,發射極輸出低電壓低電流,這樣AQY210不導通,信號輸出端口工作在高阻態;當FPGA輸出“1”電平時,三極管工作導通,發射極輸出高電壓高電流,驅動AQY210導通。時間指令信號的設計就是在上述開關電路的基礎上,FPGA收到上位機發來的命令后,判斷命令類型,確定通道號,之后啟動計數器來實現規定時間的開關電路的通斷來實現的,如圖6為時間指令脈沖硬件電路部分設計。

圖6 時間指令脈沖電路

3 等效器應用層通信協議

等效器產生的信號類型和數量眾多,且這些信號模塊都必須受上位機的控制,為便于對這些信號控制模塊進行統一管理,本文設計了統一的等效器應用層協議,此協議包括各類信號幀結構的設計和協調一致的工作流程。

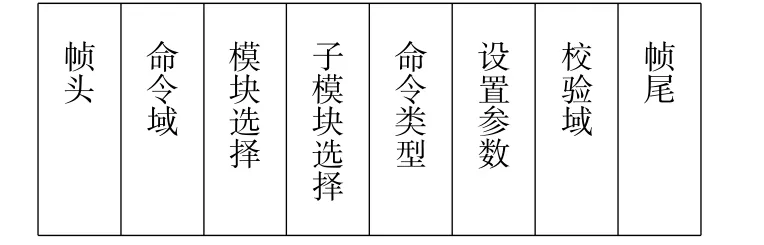

本設計中一幀有10 byte,其中幀頭2 byte,命令域、模塊選擇、子模塊選擇、命令類型、校驗域和幀尾各占1 byte,設置參數占2 byte。命令域包括包括自檢和握手命令、停止命令、各功能模塊接收信號命令;模塊選擇和子模塊選擇代表不同功能模塊的邏輯地址;設置參數包括直流信號、時間指令脈沖信號、422異步串行輸出信號、正弦信號、模擬信號清零復位信號;校驗域采用奇校驗,通過校驗域來保證命令和數據傳輸的可靠性[4]。應用層通信協議幀結構的設計如圖7所示。

圖7 應用層通信協議幀結構

4 系統軟件設計

4.1 USB讀寫時序

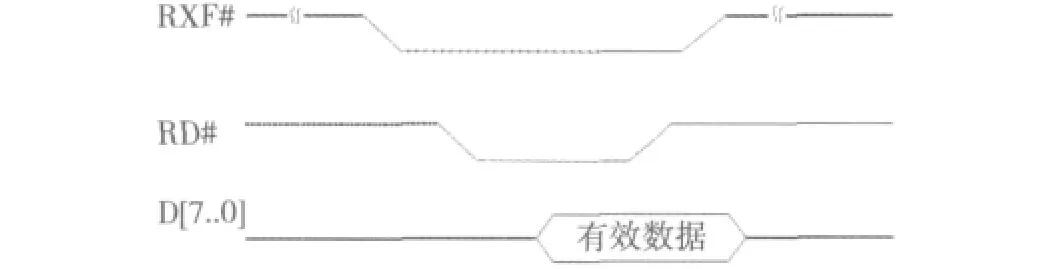

接收數據時序圖如圖8所示。接收數據的過程是外控制器(本設計為FPGA)不斷查詢FT245RL的RXF引腳狀態,如果RXF引腳為高電平,說明芯片正處于接收數據狀態;當RXF為低電平,則說明芯片已經接收完成一字節數據并存儲到FT245RL的接收緩沖區(接收FIFO);外控制器隨即驅動RD引腳由高變低產生讀控制時序,即可讀取接收FIFO中數據到外控制器的數據緩沖區。重復上述接收數據步驟即可實現一幀數據的接收,然后即可進行幀處理,實現既定的功能。

圖8 接收數據時序圖

RT245RL發送數據時序圖見圖9。發送數據到上位機的過程主要是外控制器(FPGA)不斷查詢FT245RL的TXE引腳電平,當其為高電平說明上一次寫入數據的過程還未完成;當其變為低電平表明FT245RL發送邏輯空閑,外控制器將所需發送數據準備好后,驅動WR引腳由高到低產生下降沿即可將緩沖區內數據寫入FT245RL的發送FIFO,隨后FT245RL在適當的時候自動將數據發送給上位機,重復上述發送數據步驟即可實現上傳數據給上位機。

圖9 發送數據時序圖

4.2 VB上位機軟件設計

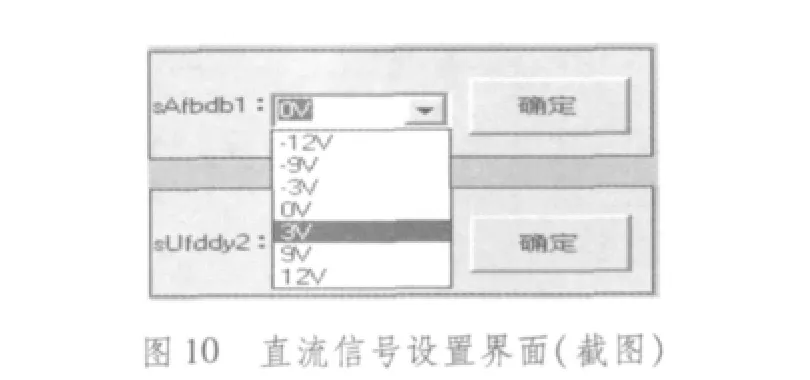

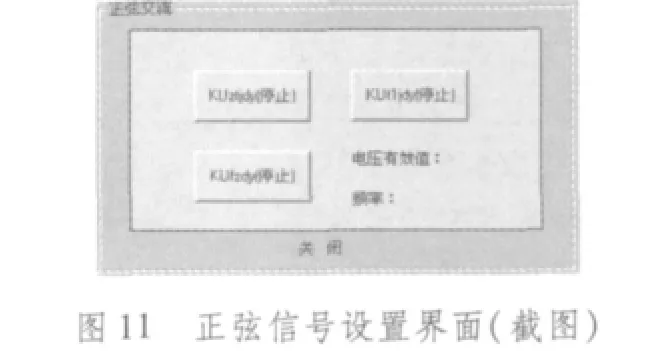

設計由各硬件電路模塊實現任務要求的具體功能,由上位機對整個等效器的工作進行整體控制,上位機通過發送啟動命令、設置參數與等效器進行數據交互。上位機與等效器通過USB總線接口進行通信,通信協議參見“等效器應用層協議”。其中每一類信號的命令信息幀根據“等效器統一幀結構”的格式而制定,上位機與等效器硬件電路的數據通信流程嚴格按照“上位機向主控模塊發送命令通信協議”的規定執行,具體見圖10~圖13。

5 測試結果

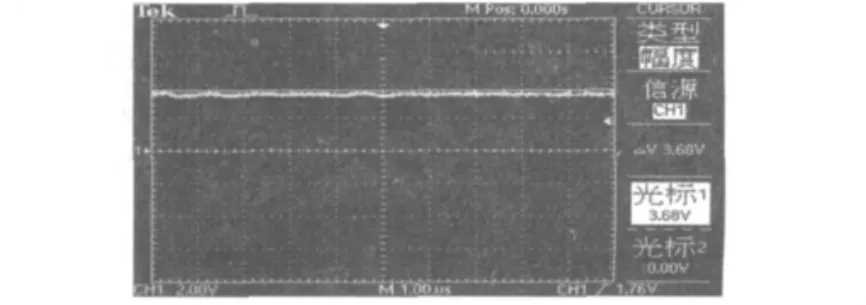

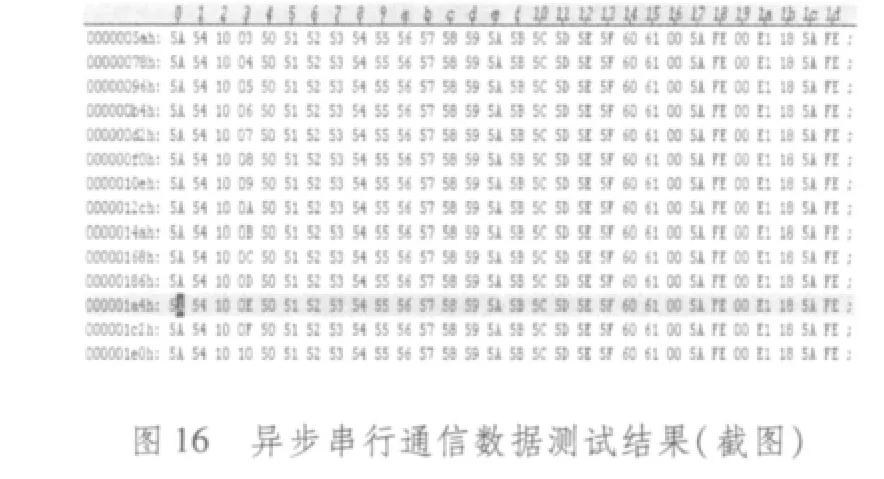

圖14為按照圖10的設置測試一路直流信號的結果;本文設計的是多路固定頻率和固定幅值的正弦信號,圖15為按照圖11測試的一路峰峰值為9 V、頻率為18 kHz的正弦信號的結果;圖16為按照圖12的設置測試了異步串行通信數據幀的結果數據(確認幀和否認幀與此類似);圖17為按照圖13的設置測試了一路幅值是28 V的100 ms時間指令脈沖信號,由此可見本文設計的等效器能很好地提供遙測設備在系統地面測試對外系統控制和測量參數的要求。

圖14 直流信號測試結果(截圖)

6 結束語

本文提出一種外系統等效器的設計及實現方案,利用模塊化工程設計思想,將整個等效器任務按照功能要求分為各個子模塊單獨實現,在實現功能的基礎上充分保留設計裕量,以備對系統進行升級改進,進行彈性設計,可以很好地測試外系統遙測設備的可靠性和監測功能。此方案實現的等效器已成功應用于某型號航天器遙測設備的地面測試系統中,經調試和測試后,該等效器工作穩定,滿足工業現場的要求,達到設計目的。

[1]李娜,孟令軍.用FT245BM實現FPGA與PC機的數據無縫傳輸[J].重慶工學院學報:自然科學版,2009,23(5):80-83.

[2]孫立輝,劉院英,和志強.基于FT245BM和FPGA的USB接口設計[J].微計算機信息,2006(2):183-185.

[3]高世杰,竺曉山,吳志勇,等.基于USB2.0的多路異步串行系統設計[J].電視技術,2005,29(7):91-93.

[4]陳志良,曾浩.基于DSP+FPGA視頻信號處理器的USB擴展及應用[J]. 電視技術,2011,35(23):44-47.