膈神經脈沖刺激儀的研制

錢明理 王 成

膈神經是頸叢中最重要的分支,其中的運動纖維支配膈肌。膈神經放電呈周期性,表現出特征性的高頻振蕩現象,頻率為100次/s左右。神經斷裂后即失去推動傳導沖動的作用,一般認為神經細胞損壞后不能再生,而神經纖維在一定條件下是可以再生的[1]。雪旺細胞在神經再生中起著重要作用。損傷遠側雪旺細胞分裂增殖形成索帶,對再生軸突起引導作用,并可誘導生長錐的遷移方向。雪旺細胞與靶器官還能分泌多種神經營養因子(neurotrophin,NT),如神經生長因子(nerve growth factor,NGF)等數十種多肽或蛋白類活性物質,營養、支持神經細胞的增殖代謝和調控軸突的再生與髓鞘的形成[4]。

電刺激能通過促進雪旺細胞和NGF的一系列活動而加速神經再生。雪旺細胞在生長及遷移時分泌大量的NGF,而電場使NGF受體向陰極移動,隨即NGF聚集在遠端并誘導軸突也向遠端生長。目前,電刺激能促進神經再生已得到公認[5-6]。

研究表明, 模擬膈神經脈沖能有效地促進周圍神經損傷后神經纖維再生,對周圍神經損傷的治療和康復有比普通的電刺激更好的療效[2-3]。

生物刺激器在臨床的應用較為廣泛,如心臟起搏器對心臟起搏點的刺激;通過圖像、聲音等的刺激可用于觀察腦電的變化;肌肉刺激器能用于觀察肌肉的收縮情況等。本文所描述的膈神經刺激器目前在臨床上還未得到應用,而且該領域涉足的人不多,可參考的文獻資料極少,故該神經刺激器的研制是一個開拓的過程,值得嘗試。

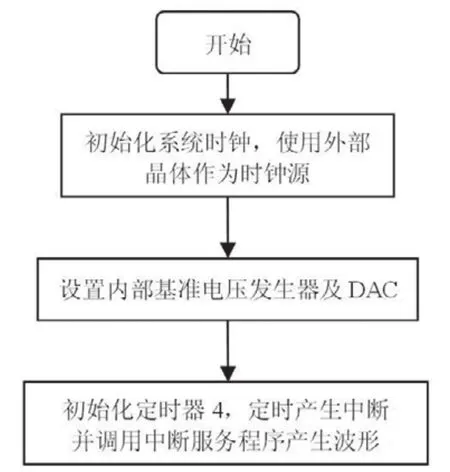

利用已采集到的膈神經模擬信號,設計一種程控電脈沖神經刺激器,可植入動物體內長久發放一個信號電脈沖,用以幫助受損的周圍神經修復。本研究通過以下3個步驟來實現(如圖1所示):

圖1 步驟圖

1 刺激器設計原理

美國Cygnal公司所設計的Cygnal C8051F系列單片機,其運行速度達到25 MIP/s。Cygnal C8051F系列單片機是集成的混合信號片上系統,具有與MCS-51內核及指令集完全兼容的微控制器,除了具有標準8051的數字外設部件之外,片內還集成了數據采集和控制系統中常用的模擬部件和其他數字外設及功能部件[7]。Cygnal C8051F系列單片機的功能部件包括模擬多路選擇器、可編程增益放大器、ADC、DAC、電壓比較器、電壓基準、溫度傳感器、SMBus/I2C、UART、SPI、可編程計數器/定時器陣列(PCA)定時器、數字I/O端口、電源監視器、加密狗定時器(WDT)和時鐘振蕩器等。所有器件都有內置的FLASH存儲器和256字節的內部RAM,其中FLASH存儲器既可用作程序存儲器又可用作于非易失性數據存儲。應用程序可以使用MOVC和MOVX指令對FLASH進行讀或改寫。有些器件還可以訪問外部數據存儲器RAM,即XRAM(如圖2所示)。

圖2 C8051F020原理框圖

1.1 主程序總體設計

利用C語言編程使C8051F020器件的片內數/模轉換器(DAC)將已采集的數據表通過使用累加算法實現一個中斷驅動的函數發生器,最終輸出頻率與幅度可調的模擬信號波形。根據要求,程序流程如圖3所示:

圖3 主程序流程圖

1.2 部分程序設計

1.2.1 設置系統時鐘

C8051F微控制器擁有高速CPI-51內核,系統時鐘最大可達25 MHz,因此考慮使用外部的振蕩源-22.1184 MHz的晶體(外部振蕩源才能達到此較高的振蕩頻率,且有相當高的精度)[8]。當外部振蕩器穩定運行時,晶體振蕩器有效標志(OSCXCN寄存器中的XTLVLD)被硬件置‘1’。XTLVLD檢測電路要求在允許振蕩器工作和檢測XTLVLD之間至少有1 ms的啟動時間。在外部振蕩器穩定之前就切換到外部振蕩器可能導致不可預見的后果。因此,在設置系統時鐘考慮其過程如下:①允許外部振蕩器;②等待1 ms;③查詢XTLVLD‘0’->‘1’;④切換到外部振蕩器。

1.2.2 禁止加密狗定時器(WDT)

MCU內部有一個使用系統時鐘的可編程加密狗定時器(WDT)。當加密狗定時器溢出時,WDT將強制CPU進入復位狀態。根據實際需要,要求禁止WDT以防止意外產生的禁止操作。向WDTCN寄存器寫入0×DE后再寫入0×AD可禁止WDT,但注意:寫0×DE和寫0×AD必須發生在4個時鐘周期之內,否則禁止操作將被忽略。

程序中與上述對應的源代碼為:

1.2.3 設置內部基準電壓發生器及DAC

電壓基準電路為控制ADC和DAC模塊工作提供了靈活性。C8051F有3個電壓基準輸入引腳,允許每個ADC和2個DAC使用一個外部電壓基準或片內電壓基準輸出[9]。在使用DAC之前,必須通過設置REFnCN寄存器的相應位來使能內部電壓基準。內部電壓基準電路由一個1.2 V、15 ppm/℃(典型值)的帶隙電壓基準發生器和一個2倍增益的輸出緩沖放大器組成。內部基準電壓可以通過VREF引腳連到電壓基準輸入引腳。從芯片數據手冊中可知DAC工作所需VRER=2.4 V,而基準電壓發生器使用內部帶隙基準作為即可產生2.4 V的輸出電壓,因此在使用DAC之前,還必須通過設置REFnCN寄存器的相應位(BIASE 和REFBE)為‘1’來使能內部電壓基準。

程序中與上述對應的源代碼為:

每個C8051F020器件都有2個片內12位電壓方式數/模轉換器(DAC)。可以用對應的控制寄存器DAC0CN到DAC1CN允許/禁止DAC0和DAC1。在被禁止時,DAC的輸出保持在高阻狀態,DAC的供電電流降到1 μA或更小。每個DAC的電壓基準在VREFD引腳提供。

DAC為電壓輸出方式,有靈活的輸出更新機制,允許無縫滿刻度變化并支持無抖動輸出更新適合于波形發生器的應用。此更新機制允許用基于定時器4的溢出信號更新DAC輸出。 在ADC轉換操作中,ADC轉換可以由定時器溢出啟動,不用處理器干預。與之類似,DAC的輸出更新也可以用定時器溢出事件觸發。這一特點用于DAC產生一個固定采樣頻率的波形時尤其有用,這樣可以消除中斷響應時間不同和指令執行時間不同對DAC輸出時序的影響。當DAC0MD位(DAC0CN.[4∶3])被設置為‘10’時,對DAC數據寄存器的寫操作被保持,直到相應的定時器溢出事件(定時器4)發生時DAC0H:DAC0L的內容才被復制到DAC輸入鎖存器,允許DAC數據改變為新值。設計中采用定時器4溢出更新輸出,DACn輸出更新發生在定時器4溢出更新輸出之時。這意味著寫DACnH和DACnL并不立即影響DAC輸出,寫入值將被保持,直到發生下一次定時器4溢出時才更新DAC。

1.2.4 初始化定時器4并產生中斷

定時器4是一個16位的計數器/定時器,由2個8位的SFR組成:TL4(低字13節)和TH4(高字節)。它使用系統時鐘作為時鐘源。定時器4提供3種工作方式,這里采用方式1(自動重裝載的16位計數器/定時器),用于控制DAC輸出的采樣速率[10]。當計數器/定時器寄存器發生溢出(從0×FFFF到0×0000)時,自動重裝載方式的計數器/定時器將定時器溢出標志TF4置‘1’,產生一個中斷。溢出時2個捕捉寄存器(RCAP4H,RCAP4L)中的16位計數初值被自動裝入到計數器/定時器寄存器,定時器重新開始計數。設計中DAC采樣速率就是通過初始化定時器4的重載值來設置的,重載值是2次中斷之間的SYSCLK周期數。該值是負值,這是因為C8051定時器是向上記數的。可以用下面的公式計算該值,即:定時器4重載值=SYSCLK/SAMPLE_RATE_DAC DAC所允許的最大采樣速率大約為100 kHz,這是由10 μs的輸出建立時間決定的。在選擇DAC采樣頻率時,還必須考慮到2次定時器4中斷服務程序要執行的所有指令的最長時間,否則輸出頻率將受到影響。設計使用22.1 MHz的SYSCLK和80 kHz的DAC更新速率,這就允許ISR在276個SYSCLK周期內執行結束,這主要是在采樣速率和定時器4 ISR的執行時間之間進行權衡。

程序中與上述對應的源代碼為:

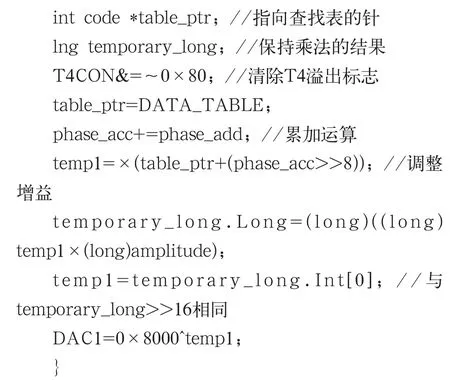

1.2.5 波形產生

在定時器4溢出時將調用中斷處理程序,波形產生完全在定時器4的ISR中完成,分為三級實現。所有產生的波形都用一個16位的累加器,用它來記錄輸出波形在橫軸上的位置。在給定DAC的更新頻率為80 kHz時,該累加器提供1.2 Hz的頻率分辨率。定時器4 ISR中的第一級根據波形的設置查找與累加器對應的下一個DAC輸出值。每次調用定時器4 ISR時,累加器的值增加

程序中與上述對應的源代碼為:

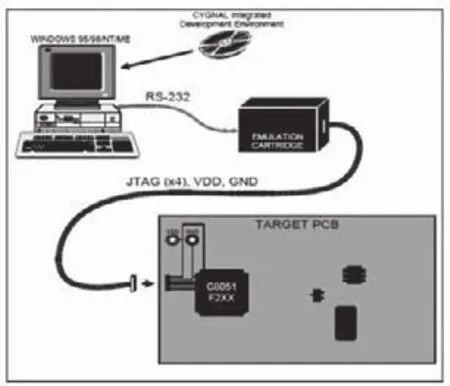

2 Cygnal C8051F單片機開發工具

Cygnal的開發工具實質上就是計算機IDE調試環境軟件及計算機USB口到C8051F單片機JTAG口的協議轉換器(EC2)的組合。Cygnal C8051F系列所有的單片機片內均設計有調試電路,該調試電路通過邊界掃描方式獲取單片機片內信息,通過4線的JTAG接口與開發工具連接以便于進行對單片機在片編程調試。適配器(EC2)一端與計算機相連,另一端與C8051F單片機JTAG口相連,應用Cygnal提供的IDE調試環境可以進行非侵入式、全速的在系統編程(ISP)和調試。開發工具與PC機(已安裝Cygnal IDE)硬件連接:在系統編程和調試環境如圖4、圖5所示。

圖4 硬件連接示意圖

圖5 Cygnal IDE

3 結果與討論

經過上述描述的過程,將產生膈神經模擬信號植入正常家兔進行活體實驗(如圖6、7所示)。

圖6 刺激器

圖7 膈神經模擬信號波形

其大致波形形狀與正常家兔膈神經脈沖信號(通過Matlab 6.5程序繪制波形)一致。該刺激器在示波器上的實際輸出頻率為200 Hz、幅度為2 V。由此,初步實現了神經刺激信號的發生。

目前,由于此類植入式神經刺激器研制領域的人不多,該神經刺激器的研制過程是一個開拓的過程,并無仿效先例,因此改進工作還將不斷進行。

[1]柏樹令.系統解剖學[M].5版.北京:人民衛生出版社,2001:50.

[2]夏奕俊,徐向陽,崔茂龍,等.模擬膈神經脈沖電刺激促進周圍神經再生的研究[J].中華實驗外科雜志,2004,21(10):1219-1221.

[3]夏奕俊,徐向陽,崔茂龍,等.膈神經脈沖電刺激促進周圍神經再生的實驗研究[J].中華手外科雜志,2004,20(4):246-248.

[4]Dong Z, Sinanan A, Parkison D, et al.Schwann cell development in embryonic mouse nerves[J].J Neurosci Res,1999,56(4):334-348.

[5]Weidner N, Blesch A, Grill RJ, et al. Nerve growth factor-hypersecreting Schwann cell grafts augment and guide spinal cord axonal growth and remyelinate central nervous system axons in a phenotypically appropriate manner that correlates with expression of L1[J].J Comp Neurol,1999,413(4):495-506.

[6]Varon S,Conner JM. Nerve growth factor in CNS repair[J].J Neurotrauma,1994,11(5):473-486.

[7]李勛.單片機實用教程[M].北京: 航空航天大學出版社,2006:65-71.

[8]馬喜順,陶庸.高速SOC單片機C8051F[J].電子產品世界,2002(5A):63-64.

[9]閻石.C8051F單片機應用解析[M].北京:航空航天大學出版社,2002:34-35.

[10]郭玉霞.MCS-51系列單片機原理與應用[M].北京:航空航天大學出版社,2010:44-46.