通信測試卡中HDLC協議控制器的設計與實現

劉延飛 李 琪 楊鐵阡 倪 亮

(第二炮兵工程大學專業基礎實驗中心,陜西 西安 710025)

0 引言

在航空航天領域中,大型地面測試設備測試數據具有傳輸量大、實時性要求高的特點。為了解測試設備與上位機的通信狀況,需采用一種面向比特級的同步通信協議,實現數據傳輸過程的完全透明。高級數據鏈路控制(high level data link control,HDLC)協議具有上述優點,同時,它能保證傳遞到下一層的數據在傳輸過程中能夠被準確接收,且一旦接收端接收到數據,就能立即傳輸下一幀數據[1]。

HDLC的一般實現方法是采用專用集成電路(application specific integrated circuit,ASIC)器件和軟件編程等。采用ASIC器件設計比較簡單,但靈活性較差;軟件編程方法靈活,但占用處理器資源多、執行速度慢、實時性不易預測。現場可編程門陣列(FPGA)采用硬件描述語言處理信號,可以通過軟件反復編程使用,能夠兼顧速度和靈活性,還能并行處理多路信號,便于實時預測和仿真,所以在FPGA中實現HDLC協議的功能是一種較為合適的選擇[2]。

根據課題具體要求,發送端和接收端的數據內容是固化的,只需檢測測試設備能否與上位機進行正常通信,所以在數據傳輸過程中可以不加CRC校驗[3],本文將介紹一種簡化HDLC協議控制器的方法。

1 HDLC協議簡介

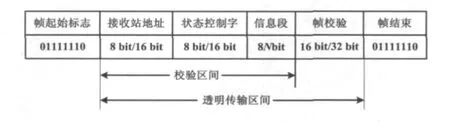

HDLC協議是通信領域中應用最廣泛的協議之一,其面向比特的高級數據鏈路控制規程,具有差錯檢測功能強大、效率高和傳輸同步的特點[4]。在HDLC通信方式中,所有信息都是以幀的形式傳送的。HDLC幀格式如圖1所示。

圖1 HDLC幀格式Fig.1 Frame format of HDLC protocol

1.1 標志字

根據HDLC協議規定,所有信息傳輸必須以一個標志字“01111110”開始,且以同一個標志字結束。由開始標志到結束標志之間構成一個完整的信息單位,稱為一幀。接收方可以通過搜索“01111110”來探知幀的開始和結束,從而建立幀同步。在幀與幀之間的空載期,可連續發送標志字來作填充。

1.2 “0”比特插入技術

HDLC幀的信息長度是可變的,可傳送除標志字以外的任意二進制信息。為確保標志字獨一無二,發送方在發送信息時采用“0”比特插入技術,即發送方在發送除標志字符外的所有信息時(包括校驗位),只要遇到連續的5個“1”,就自動插入一個“0”;反之,接收方在接收數據時,只要遇到連續的5個“1”,就自動將其后的“0”刪掉。“0”比特插入和刪除技術使得HDLC具有良好的傳輸透明性,可傳輸任何比特代碼。

1.3 地址段及控制段

地址字段為8位,也可采用8的倍數進行擴展,用于標志接收該幀的棧地址。控制字段為8位或16位,發送方的控制字段用來表示命令和響應的類別與功能。

2 HDLC協議控制器的FPGA實現

基于FPGA實現的HDLC協議控制器主要包括發送和接收兩個模塊[5]。

2.1 發送模塊的設計

發送端先將待發送的并行數據進行并串轉換,然后由系統自動完成編碼、“0”比特和標志字“7E”插入,最后將處理后的數據序列傳遞到發送端口。根據前文所述,由于每一幀的數據內容固定,因此,可將CRC結果視為固定值“E2、99”,直接將其添加到發送端數據序列即可。

2.1.1 發送模塊工作原理

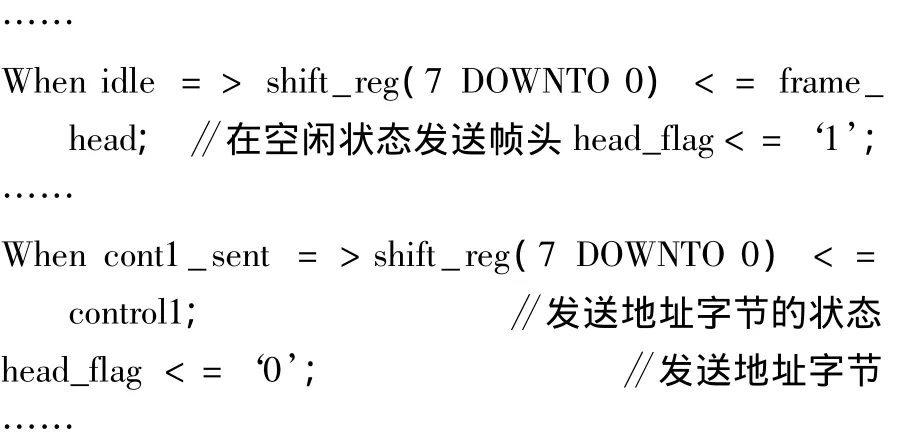

設計的代碼主要由以下進程組成:① HDLC數據發送狀態機狀態轉移進程,完成HDLC數據發送狀態機各個狀態對應的信號輸出,包括標志信號和控制信號;②移位寄存器進程,通過移位實現數據并串轉換,并按添零要求對串行數據序列做相應處理;③添零進程,當遇到連續的5個“1”時,自動進行添零處理,最后產生正確的、經過添零處理的HDLC數據序列。其部分源代碼如下[6]。

在空閑狀態,發送HDLC的幀頭(7E);在地址發送狀態,發送地址字節內容(5A 4A);然后轉入控制字節發送狀態,發送控制字節(54);進入HDLC幀尾發送狀態,將幀尾(7E)發送出去,發送完幀尾,轉入到空閑狀態,等待新數據的到來。

2.1.2 試驗結果和分析

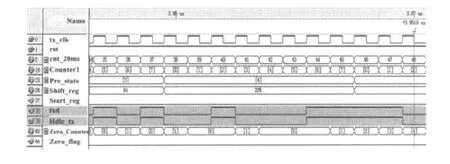

發送模塊的試驗仿真結果如圖2所示。

圖2 發送模塊仿真結果Fig.2 Simulation result for transmitting module

當發送數據幀頭“01111110”后,起始標志位start_flag置高,開始發送接收地址和控制字等數據內容。數據并串轉換計數器counter1和添零計數器zero_counter開始計數,發送的數據依次存入移位寄存器shift_reg。數據發送信號txd,按照預定格式向串行數據序列hdlc_tx依次賦值,實現數據的正確發送。

2.2 接收模塊的設計

接收端首先接收同步串行數據,然后由系統自動完成標志字的檢測、去“0”,再將同步串行數據轉換成1位并行方式輸出。整個系統收發端使用同一個全局時鐘。下面分別對接收模塊各個部分進行介紹。

2.2.1 幀頭檢測模塊

本進程用來檢測幀頭“7E”是否出現,如果檢測到“7E”,則表明接收到一個完整的數據;反之,則繼續接收數據[7]。

2.2.2 去“0”模塊

本進程用來檢測接收的數據是否包含插入的“0”比特,當檢測到插入的“0”比特后,對其進行刪除,并進行數據串并轉換。

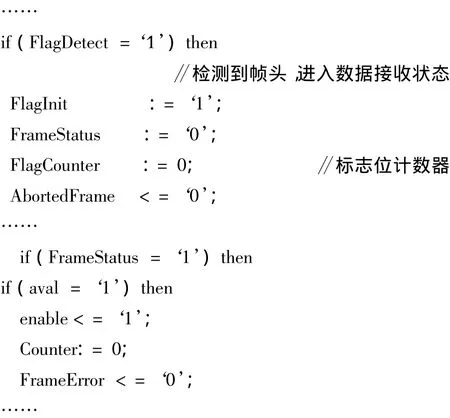

2.2.3 接收控制模塊

本進程用于接收過程的控制,主要包括通過檢測是否出現幀頭來判斷接收的數據是否為有效幀,以及產生接收使能信號。其部分VHDL代碼如下。

2.2.4 試驗結果和分析

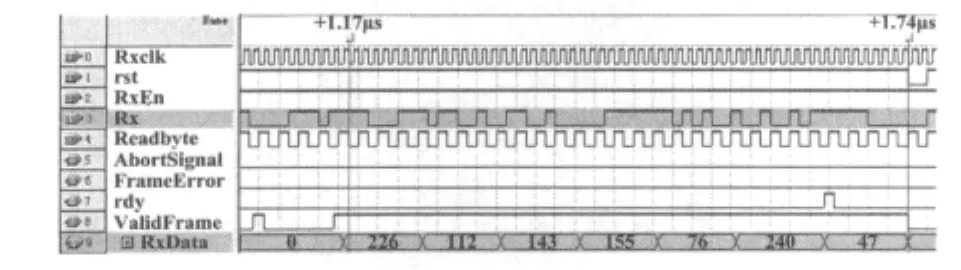

整個接收模塊的試驗仿真結果如圖3所示。

圖3 接收模塊仿真結果Fig.3 Simulation result for receiving module

當接收的串行數據出現幀頭“01111110”時,幀有效信號被拉高,開始進行串并轉換,并將接收數據放入到接收緩存中,實現數據的存儲。

3 結束語

針對某型地面測試設備通信測試卡的技術要求,文中提出了一種利用FPGA簡化HDLC協議控制器的設計方案,并利用Altera公司的EP2C70F67218芯片來實現。

與傳統的HDLC協議的實現方法相比,該控制器更加簡單可靠;且由于數據幀傳輸過程中沒有采用標準的CRC校驗,使得數據傳輸速度更快。軟件仿真和代碼調試證明,本控制器能夠應用于通信測試卡的測試,具有一定推廣價值。

[1]黃國強.HDLC協議的FPGA實現及其在通信系統的應用[J].五邑大學學報,2008(22):40-44.

[2]徐濤.基于PCI的HDLC協議處理器的設計與優化[D].南京:東南大學,2005.

[3]劉巖俊,閆海霞.HDLC通訊協議中CRC的應用[J].電子測量技術,2010(3):21-23.

[4]李曉娟.基于FPGA的HDLC設計實現[J].現代電子技術,2007(6):35-37.

[5]應三叢.基于FPGA的HDLC協議控制器[J].四川大學學報:自然科學版,2008(40):116-120.

[6]潘松,王國棟.VHDL實用教程[M].成都:電子科技大學出版社,1999:158-169.

[7]徐欣,于紅旗,易凡,等.基于FPGA的嵌入式系統設計[M].北京:機械工業出版社,2005:79-102.