基于FPGA的等精度轉矩轉速測試儀

梁龍學 杜永文

(蘭州交通大學電子與信息工程學院,甘肅 蘭州 730070)

0 引言

傳統轉矩轉速測試儀對被測信號一般沿用“高頻用測頻法、低頻用測周法”。這種做法對提高測量精度無疑是十分有效的,但卻存在測量精度的離散性問題[1],且在整個測試范圍內測試精度差異很大,降低了測量結果的置信度;測試適用范圍小,一種儀器只能接一種型號的傳感器,缺乏通用性;需用測頻法及測周法分段測試,給用戶的操作和使用帶來極大不便;雖有在線測試方案[2],但誤差太大。為此,本文提出一種等精度的、通用性強的轉矩、轉速測試方案。

1 測試儀組成及測量原理

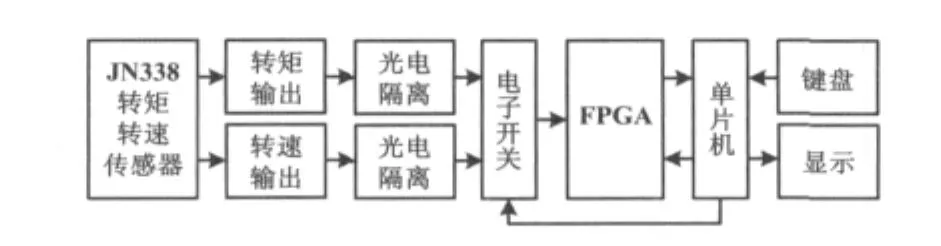

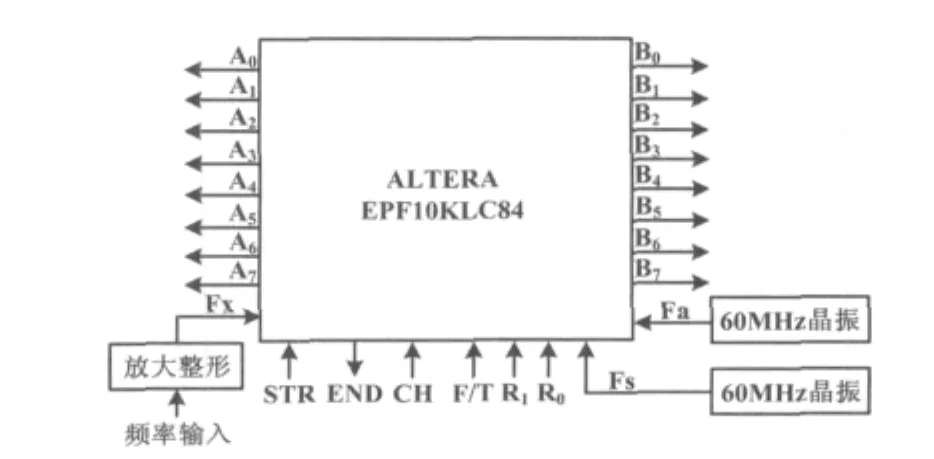

轉矩轉速測試儀由轉矩轉速傳感器(如JN338)、光電隔離、電子開關、FPGA、單片機、鍵盤和顯示等部分組成。JN338負責信號采集,它能將旋轉動力系統或機電一體化設備的轉矩、轉速等被測信號轉化為標準的TTL數字信號。FPGA負責對上述數字信號的頻率進行精確測量,并送至單片機進行處理并顯示。單片機通過控制電子開關選取測試對象,同時還控制FPGA的采樣速率和測量方式等。轉矩轉速測試儀整體結構如圖1所示。

圖1 轉矩轉速測試儀結構圖Fig.1 Structure of torque and speed tester

1.1 轉矩轉速測量原理

根據輸出信號不同,轉矩轉速傳感器可分為正弦波輸出型和數字輸出型兩大類。如JN338為數字輸出型,其輸出信號可直接進行測試;它擁有20多種型號,且其總的轉矩測量范圍為1~5000 N·m,轉速測量范圍為10 ~60000 r/min。JN338測量原理簡述如下[3]。

轉速測量公式為:

式中:n為轉速,r/min;f為實測轉速輸出信號的頻率值,kHz;Z為傳感器測速齒數。

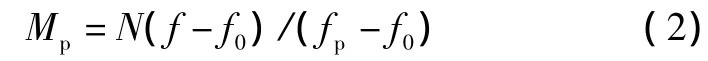

在有效的量程范圍內,傳感器轉矩輸出信號頻率與對應轉矩值基本上呈線性關系。轉矩輸出信號頻率在零點時,f0=10 kHz;正向旋轉滿量程時,fp=15 kHz;反向旋轉滿量程時,fr=5 kHz。轉矩實際輸出信號頻率用f表示。則正向轉矩為:

反向轉矩為:

式中:Mp為正向轉矩;Mr為反向轉矩;N為轉矩滿量程。如JN338100型對應轉矩測量范圍為10~100 N·m,可測最高轉速為6000 r/min,則公式中的N取100 N·m。

軸輸出功率由轉矩轉速傳感器輸出的轉矩及轉速值經過運算得到。軸輸出功率的計算公式為:

式中:P為軸輸出功率,kW;M為實際轉矩,N·m;n為轉速,r/min。

1.2 信號頻率的準確測量

由上述分析可知,轉速和轉矩的測量均與被測信號的頻率有關,所以測試儀整體測量的準確度在很大程度上取決于信號頻率的準確測量[4]。

直接測頻法常用的有測頻法和測周期法,但它們存在以下問題:±1計數誤差不可消除;頻率不同,測量精度不同,且差異很大;若用測頻法、測周法分段測試,則頻率銜接點難以選定,且存在測量精度跳變。采用等精度測頻法可以克服上述缺陷。

1.2.1 等精度頻率測量原理

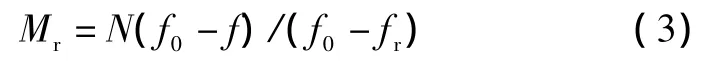

等精度測頻原理如圖2所示。

圖2 等精度測頻原理波形圖Fig.2 Waveform of the equal-precision frequency measurement

在等精度測頻法中,閘門時間不是固定值,而是被測信號周期的整數倍,因此消除了對被測信號計數所產生的±1個字誤差,并且達到了在整個測試頻段內的等精度測量。

在測量過程中,需使用兩個計數器分別對標準信號和被測信號進行計數。設在一次實際閘門時間t中計數器對被測信號的計數值為Nx,對標準信號的計數值為Ns,且被測信號周期、頻率分別用Tx和fx表示,標準信號用Ts和fs表示,則有:

即被測信號的頻率fx為:

具體測量過程為按下測量鍵,單片機即啟動預置閘門開啟信號(對應上升沿),此時計數器并未開始計數,而是要等到被測信號的上升沿到來時,測頻電路產生實際閘門開啟信號,計數器才真正開始計數。同樣地,預置閘門關閉信號(下降沿)到來時,計數器并不立即停止計數,而是要等到被測信號上升沿到來時,測頻電路產生實際閘門關閉信號后才真正結束計數。顯然,實際閘門時間t與預置閘門時間t1并不嚴格相等,但差值不會超過標準信號的一個周期[5-6]。

1.2.2 等精度頻率測量誤差分析

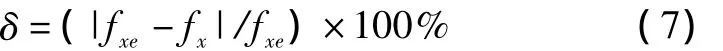

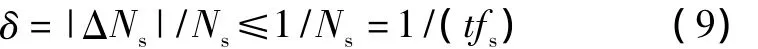

由式(6)可知,若忽略標頻fs的誤差,則等精度測頻可能產生的相對誤差為:

式中:fxe為被測信號頻率的準確值。

在測量中,由于fx計數的啟停時間都是由該信號的上升沿觸發的,在閘門時間t內對fx的計數Nx無誤差(t=NxTx);對 fs的計數 Ns最多相差一個數,即|ΔNs|≤1,Ns用 Ns+ΔNs修正后可得到被測信號頻率準確值fxe的計算公式,即:

將式(6)、式(8)代入式(7),經整理可得:

由式(9)可以得出以下結論:測量頻率的相對誤差與被測信號頻率大小無關,僅與閘門時間和標準信號頻率有關,即實現了整個測試頻段的等精度測量;閘門時間越長,標準頻率越高,測頻的相對誤差就越小[5-6]。選用 FPGA 時鐘頻率為 fs=60 MHz,如閘門時間取 t=1 s,則測試精度 δ≤1.7 ×10-8。

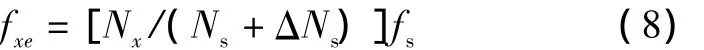

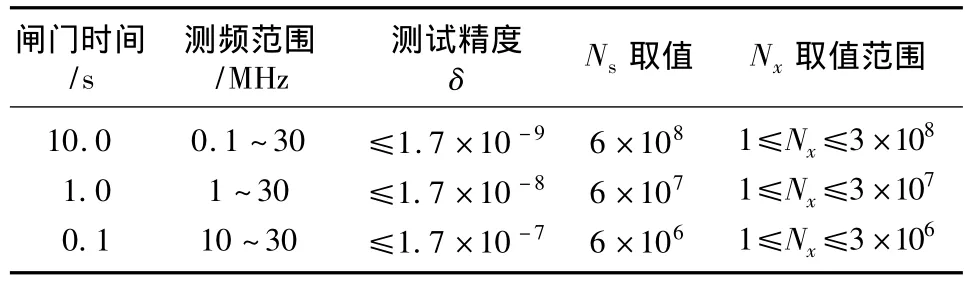

1.2.3 測試精度及相關參數

由式(5)可知:Ns=t/Ts=tfs,Nx=t/Tx=tfx。由于FPGA的fs(60 MHz)是固定的,Ns可根據t的值算出,而Nx隨著被測信號頻率fx而變,但其最小值也應為1(表示對一個完整的被測信號周期進行計數)。此外,根據采樣定理,fx最大值應不大于fs/2,可相應地算出Nx的取值范圍。δ由式(8)計算得出。測試精度與開門時間的關系如表1所示。

表1 測試精度等與閘門時間的關系表Tab.1 Relationship between testing precision and gate time

由此可見,在標準信號頻率不變的前提下,閘門時間越長,Ns、Nx的計數值越大,測試精度越高,但測頻范圍基本不變(僅其能夠測試的下限頻率有所變化)。

1.2.4 計數器選擇

JN338系列傳感器轉矩測量范圍為1~5000 N·m,而轉矩信號頻率在正、反向旋轉滿量程時分別為15 kHz、5 kHz,故轉矩信號頻率低且變化范圍小。

由式(1)可知,f=nZ/60。顯然,n和Z越大,f也就越高。由于JN338轉速測量范圍為10~6000 r/min,其所對應的轉速信號頻率并不高。加上其他類型傳感器,可得出目前傳感器能夠測量的最高轉速為36000 r/min,編碼器齒數Z最大為2700,由此可估算出轉速信號頻率最大值為 1.62 MHz,遠小于 fs。

由此可見轉矩、轉速信號頻率都不高,亦即Nx對應值不大。因此,計數器的位數選擇主要取決于Ns。綜合考慮,計數器取32位即可(232≈4.29×109>6×108)。

2 轉矩轉速測試儀的設計

2.1 通用性設計的實現

由于采用等精度測頻法后測試儀的測頻范圍很大(達30 MHz),能夠覆蓋所有型號的轉矩轉速傳感器的測試范圍。為此,提出“一個主測試機箱配多種傳感器”的設計思想——采用即插即用接口設計。具體來講,就是用戶根據被測對象轉矩、轉速變化范圍選擇型號合適的傳感器,先將其固定在測試軸上,再將其轉矩、轉速輸出引線插頭分別接到對應插槽即可。數字式傳感器(如JN338)可直接接入,而對正弦波輸出類(如JCZ型)則需在接入之前將它們的輸出信號轉換為TTL電平[7]。這樣,一個主測試機箱可配接不同型號的傳感器,實現一機多用,既經濟又方便。

2.2 等精度頻率測量的實現

在快速測量的要求下,要保證較高精度的測頻,必須采用較高頻率的標準信號。單片機受本身時鐘頻率和若干指令運算的限制,測頻速度較慢,而FPGA具有集成度高、工作頻率高和功能強大等特點,能夠滿足高速、高精度測頻要求。通過對FPGA進行設計,即可實現頻率的等精度測量。測頻主系統框圖如圖3所示。

圖3中,A7~A0和B7~B0為兩個計數器的計數值輸出,單片機通過R1、R0數據讀出選通端,讀出4個8位(即32位)計數值,并根據一定算法算出頻率和脈沖寬度。STR為預置門啟動輸入;F/T為測頻/測脈寬選擇;CH為自校/測頻選擇;Fa為自校頻率輸入端;Fs為標準頻率信號輸入端;Fx為經過放大整形后的被測信號輸入端;END為計數結束狀態信號[5]。由于只有一個信號輸入端,為節省成本和簡化設計,采用轉矩、轉速信號分別進行測試的方案,并由單片機程控電子開關來實現。這樣,使用一片FPGA(EPF10K10LC84)即可完成各種測試功能。

圖3 測頻主系統框圖Fig.3 Block diagram of the main system of frequency measurement

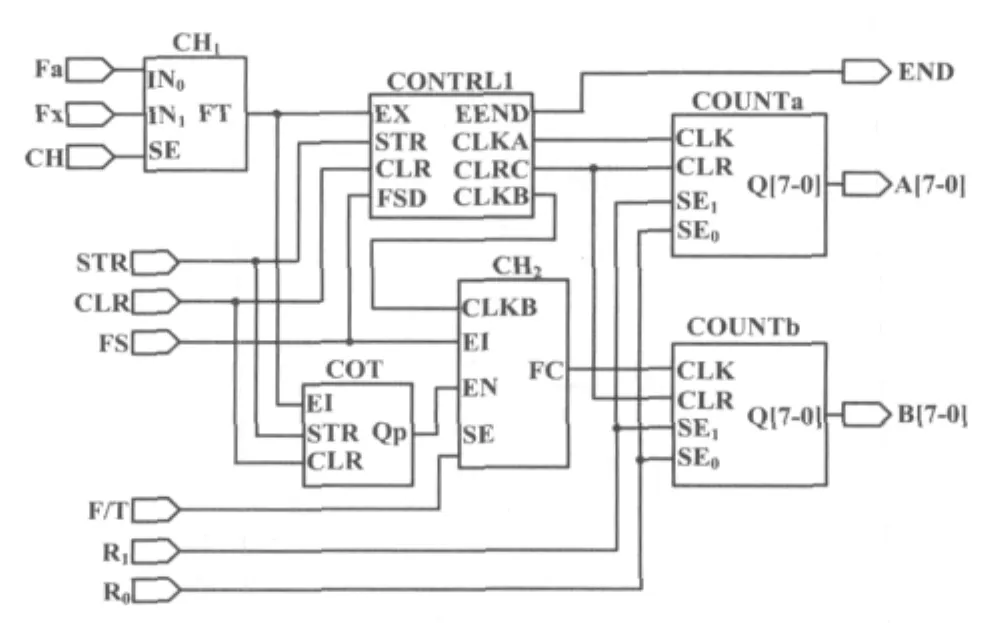

在MAX+plusⅡ軟件環境下進行FPGA設計。首先對各功能模塊進行邏輯描述,然后通過EDA開發平臺,自發地對設計文件完成邏輯編譯、化簡、綜合及優化、布局布線及仿真,最后對FPGA芯片進行編程,以實現系統的設計。系統頂層設計原理圖如圖4所示[6]。

圖4 系統頂層設計原理圖Fig.4 Design principle of the top layer

圖4中,CH1和CH2為選擇器,CH1進行自校/測頻選擇,CH2進行測頻和測脈寬選擇。CONTRL1為控制模塊,控制被測信號Fx和標頻信號Fs的選通及2個32位計數器(COUNTa和COUNTb)的計數。計數器以4個8位二進制數形式輸出。FPGA與SPCE061A單片機的接口比較簡單。A7~A0和B7~B0與單片機A口相連接,其他輸入/輸出端與單片機B口相連接。

2.3 無法實現同相的情況處理

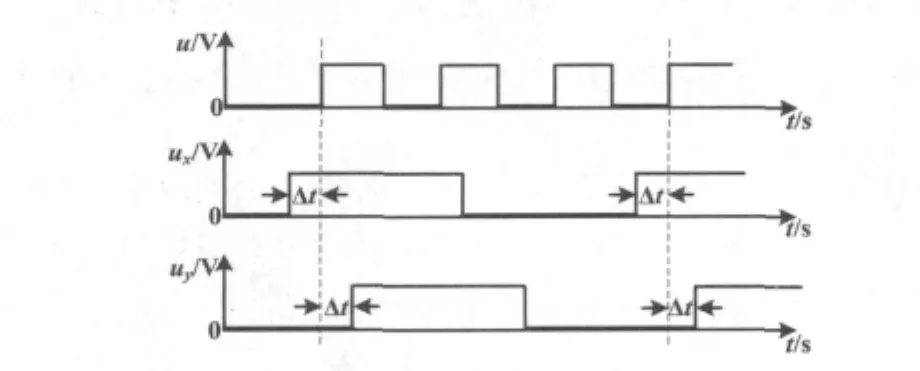

若其中一個被測信號和標準信號的周期是另一個的整數倍,且在進入系統時存在初始相位差,則它們經過一定時間t(預置閘門時間)后相位差仍保持不變,即二者相位可能永遠不重合[8]。圖5即表達了TX=3 Ts時,被測信號u和標準頻率信號fs相位不重合這兩種情況,其中 ux比fs相位超前,而uy比 fs相位滯后。由于無法找到同步點,這類情況顯然不能采用等精度測頻法。故在實際測試時,如經過一段時間t后實際閘門脈沖仍無法形成,即計數器無計數,則認為這兩個信號無法實現同相。單片機判定后會自動改用直接測頻法進行測量并提示用戶。

圖5 被測信號和標準信號相位不重合的情況Fig.5 The situation of phase not coincide for measured signal and standard signal

2.4 單片機選型及設計

單片機選用SPCE061A。該單片機為16位機,數據處理能力較強;具有32 kB Flash和2 kB SRAM以及液晶驅動器,其液晶驅動可直接通過軟件控制來實現,提高了系統的穩定性和抗干擾能力;I/O口數量多(A、B口各16個),不需要擴展即能滿足系統需要;時鐘頻率較高,約40 MHz。鍵盤設有自校/測頻選擇鍵CH、測頻和測脈寬選擇鍵F/T、預置門啟動輸入鍵STR、轉矩測試鍵M、轉速測試鍵n和打印鍵P等功能鍵。

由于需要顯示轉矩、轉速、軸輸出功率值以及閘門時間、測試精度、信號頻率等諸多信息,顯示器選用點陣數為320×240且帶中文字庫的LCD(如HTM320240G)。

3 結束語

本設計采用等精度測頻法,實現了轉矩、轉速信號的等精度測量;采用即插即用接口設計,使測試主機具有更大的使用靈活性,大大增強了測試儀的通用性;利用FPGA工作頻率高、功能強的特點簡化了系統設計,提高了測試精度。經測試表明,本設計具有很好的推廣及應用價值。

[1]楊冠群.以周期滑動擴展的測周法實現等精度的頻率測量[J].電子技術應用,2002,28(2):41 -43.

[2]劉海琴,史智興,程天良,等.基于單片機的電機轉矩測量系統設計[J].微計算機信息,2006,3(2):27 -29.

[3]孟臣,李敏.JN338智能數字式轉矩轉速傳感器及其應用[J].國外電子元器件,2003(11):56-58.

[4]梁龍學.一種新型數字式轉矩轉速測試儀[J].蘭州交通大學學報:自然科學版,2006,25(1):101 -103.

[5]包明,趙明富,郭建華.基于FPGA的高速高精度頻率測量的研究[J].單片機與嵌入式系統應用,2003(1):31-33.

[6]王慧.基于FPGA高速高精度頻率測量系統的實現[J].傳感器世界,2006,12(1):27 -29.

[7]梁毓明,汪鋒鎖,劉志剛.JCZ型轉矩轉速傳感器輸出信號的處理方法[J].計算機測量與控制,2005,13(11):1296 -1298.

[8]劉德亮,王竹林,尉廣軍.基于FPGA高精度頻率測量儀的設計[J].河北工業科技,2010,27(1):29-31.