基于并行完備檢測的高速異步流水線設計

楊延飛 楊銀堂 朱樟明 周 端

①(西安電子科技大學微電子研究所 西安 710071)

②(西安電子科技大學計算機學院 西安 710071)

1 引言

隨著集成電路工藝的發展,傳統的同步電路設計面臨由全局時鐘引起的一系列設計問題[1]。由于異步電路采用握手協議代替時鐘信號,避免了全局時鐘引起的各種問題,因而成為設計者新的選擇[2]。異步流水線是建立高速異步系統的主要技術之一,其中零協議邏輯(NULL Convention Logic, NCL)流水線[3]因延時不敏感特性、設計簡單等特點被廣泛應用設計各種運算電路[4,5]。但是傳統的 NCL流水線每個數據周期內有效數據(DATA)和空(NULL)信號交替輸入,導致流水線吞吐量大幅下降。現有多種技術優化NCL流水線,文獻[6]采用提前完備檢測技術提升吞吐量;文獻[7,8]主要優化流水線靜態功耗;文獻[9]以較大的面積代價提升流水線性能。文獻[10,11]的設計方法則適合應用于延時最長的一級流水線,進而提升整個流水線的吞吐量。

本文提出一種基于串并結合工作方式的 NCL流水線。采用獨特的多閾值半靜態 NCL(Multi-Threshold Semi-static NCL, MTSNCL )閾值門建立異步組合邏輯,以實現流水線級內并行、級間串行的工作方式,有效地提升流水線性能。

2 并行完備NCL流水線設計

2.1 MTSNCL閾值門設計

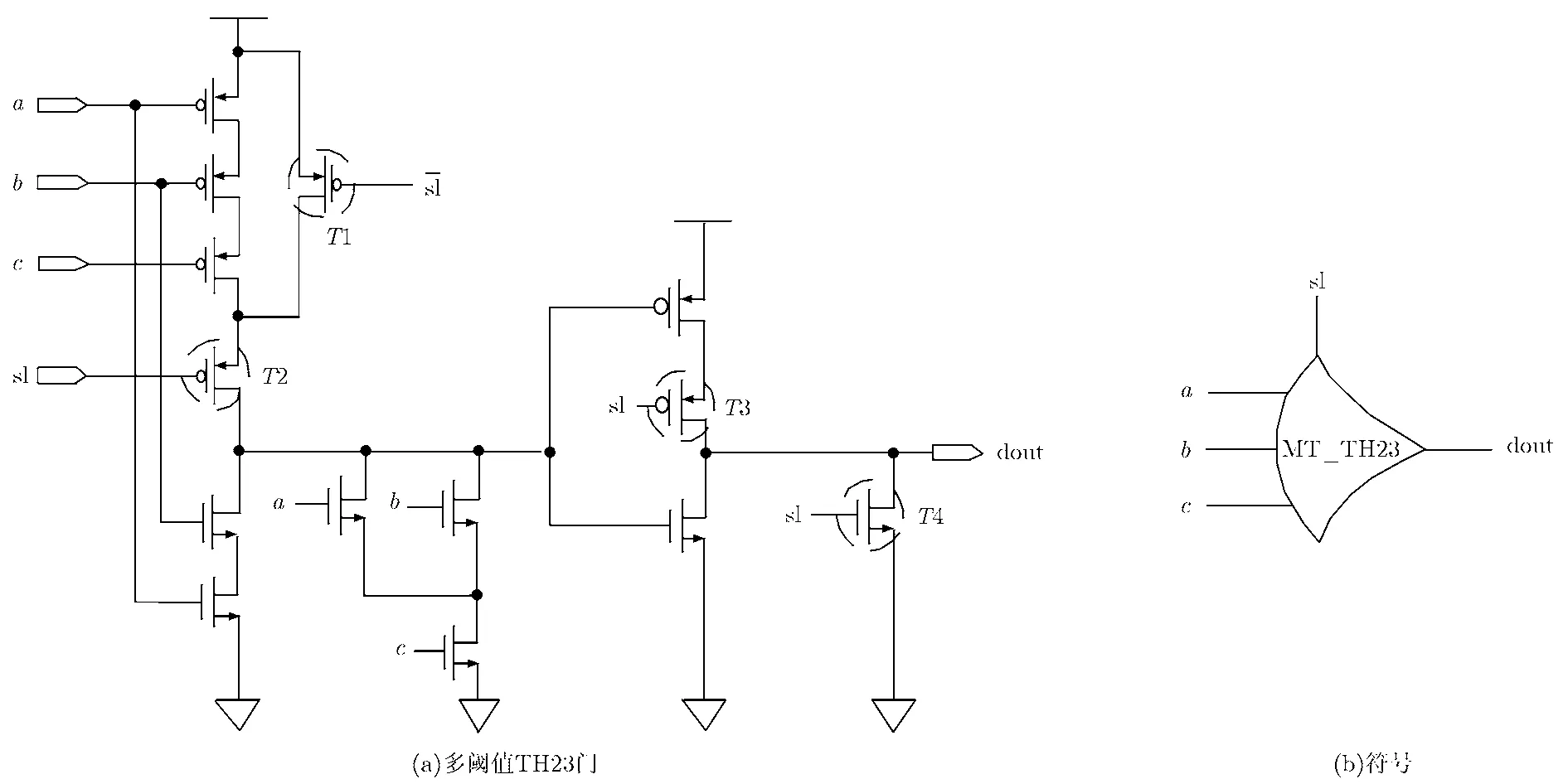

圖1所示為本文提出的MTSNCL閾值門結構,以 TH23門為例。圖中圓形星狀線標注的晶體管為高閾值晶體管,由sl(sleep, 休眠信號)及其反向信號所控制,該信號由流水線內部產生。當sl為0時,T2和T3導通而T1 和T4關斷,執行傳統TH23門的邏輯功能。反之,當sl為1時,T1和T4導通而T2 和T3關斷,閾值門進入休眠模式且輸出dout為 0。此時,閾值門中的上拉鏈和下拉鏈均被高閾值晶體管短路,GND和VDD之間為漏電流很小的高閾值晶體管,有效地減小了閾值門的靜態功耗。由于在休眠模式下,電路中的高閾值晶體管同時具有保持功能。因此圖中閾值門不包含狀態保持模塊也可正常工作。

2.2 并行完備流水線結構

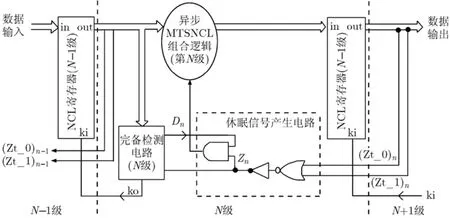

圖2所示為本文提出的NCL流水線,圖中每級流水線由MTSNCL組合邏輯、NCL寄存器、完備檢測及休眠信號產生電路組成。以第N級流水線為例,休眠信號產生電路的輸入信號(Zt_0)n和(Zt_1)n是經過第N級流水線組合邏輯和寄存器的延時最長的一位雙軌數據。當(Zt_0)n和(Zt_1)n中有一位為1時,輸出Zn為1,表示本級組合邏輯輸出的所有數據已經正確存儲;當(Zt_0)n和(Zt_1)n均為0時表示本級組合邏輯和寄存器復位完畢且輸出空。該模塊的另一輸入信號Dn來自本級完備檢測模塊,Dn為 1,表示本級輸入的所有有效數據已正確接收,為0表示本級輸入均為零。由圖2可看出,只有在Dn和Zn均為1時,輸出sl才為1,即本級組合邏輯的復位只有在輸入數據正確接收且輸出數據正確存儲后才會啟動,而只要輸入或輸出復位完畢,組合邏輯就會立刻進入工作狀態。

本文流水線的工作原理為:數據輸入第N級流水線后,完備檢測和數據處理并行進行,sl信號和應答信號 ko的產生依賴于完備檢測和數據處理時間較長者。若完備檢測的時間較長,那么 sl和 ko將在完備檢測完成后產生。反之,若數據處理時間較長,那么sl和ko將在數據被完整存儲后產生,以確保數據的正確處理。當數據處理完畢后,sl為1,進行本級組合邏輯和輸出寄存器的復位,本級輸出為零。同時ko為0,通知前級寄存器數據存儲完成,可輸出NULL信號。

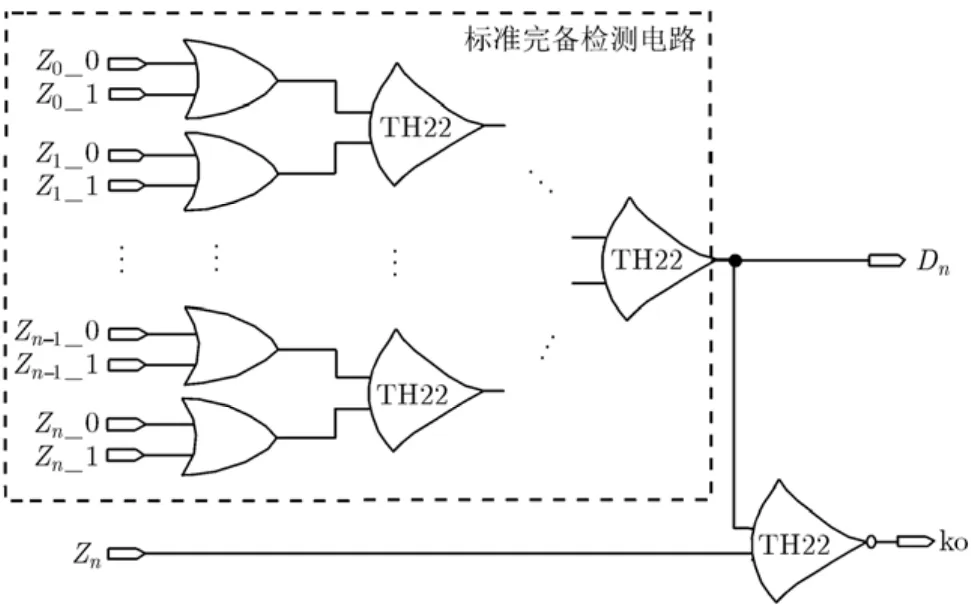

圖3所示為第N級流水線的完備檢測電路,由標準完備檢測電路和反向TH22門組成。標準完備檢測電路在檢測本級輸入正確性的同時保證前級輸出的完備性。只有當所有的輸入數據都正確接收后,輸出Dn才為1。輸入Zn由休眠信號產生電路輸出,Zn為1時,表示本級寄存器已完成數據的存儲。本級應答信號ko由反向TH22門輸出。當Zn和Dn均為1時,本級流水線完成數據處理和存儲,此時 ko為0,通知前級可以開始空周期的處理。當Zn和Dn均為0時,ko為1,本級完成復位,并通知前級可以接收新的有效數據。與標準流水線不同的是,本文流水線中本級輸出數據的完備性是由下一級完備檢測電路保證的。

2.3 流水線分析

圖1 多閾值TH23邏輯門

圖2 多閾值并行完備流水線

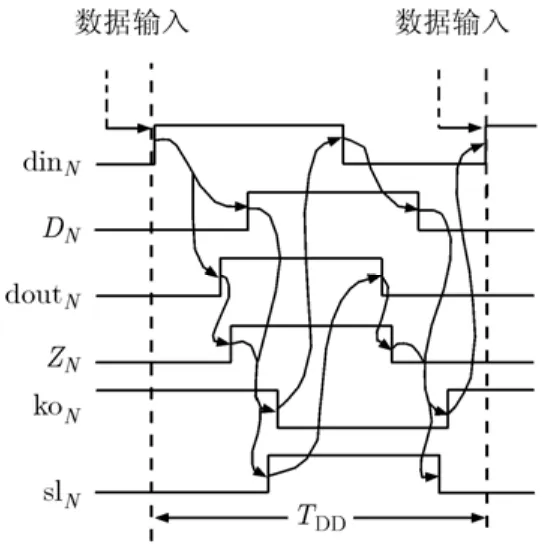

圖4所示為本文流水線的握手時序圖,以第N級為例。圖中dinN和doutN分別表示第N級流水線的輸入和輸出數據。初始化后應答信號 koN為高電平,等待有效數據的輸入。當數據輸入后,完備檢測和組合邏輯運算并行進行,而slN必須在數據計算完成并有效存儲,同時本級完備檢測結束后才輸出為高電平。如圖中所示,在DN和ZN均為高電平后才引起slN有效,電路進入低功耗的空狀態。由時序圖中可看出,組合邏輯的復位是由slN控制,而電路進入空周期則是由應答信號koN引起的。

數據到數據周期時間(DATA-to-DATA cycle time)TDD是表征NCL流水線性能的一個重要參數,

圖3 完備檢測電路(第N級)

圖4 本文流水線握手時序圖(第N級)

定義為每級流水線從當前有效數據輸入到下一次有效數據輸入的時間。由于標準NCL流水線中信號總是依次經過組合邏輯、存儲單元和完備檢測。假設每級流水線組合邏輯和完備檢測時間相同,則其周期時間為

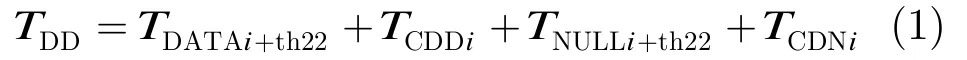

式(1)中TDATAi+th22和TNULLi+th22分別表示 DATA和NULL信號經過第i級組合邏輯和寄存器的時間,TCDDi和TCDNi分別為DATA和NULL信號經過第i級完備檢測電路的時間。相比較于標準流水線的串行工作方式,本文流水線中信號的處理和存儲與信號的完備檢測是并行進行的。若采用相同的參數表述,由圖4可知本文提出的流水線周期時間為

式(2)中所相加的時間項個數少于式(1),表明本文設計的流水線在傳輸數據時不再依次串行通過每個功能塊,每級流水線內采用并行工作方式,提升了吞吐量。

3 仿真結果和性能分析

3.1 流水線功能驗證

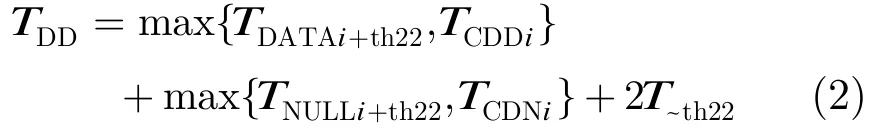

基于 SMIC 0.18 μm 標準 CMOS工藝,采用Cadence Spectre對本文流水線仿真驗證,電源電壓為1.8 V。流水線組合邏輯使用一位NCL全加器,級數為4級,圖5所示為部分仿真波形。圖中Zt0_0和Zt0_1為信號經過第1級流水線組合邏輯和寄存器延時最長的一位雙軌輸出,Z0_0和Z0_1為流水線最終輸出的首位雙軌數據。Z1為Zt0_0和Zt0_1兩信號或操作后的輸出,D1則為第1級流水線完備檢測模塊中標準完備檢測電路的輸出。初始化后應答信號 ko1為 1,請求輸入數據。數據進入組合邏輯的同時開始完備檢測,D1為1時表示數據正確輸入。當Z1為1時表示首級流水線計算并存儲完畢,此時sl1為1,開始本級組合邏輯和寄存器的復位。在D1和Z1均為1后ko1為0,通知前級可輸入NULL信號。由波形圖可看出,本文流水線信號的處理、存儲與信號的完備檢測是并行進行的。

圖5 部分仿真波形圖(4級)

3.2 流水線性能比較分析

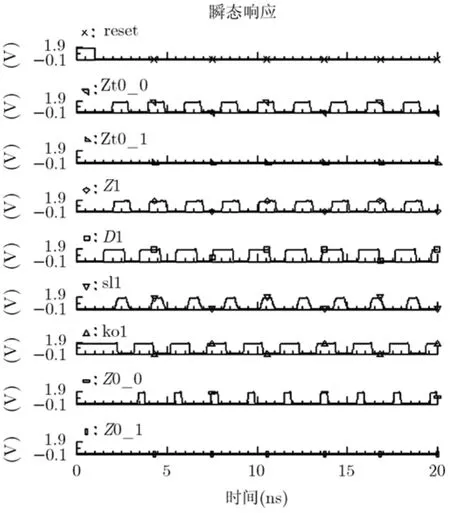

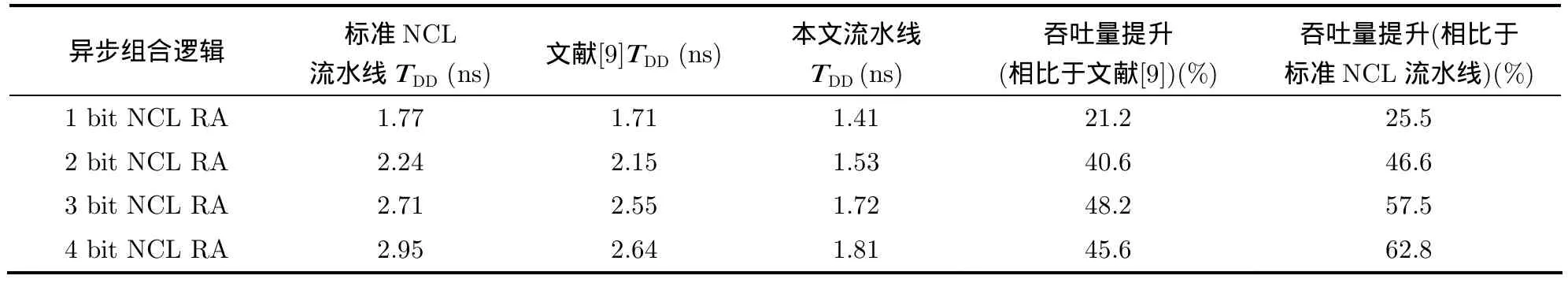

基于相同的測試平臺,分別對文獻[12]中的標準流水線、文獻[9]提出的流水線和本文的流水線進行了仿真比較。測試時采用 NCL串行進位全加器(Ripple full-Adder, RA)作為組合邏輯。表1給出了基于不同位寬RA下3種流水線的周期及吞吐量。由于異步電路的性能取決于平均性能[10],測試時各流水線的TDD為不同輸入向量下的平均值。由表 1可看出,隨著RA位數增加,本文流水線吞吐量提升率越高。由于RA位數增加,每級流水線的組合邏輯延時和完備檢測時間均增加。對比2.3節式(1)和式(2)可知,隨著延時的增加,本文提出的流水線吞吐量提升越高。當組合邏輯為4位RA時,相比較于文獻[9]和標準流水線,吞吐量分別提升了45.6% 和62.8%。

圖6所示為不同位寬RA下3種流水線的靜態功耗和面積比較,圖 6(a)為不同級數下流水線的靜態功耗,圖6(b)為相應的面積。由圖6可看出,文獻[9]的流水線靜態功耗最小,但面積最大。由于該流水線采用靜態實現方式,相比于半靜態NCL門,靜態NCL門具有更小的靜態功耗,但是設計復雜且面積較大。因此靜態功耗雖然顯著減小,卻需要更大的面積和動態功耗。而本文流水線采用MTSNCL邏輯,降低靜態功耗的同時面積和動態功耗代價較小。由圖中可看出,當4級流水線的組合邏輯為 4位RA時,相比較于標準NCL流水線,本文流水線的靜態功耗減小了40.5%,而面積僅增加了9.3%。

圖6 流水線靜態功耗和面積比較

表1 流水線性能比較

4 結束語

本文提出了一種并行完備異步流水線。首先給出流水線所需的NCL閾值門,采用新閾值門建立異步組合邏輯,使每級流水線的數據處理和完備檢測并行進行,實現流水線級內并行、級間串行的工作方式。這種串并結合的工作方式在有效縮短流水線周期,提升吞吐量的同時,降低了流水線空周期時的靜態功耗。實驗比較結果顯示,本文流水線具有周期短,吞吐量高,靜態功耗低的特點,適用于納米工藝下高速異步NCL流水線系統設計。

[1]Rajaram A and Pan D Z. Robust chip-level clock tree synthesis[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2011, 30(6): 877-890.

[2]彭瑤, 周端, 楊銀堂, 等. 一種高速延時無關片上異步轉同步通信接口的設計[J]. 電子與信息學報, 2011, 33(4): 938-944.

Peng Y, Zhou D, Yang Y T,et al..A novel high-speed delay-independent asynchronous to synchronous communication interface[J].Journal of Electronics&Information Technology, 2011, 33(4): 938-944.

[3]Fant K M and Brandt S A. NULL convention logic: a complete and consistent logic for asynchronous digital circuit synthesis[C]. Proceedings of International Conference on Application Specific Systems, Architectures and Processors,Chicago, IL, 1996: 261-273.

[4]Sankar R, Kadiyala V, Bonam R,et al.. Implementation of static and semi-static versions of a bit-wise pipelined dual-rail NCL 2s complement multiplier[C]. 2007 IEEE Region 5 Technical Conference, Fayetteville, Arkansas, 2007: 59-64.

[5]Mallepalli S R, Kakarla S, Burugapalli S,et al..Implementation of static and semi-static versions of a 24+8×8 quad-rail NULL convention multiply and accumulate Unit[C]. 2007 IEEE Region 5 Technical Conference, Fayetteville, Arkansas, 2007: 53-58.

[6]Smith S C. Speedup of self-timed digital systems using early completion[C]. IEEE Computer Society Annual Symposium on VLSI, Pittsburgh, PA, 2002: 98-104.

[7]Bailey A D, Jia Di, Smith S C,et al.. Ultra-low power delay-insensitive circuit design[C]. The 51st Midwest Symposium on Circuits and Systems, Knoxville, TN, 2008:503-506.

[8]Bailey A D, Al Zahrani A, Fu G Y,et al.. Multi-threshold asynchronous circuit design for ultra-low power[J].Journal of Low Power Electronics,2008, 4(3): 337-348.

[9]Al Zahrani A, Bailey A D, Fu G Y,et al.. Glitch-free design for multi-threshold CMOS NCL circuits[C]. Proceedings of the ACM Great Lakes Symposium on VLSI, Boston Area,MA, 2009: 215-220.

[10]Smith S C. Speedup of NULL convention digital circuits using NULL cycle reduction[J].Journal of System Architecture, 2006, 52(7): 411-422.

[11]Guan X G, Zhou D, and Yang Y T. Optimization design of a full asynchronous pipeline circuit based on null convention logic[J].Journal of Semiconductors, 2009, 30(7): 075010-6.

[12]Kakarla S and Al Assadi W K. Testing of asynchronous NULL conventional logic (NCL) circuits[C]. 2008 IEEE Region 5 Conference, Kansas City, MO, 2008: 1-6.