基于Xilinx ISE平臺的FPGA電路設計

于東陽,蘇 彬

(中國電子科技集團公司第四十七研究所,沈陽110032)

1 引言

如今社會是數字化的社會,是數字集成電路廣泛應用的社會。數字集成電路本身在不斷進步,傳統的可編程邏輯器件正在向大容量、高性能、低成本的方向發展。因此出現了現場可編程邏輯器件(FPLD),其中應用最廣泛的當屬現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。美國Xilinx公司是全球最大的可編程邏輯器件廠商,首創了現場可編程邏輯陣列這一技術,其產品在國內各個行業得到了廣泛應用,同時該公司的ISE開發軟件為用戶提供了一個易于操作的軟件開發平臺,可以很方便地開發出基于該公司的CPLD/FPGA產品的數字電路。

2 VHDL語言簡介

VHDL是一種硬件描述語言,主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL的語言形式和描述風格與句法十分類似于一般的計算機高級語言。

3 ISE簡介及FPGA設計流程

Foundation Series ISE(簡稱ISE)是由著名的可編程器件開發廠商Xilinx公司提供的集成化開發平臺。ISE可以完成FPGA開發的全部流程,包括設計輸入、仿真、綜合、布局布線、生成BIT流文件、配置以及在線調試等,功能非常強大,并且具有界面良好、操作簡單的特點,再加上Xilinx的FPGA芯片占有很大的市場,使得ISE成為了非常通用的FPGA工具軟件。

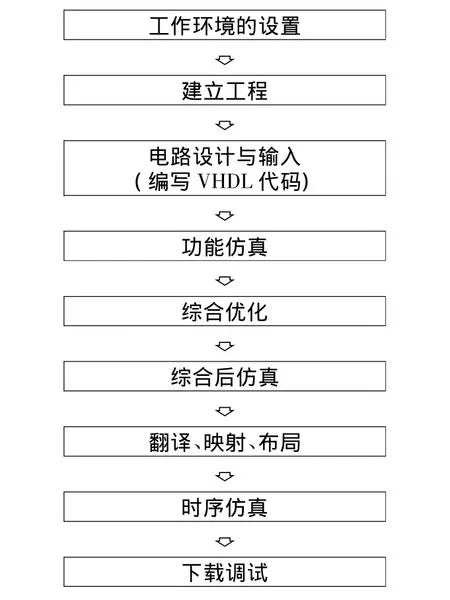

如圖1所示。在ISE集成開發環境中,一個完整的FPGA設計流程包括工作環境設置、工程建立、電路設計(VHDL代碼編寫)、功能仿真、綜合優化、綜合后仿真、翻譯、映射、布局、時序仿真、下載調試等主要步驟。

首先要進行整個工作環境的設置,通過環境設置可以使整個設計過程更加適應自己的習慣,提高工作效率。然后要建立一個工程項目,把整個設計放到工程里統一管理。電路的設計輸入是工程設計的第一步,常用硬件描述語言(HDL),將電路需要實現的功能及輸入輸出接口等用VHDL編寫出來。功能仿真是數字系統設計中不可缺少的一個環節,通過仿真可以對整個設計的功能和時序進行驗證。電路設計完成后,可以用ISE中的Test Bench Waveform工具為當前升級添加測試激勵,然后在ISE中啟動ModelSim仿真軟件對設計進行功能仿真。當功能仿真沒有問題后,下一步就是要進行綜合優化。綜合優化將HDL或原理圖設計輸入翻譯成由與、或、非門、RAM、寄存器等基本邏輯單元組成的邏輯連接,即網表,并根據約束文件優化所生成的網表。當綜合完成后,需要檢驗和原設計是否一致,要做綜合后仿真。綜合后仿真的結果會產生相應的邏輯網表,FPGA根據邏輯網表的內容進行翻譯、映射、布局來實現整個設計的邏輯功能。布局布線后是時序仿真,這種仿真將布局布線的時延文件反標到設計中,使仿真既包含門延時,又包含線延時信息,從而更加全面、準確的反映芯片的實際工作情況。最后就需要把生成的配置文件寫入芯片中進行測試。

4 設計實例

下面以Xilinx公司Spartan IIE系列的FPGA芯片為例來實現一個簡單的電路設計,基本功能是實現一個3-8譯碼器。

圖1 FPGA設計流程圖

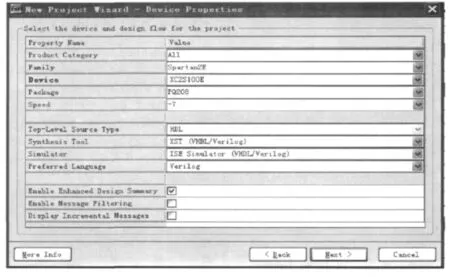

(1)新建選擇的芯片

在ISE的工具欄里選擇新建工程,新建一個項目,通過選擇項目芯片的屬性來建立一個工程,如圖2所示。

圖2 新建項目屬性窗口

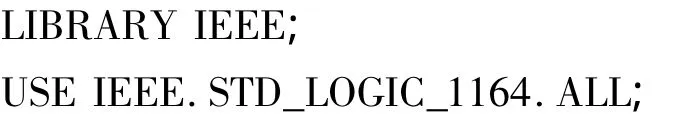

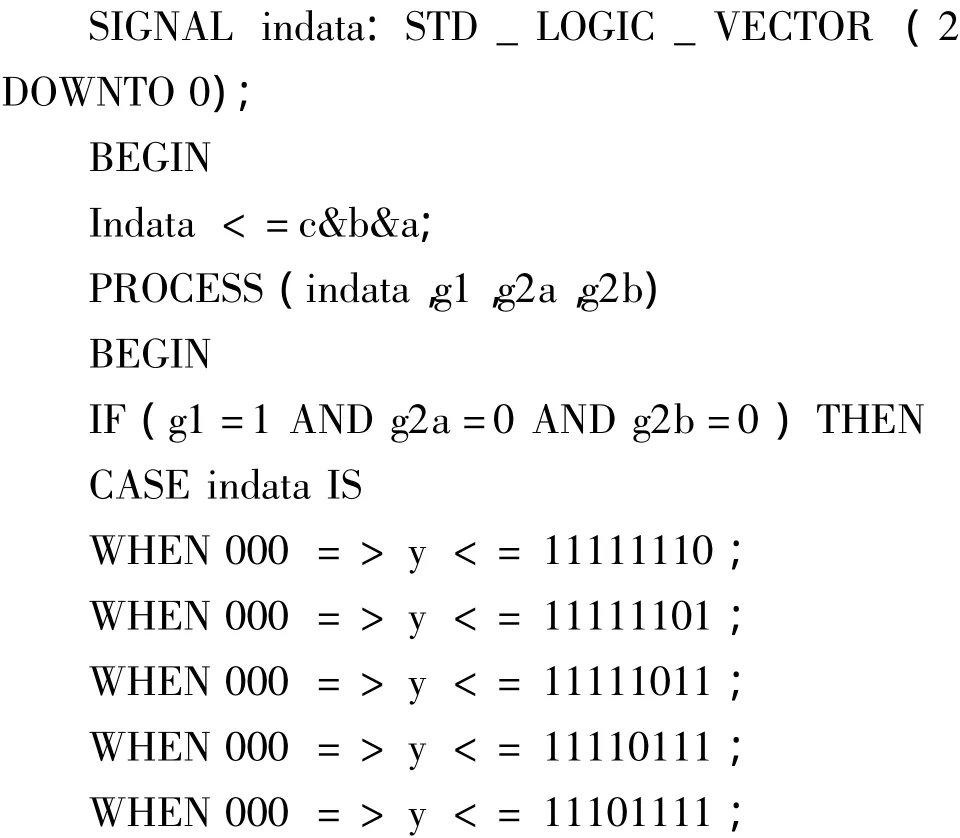

(2)編寫VHDL代碼

在項目中新建一個設計輸入源文件,輸入如下源程序:

(3)功能仿真

用ModelSim進行仿真,觀察仿真時序波形與設計是否一致,如圖3所示。

圖3 ModelSim仿真圖形

(4)綜合優化

執行綜合優化功能后,如正常則顯示為綠色,可進行下步操作。

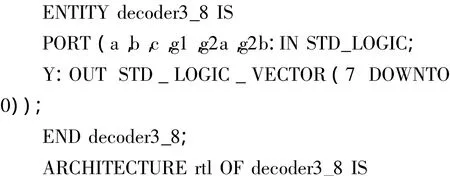

(5)實現

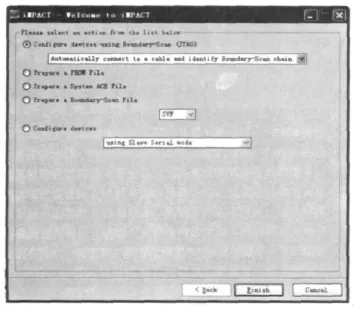

將FPGA進行管腳約束,并通過翻譯、映射和布局布線后,最終生成FPGA配置所需要的BIT流文件,并通過測試工具IMPACT加載到FPGA芯片中運行,如圖4所示。

圖4 IMPACT進行加載窗口

(6)檢驗

通過觀察編譯完成后的器件,來檢驗是否與設計一致,如有錯誤,則返回第一步重新按流程設計。

5 結束語

FPGA被廣泛地應用在目前的數字電路系統設計中,掌握FPGA的開發方法是當前電子工程師必須的一項基本技能。本文通過實例,詳細介紹了在ISE集成開發環境下,用FPGA進行數字電路設計的具體過程和方法。案例表明ISE有著強大的功能和豐富的工具集,通過它可以完成整個FPGA的開發過程,而且ISE的界面簡潔,易學易用,有可視化編程技術,還具有強大的輔助設計功能,可以大大減少設計者的工作量,提高設計的效率和質量。

[1] 王金明,楊吉斌.數字系統設計與Verilog HDL[M].北京:電子工業出版社,2002

[2] 田耕,徐文波.Xilinx FPGA開發實用教程[M].北京:清華大學出版社,2008.

[3] 薛小剛,葛毅.Xilinx ISE9.x FPGA/CPLD設計指南[M].北京:人民郵電出版社,2007.

[4] 王誠,薛小剛,鐘信潮.FPGA/CPLD設計工具——Xilinx ISE使用詳解[M].北京:人民郵電出版社,2005.