IC設計中的ESD保護技術探討

曹燕杰,王 勇,朱 琪,華夢琪,吳海宏,張 勇

(中科芯集成電路股份有限公司,江蘇 無錫 214072)

1 ESD在IC設計中的重要性

為了避免集成電路在生產過程中被靜電放電所損傷,在集成電路內皆有制作靜電放電保護電路。靜電放電保護電路是集成電路上專門用來做靜電放電保護的特殊電路,靜電放電保護電路提供了ESD電流路徑,以免ESD放電時電流流入IC內部而造成電路損傷。

靜電放電(Electrostatic Discharge,ESD)是造成大多數電子器件或電子系統受到過度電性應力(Electrical Overstress,EOS)破壞的主要因素。這種破壞會導致半導體器件或電子系統形成一種永久性的毀壞,因而影響集成電路(Integrated Circuits)的電路功能,使得電子產品工作不正常。 而靜電放電破壞的產生,多是由于人為因素所形成,但又很難避免。電子器件或系統在制造、生產、組裝、測試、存放、搬運等的過程中,靜電會累積在人體、儀器、儲放設備等之中,甚至在電子器件本身也會累積靜電,而人們在不知情的情況下使這些物體相互接觸,因而形成了一條放電路徑,使得電子器件或系統遭到靜電放電的損害。

如何才能避免靜電放電的危害呢?除了加強工作場所對靜電累積的控制之外,必須在電子產品中加入具有防患靜電放電破壞的裝置。首先必需考慮這額外裝置的效能,如何處理才能達到有效保護的功用。同時裝置應放在何處,以及在工業上的大量應用中如何才是最省成本的設計方式都是應一一處理及考慮的問題。

在保護裝置的設計上,從加強集成電路本身對靜電放電的耐受能力上著手,可以解決芯片包裝后組裝、測試、存放、搬運等所遭遇到大多數靜電放電的問題。

靜電放電保護電路(ESD protection circuits)是集成電路上專門用來做靜電放電保護之用,此靜電放電保護電路提供了ESD電流路徑,以免ESD放電時靜電電流流入IC內部而造成損傷。人體放電模式(HBM)與機器放電模式(MM)的ESD來自外界,所以ESD保護電路都是做在PAD(芯片壓焊點)的旁邊。在輸出PAD,其輸出級大尺寸的PMOS及NMOS器件本身便可當作ESD保護器件來用,但是其布局方式必須遵守設計規則中有關ESD布局方面的規定。在輸入PAD,因CMOS集成電路的輸入PAD一般都是連接到MOS器件的柵極(gate),柵氧化層容易被ESD所打穿,因此在輸入PAD的旁邊會做一組ESD保護電路來保護輸入級的器件。在VDDpad與VSSpad的旁邊也要做ESD保護電路,因為VDD與VSS腳之間也可能遭受ESD的放電。

2 IC設計中對ESD設計的要求

IC設計對ESD設計的要求可以分成4類:健壯性、有效性、速度、透明性。好的ESD設計必須滿足這4個要求。

(1)健壯性指的是ESD保護電路能夠承受的ESD電流的能力;

(2)有效性是指ESD保護電路能把電壓限制在安全值以下,不使被保護電路失效;

(3)滿足了健壯性和有效性的ESD保護電路,必須有足夠快的速度把ESD降低到安全水平;

(4)透明性是最后一個優秀的ESD保護電路的指標,要求ESD保護不影響I/O電路和芯片的正常工作,這包含I/O的參數和電路的規范。例如:

(a)電容:ESD保護電路不應該有太大的電容,違背I/O信號的負載限制。

(b)漏電:在I/O,高電平或低電平時沒有超規范的漏電,也包含電源-地之間沒有大的漏電。

(c)上電順序:ESD保護電路不會影響正常的上電順序。

(d)熱插拔:當有要求時也不能違背。

(e)過壓狀況:在混合電壓端口,如3.3V/5V,ESD保護電路表現正常。

(f)Latchup:不能造成芯片的latchup。

透明性對高頻端口和低漏電電源尤其重要。

3 常見的ESD設計方法或注意點

3.1 ESD 保護策略介紹

在靜電保護的各種手段中,最主要也是最有效的方式還是在集成電路內部電路結構設計時加入靜電保護電路結構。靜電保護結構的作用就是在靜電電壓產生時能將其安全地釋放,防止其被導入器件內部工作電路。實際上,設計有效的靜電保護結構是一個長期的、不斷發展的過程。一個好的、具有較強抗靜電能力的保護結構,往往要進行很多次重復的改進才能完成。而且,原有的一些比較成功的保護結構,隨著器件尺寸的不斷減小以及工藝技術的改進,其可靠性和有效性會大打折扣,因此需要不斷改進甚至重新設計新結構。

3.2 ESD保護器件介紹

在ESD沖擊發生時,ESD保護電路必須保證及時地釋放ESD能量,并且保護電路本身必須能夠承受大電流。所以ESD保護電路必須要具有較低的擊穿電壓(breakdown voltage)或者較快的觸發速度,形成低阻通路,并均勻地釋放ESD能量。因此這就對ESD器件在大電流、高電壓情況下的工作機制提出了一定的要求。這些器件的工作機制與它們在正常工作狀態下的機制有很大不同。在這里簡要敘述了常用ESD保護結構構成的器件在ESD狀態下的特性和工作機制。這些器件包括半導體電阻、傳統的二極管(正反向)、厚氧化層(Field-oxide)器件、NMOS管。

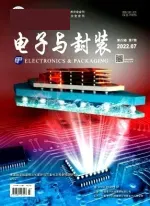

圖1 各種ESD保護器件的I-V特性

從圖1器件的I-V特性可知,各種ESD保護器件在正向偏壓及反向偏壓之下,其工作電壓是不同的,例如二極管在正偏的工作電壓約在0.8V ~ 1.2V左右,但是該二極管器件在反偏的工作電壓約在-13V~-15V左右。因此,當相同大小的ESD放電電流流經該二極管器件時,在反偏情形下所產生的熱量遠大于該二極管在正偏情形下的熱量,也就是說在器件尺寸大小相同的前提之下,二極管器件在正偏所能承受的ESD電壓遠大于在反偏所能承受的ESD電壓。因此,如何設計一個具有高ESD承受能力但只占用小布局面積的ESD保護電路必須考慮器件在不同偏壓之下的特性。

至于MOS器件或厚氧化層(Field-oxide)器件的ESD承受能力,跟該器件的二次擊穿電流(It2,secondary- breakdown current)有關。當ESD放電電流大于該器件的It2時,該器件便會造成不可回復的損傷。

3.2.1 電阻

電阻往往起到限流、分壓等作用。MOS工藝一般采用多晶硅電阻、P+或N+擴散電阻、P阱或N阱擴散電阻來實現。在ESD保護結構中也要用到電阻,起的作用主要也是限流和分壓。但是ESD的釋放是短時間高能量的釋放,這種情況下這些電阻都會表現出不同的特性。

多晶硅電阻并不適用于ESD保護結構。因為ESD沖擊發生時,ESD保護結構要釋放ESD的能量,而多晶硅電阻與襯底間有二氧化硅隔離,使多晶硅電阻在ESD沖擊發生時散熱不良,主要失效模式是熔斷開路而破壞電路性能,因此不推薦使用。而N+、P+、N阱、P阱等擴散電阻在ESD沖擊發生時會進入非線性區。這是因為,擴散電阻是載流子在電場E作用下的定向漂移運動形成的:Vd=uE,其中Vd是載流子的漂移速率。而ESD具有相當高的電壓,當ESD沖擊發生時,載流子的速率將達到飽和速率Vs;再增大電壓將只會增大電場,而不會增大電流密度,器件進入飽和狀態。在擴散電阻中,若電流到達一定程度(數量)時電流會被限制,若繼續增大電壓,載流子反復撞擊產生大量空穴電流,當空穴電流足夠影響總電流時,會出現負阻現象;這時電壓開始下降,只要較低的電壓就可以維持較大的電流。在ESD可靠性研究中擴散電阻的高電流行為已經被大量研究;但需注意在更高的電流等級下電阻最終發生永久熱失效,因此設計時必須考慮到其能量釋放的密度問題。

3.2.2 二極管(diode)

二極管結構作為ESD保護器件被廣泛使用很長時間。二極管擁有良好的電流導通特性(50mA/μm)和很低的導通阻抗。因此,在1.5μm工藝以下ESD保護器件主要使用MOS管和場管,利用它們寄生的npn管的snapback特性。

二極管,在Vdd-Vss間有足夠好的ESD保護電路,能夠利用其優秀的正偏特性正常工作,而不需要工作在反向擊穿。另外,二極管不像其他保護器件如MOS管、SCR結構有latch-up風險。

3.2.3 厚氧化層(field oxide oxide)器件

場管作為ESD保護器件主要使用在特征尺寸從1μm到3μm的工藝里。實際上,場管主要以寄生的橫向npn工作。在大尺寸工藝中,場管的ESD性能好是因為寄生npn管工作區域離硅表面更遠,產生的熱量遠離硅表面。

就ESD而言,場管的主要參數有:溝道長度(L)、漏端的孔到擴散區邊緣的距離(DS)、溝道寬度(W)。關于DS這個參數,增大DS,一方面增加了漏端的串聯電阻,另一方面可以增大寄生npn管的有效導通區域,有利于提高ESD水平。但如果DS過大,可能會造成接觸孔和襯底的穿刺現象(contact spiking)。常見的解決辦法是在接觸孔下放n-well,這樣擊穿就不會發生在接觸孔的下面了。

對于突變結工藝,漏端的孔到擴散區邊緣的距離(DS)非常關鍵,但當輕摻雜漏(LDD)結的引入,增大DS的效果就變差了。當引入硅化物(silicide)工藝時,增大DS的效果就完全沒有了。原因是硅化物大大減小了接觸孔到溝道的電阻。最有效的解決辦法是在接觸孔到擴散區邊緣之間阻擋硅化物的形成。

3.2.4 NMOS管

在深亞微米工藝中,NMOS管有更好的ESD性能。研究表明,0.1μm工藝里的NMOS管的ESD能力比1μm工藝的好。這主要由于隨著尺寸的縮小,擊穿電壓和snapback維持電壓減小,產生的功耗降低。

NMOS管的主要設計參數有:溝道長度(L),漏端的接觸孔到柵的距離(DCG),溝道寬度(W)。對于1μm以上的工藝,一個典型的設計參數為:晶體管的W=200μm,L約大于最小溝道長度,DCG =6μm。關于多個MOS管并聯設計的晶體管,ESD性能并不能隨著并聯管子個數的增加而正比例增大,除非使用其他的技術,比如柵耦合、襯底觸發技術。單個MOS管的溝道寬度也必須進行優化,作為經驗推薦單個管子的溝道寬度為40μm~80μm。

3.3 ESD保護電路介紹

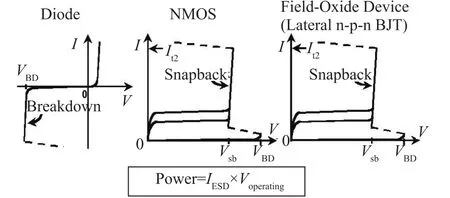

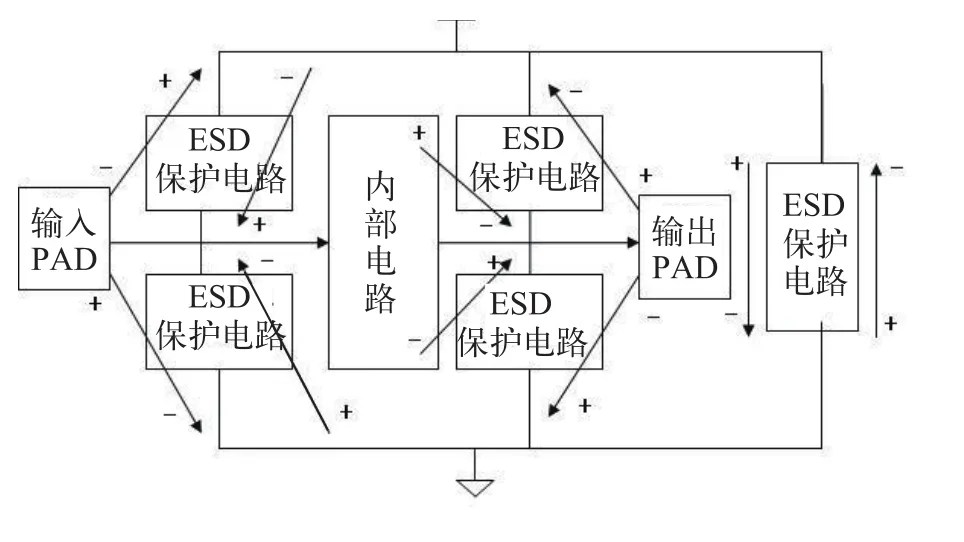

ESD保護電路的布局必須全方位考慮到ESD測試的各種組合,因為整顆IC的所有腳中,在各種測試模式下最低的ESD耐壓值為該顆IC的ESD failure threshold。因此,一個全芯片ESD保護電路的布局要如圖2所示。Input pad與Output pad要具有保護PS、NS、PD、ND四種模式的靜電放電,靜電放電模型如圖3所示。另外,VDD到VSS也要有ESD保護電路,靜電放電模型如圖4所示。

圖2 全方位靜電放電保護電路的安排

圖3 I/O Pin的靜電放電測試組合

(1)PS-mode:VSS腳接地,正的ESD電壓出現在該I/O腳對VSS腳放電,此時VDD與其他腳皆浮接;

(2)NS-mode:VSS腳接地,負的ESD電壓出現在該I/O腳對VSS腳放電,此時VDD與其他腳皆浮接;

(3)PD-mode:VDD腳接地,正的ESD電壓出現在該I/O腳對VDD腳放電,此時VSS與其他腳皆浮接;

(4)ND-mode:VDD腳接地,負的ESD電壓出現在該I/O腳對VDD腳放電,此時VDD與其他腳浮接。

圖4 VDD to VSS的靜電放電測試組合

(1)Positive-mode:正的ESD電壓出現在VDD腳, 此時VSS腳接地,但所有I/O 腳皆浮接;

(2)Negative-mode:負的ESD電壓出現在VDD腳,此時VSS腳接地,但所有I/O 腳皆浮接。

因為ESD保護電路是為了保護ESD而加入的,在集成電路正常操作情形下ESD保護電路不工作,因此在加入ESD保護電路于集成電路中時必須要考慮到之前所列舉的注意事項。其中,在設計上除了要能符合集成電路所要求的ESD保護能力之外,也要盡可能降低因為加上該ESD保護電路而增加的成本,例如布局面積的增大或者制造工藝的增加等。

另外,在一些ESD保護電路中,尤其是在Input pad,其ESD保護電路只安排在Input pad與VSS之間,Input pad到VDD之間沒有安排ESD保護電路。當ND模式的ESD放電發生時,負的ESD電壓會先經由Input到VSS之間的ESD保護電路跑到VSS電源在線,沿著VSS電源線流向VDD與VSS之間的ESD保護電路,再經由此VDD與VSS之間的ESD保護電路轉到VDD電源在線,最后由VDDpad流出此IC。

ND模式的靜電放電是藉由Input到VSS以及VDD與VSS之間的ESD保護電路來旁通ESD電流。有些加了Input到VSS之間的ESD保護電路,卻忘了加上VDD與VSS之間的ESD保護電路,這時在ND模式ESD測試組合之下,集成電路的內部電路常常先被ESD放電電流所損壞,但是在Input pad上的ESD保護電路卻毫發未傷,這種內部電路損傷無法自Input pad的I-V變化觀測得到,必須再經由IC功能測試分析才會發現。隨著芯片的尺寸越做越大,環繞整個芯片的VDD與VSS電源線也越拉越長,寄生的電容電阻效應便會顯現出來,當IC的布局造成電源線的雜散電容電阻效應,這些雜散電阻電容會延遲ESD電流經由VDD與VSS之間的ESD保護電路旁通而過。這時,來不及放電的ESD電流便會借著電源線的連接而進入到IC內部電路中,IC內部電路在布局上一般都以最小尺寸來做,也不會考慮ESD的布局方式,因此其更易被此種ESD電流所損傷。因此造成異常的ESD損傷現象,也就是在I/O pad上的ESD保護電路完好,但內部電路已失效,這種內部損傷是無法從單一輸入腳或輸出腳的I-V變化看出來的。

因此,當芯片尺寸較大時,必須要在Input pad與VDD之間也提供ESD保護電路來直接旁通ESD電流,而不能只借由VDD與VSS之間的ESD保護電路來間接放電。

4 深亞微米工藝中的ESD設計方法

在進入深亞微米的CMOS工藝中,為使MOS管能符合各式各樣的應用,器件中的雜質分布及結深都有了許多改變,然而這些工藝參數都會影響到器件對靜電放電的防護耐受度。在半導體代工盛行的今天,一旦工藝發展穩定后,為了在集成電路中設計出有競爭力的靜電放電保護電路,設計工程師就僅能從選擇適當器件以及改變其版圖幾何結構上來做變化,以實現具有最佳靜電放電防護能力的防護裝置。在作為靜電放電防護的器件中,以MOS晶體管的導通特性用做靜電放電防護最適合,因此通常在設計靜電放電防護電路時,多以MOS晶體管為主。

這里介紹一款LED驅動芯片的ESD保護結構。芯片只有一對電源和地,在ESD構架方面比多對電源和地的芯片更簡單。可以分為幾種情況:輸入保護、輸出保護、電源和地之間的保護。ESD保護的設計除了使芯片免受靜電的損傷,還要考慮其他方面:首先,加入的ESD保護不能影響端口的功能;其次,不能造成芯片端口的漏電;再次,不能造成芯片的latch-up。以下進行這4種端口的設計,該芯片采用0.35μm 1P3M 5V CMOS工藝設計。

4.1 輸入端口的設計

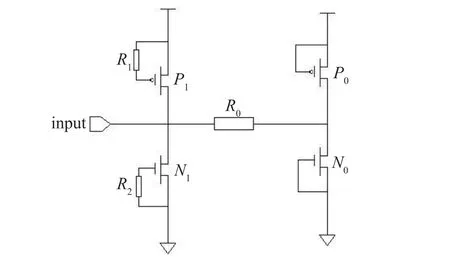

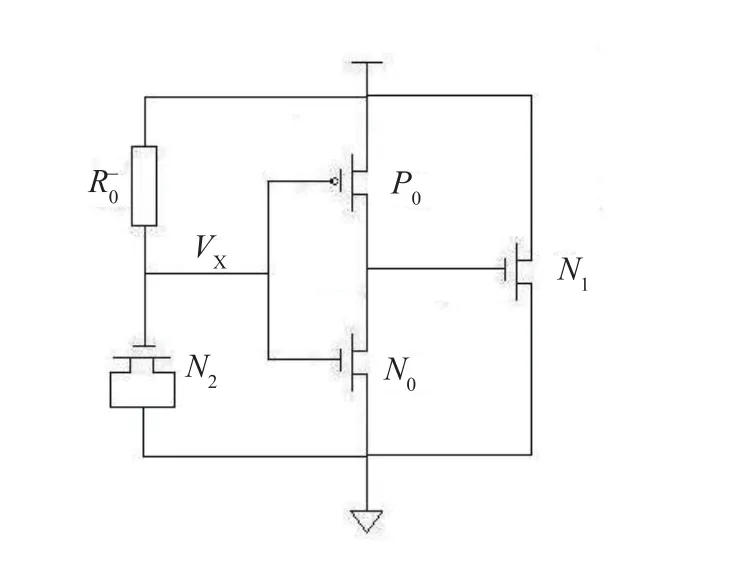

為了使輸入的薄柵氧得到最好的保護,所以采用兩級保護。第一級采用soft-pull 的MOS管,第二級采用poly電阻加柵接地的NMOS和柵接電源的PMOS。電路圖如圖5。

第一級選用MOS管,是因為在0.35μm工藝下,二極管、場管的保護效果不理想;另外SCR(可控硅)的效果比較好,面積利用率高,但比較難設計,而且有latchup風險。通常MOS管的ESD保護能力為10V/μm,如果想通過3000V(HBM),設計中心值處在4000V,MOS管的寬度為400μm,單個管子寬度根據ESD規則(30μm~60μm)定為50μm。溝道長度根據規則定為0.6μm。

圖5 輸入端口保護電路圖

針對NMOS存在不均勻導通的情況,即NMOS管的溝道寬度雖然設計值為400μm,但實際上可能只有100μm的NMOS管導通了,采用了soft-pull結構,此結構采用了gate-couple原理,使得NMOS管的觸發電壓降低,有利于NMOS管均勻導通。而PMOS管不存在這種情況。

第二級保護中的電阻選用poly電阻,主要是因為n-well電阻偏差比較大,而N+擴散電阻擊穿電壓低,此處設計并不想讓電阻擊穿。poly電阻的優點是寄生電容小、精度高,但散熱的特性比上兩種電阻差。所以,設計poly電阻的寬度足夠寬,保證散熱的面積足夠大以及能通過比較大的電流。一般poly電阻的寬度為10μm~20μm,由于是第二級保護,電流較小,寬度選為10μm。

第二級保護的MOS管主要是進一步降低輸入電壓,泄放ESD電流很小,所以寬度定為50μm,單個管子寬度為25μm。按照10V/μm計算,它能承受的ESD電壓為500V,能承受的ESD電流為500/1.5k=333mA。該芯片的輸入/輸出信號的頻率較低,第二級保護的電阻可以選大一些,設計規則最低要求200Ω,此處選了800Ω。假設第一級保護的MOS管二次擊穿的電壓為20V,那第二級保護的電阻和MOS管上的電流只有20/800=25mA,遠遠小于第二級保護上MOS管能承受的電流。

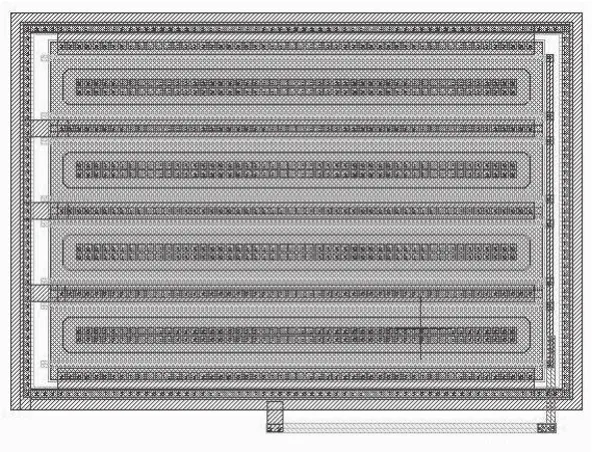

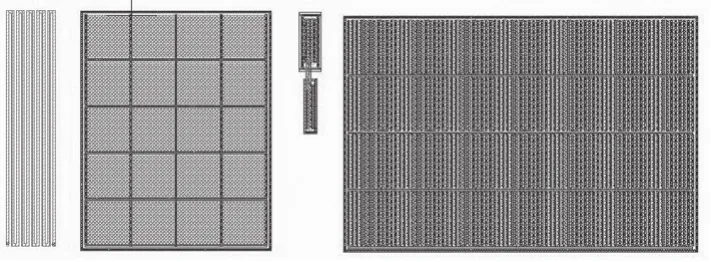

在版圖方面,剩下的主要參數是MOS管漏端的孔到柵的距離DCG。在深亞微米下,DCG通常為2μm~3μm,在亞微米,通常為5μm~6μm。在這里依據ESD的設計規則定為2μm。各個器件的版圖見圖6~圖8(圖片中的二鋁已經隱藏)。

圖6 輸入端口的ESD保護版圖

圖7 輸入端口的第一級保護NMOS管

圖8 輸入端口第二級保護的NMOS管

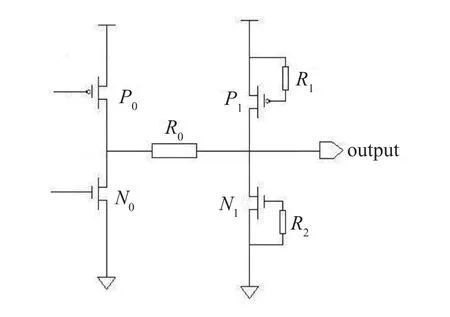

4.2 輸出端口的設計

輸出端口和輸入端口的主要區別在第二級保護上,限流電阻不能太大,否則會影響輸出的驅動能力。一般要求盡量小,出于ESD的考慮,電阻值定為100Ω。

圖9 輸出端口保護的電路圖

一般情況下,由于芯片在生產、運輸、測試過程中,芯片并未上電,靜電進入端口,輸出的輸入處于懸空,很容易被耦合到一個高電位,在ESD保護器件工作之前先導通放電。若在輸出管進入二次擊穿之前,第一級保護的MOS管還未工作,那輸出管就損壞了。通常MOS管的觸發電壓在10V左右。于是輸出管必須能承受10/100=100mA的ESD電流,也就是輸出管的寬度必須大于100mA×1.5k/10V/μm=15μm。另一方面,如果沒有限流電阻,要保證ESD保護管有效工作,需要做耦合電路,讓ESD保護管先觸發。器件的其他參數基本和輸入保護電路相同。

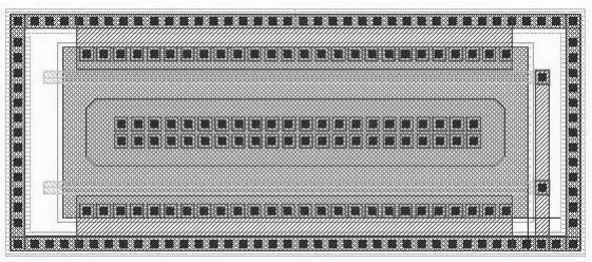

4.3 電源和地之間的保護

電源和地之間的保護電路是由一個電阻電容網絡、一個反相器和一個NMOS管組成的;RC網絡連接到反相器的輸入,它的輸出再連接到NMOS的柵極,如圖10所示。此電源保護電路在平時是不導通的。人體放電模型(HBM)的放電波形的上升時間約10ns,而芯片在上電時,電源的上升時間約為微秒到毫秒級。為了符合以上兩種要求,RC常數設計在次微秒到微秒級之間。當靜電出現在電源上時,由于RC網絡會產生延遲效應,圖10中Vx的電壓上升速度會較VDD來得慢,而在兩者之間產生電壓差。同時電壓差也出現在PMOS P0的柵源兩端。當此電壓差大于其開啟電壓時,P0導通而將NMOS N1的柵極上拉至VDD,因而NMOS N1就導通而以溝道泄放ESD電流。

圖10 電源和地之間的ESD保護

理論上如果N1的尺寸夠大的話,光靠導通就可以泄放掉所有的ESD電流而不會使晶體管工作在擊穿和snapback區,因此相對于柵極接地技術甚至柵極耦合技術來說,其反應速度要快許多。

此電路參數如圖10所示,電阻采用poly電阻,一方面是由于poly電阻精度高,另一方面是因為曾經有公司因采用n-well電阻導致在latchup測試時出現了問題。由于電阻上電流很小,電阻的寬度采用了電阻的最小寬度。電容采用了NMOS管,屬于反型的MOS管。

導通ESD電流的NMOS N1寬度很大,因此面積很大。所以芯片面積很小的話通常不采用這樣的電源和地的ESD保護方式。該保護電路的版圖見圖11(圖中二鋁已經隱藏)。

圖11 電源和地之間的ESD保護布局

5 總結

本文從ESD的原理著手,介紹了ESD保護的重要性以及IC設計中常用的一些ESD保護器件、結構、尺寸,并以一款0.35μm 1P3M CMOS工藝中成功驗證的芯片ESD保護為例進行具體說明。

當分析ESD保護時,不僅要分析各個端口的保護,更重要的是要把ESD保護當作一個整體來分析。對于每個端口都有4種情況:PS、NS、PD、ND。分析這4種情況時不能只分析某一個端口,一定要把電源和地之間的保護放進來一并考慮。

在設計具體器件時,主要參考foundry提供的ESD設計規則。最好使用I/O單元庫,因為單元庫是foundry驗證過的。如果遇到沒有單元庫或者所設計芯片端口有特殊要求時,一般不自行設計,而是參考以前的設計經驗。

本論文涉及的版圖參數主要針對0.35μm的CMOS工藝,并不是通用的尺寸。即使同樣是0.35μm的工藝,不同的foundry涉及的參數也不盡相同。

[1] MIL-STD-883C method 3015.7, Military Standard Test Methods and Proc. For Microelectronics[DB].Dept. of Defense, Washington, D. C., U.S.A., 1989.

[2] Ming-Dou Ker and Tain-Shun Wu, ESD Protection for Submicron CMOS IC’s—A Tutorial[DB].CCL Technical Journal,1995,42: 10-24.

[3] T. J. Maloney and N. Khurana. Transmission Line Plising Techniques for Circuit Modeling of ESD Phenomena[DB].EOS/ESD Symposium Proceedings, EOS-7, 1985. 49-54.

[4] T. J. Maloney and N. Khurana. Transmission Line Plising Techniques for Circuit Modeling of ESD Phenomena[DB].EOS/ESD Symposium Proceedings, EOS-7, 1985. 49-54.

[5] C. Duvvury, R. N. Rountree, and O. Adams. Internal chip ESD phenomena beyond the protection circuit[DB].IEEE Trans. on Electron Devices, 1988,35(12): 2133-2139.

[6] H. Terletzki, W. Nikutta, and W. Reczek. Influence of the series resistance of on-chip power supply buses on internal device failure after ESD stress[DB]. IEEE Trans. on Electron Devices, 1993,40(11): 2081-2083.

[7] M. D. Jaffe and P. E. Cottrell. Electrostatic discharge protection in a 4-Mbit DRAM[DB]. EOS/ESD Symp.Proc., EOS-12, 1990.218-223.

[8] C. Cook and S. Daniel. Characterization of new failure mechanisms arising from power-pin ESD stressing[DB].EOS/ESD Symp. Proc., EOS-15, 1993.149-156.

[9] EOS/ESD Standard for ESD Sensitivity Testing[DB]. EOS/ESD Association, NY., 1993.

[10] C.-N. Wu, M.-D. Ker, et al. Unexpected ESD damage on internal circuits of sub-μm CMOS technology[DB].Proc. of International Electron Devices and Materials Symposium,1996.143-146.