基于小數分頻鎖相的X波段頻率合成器設計

代傳堂,柴文乾

(中國電子科技集團公司第三十八研究所,合肥 230088)

0 引言

頻率合成器是通信、雷達、儀器儀表、空間電子設備等電子系統的心臟,其好壞直接影響電子系統的性能指標[1]。隨著電子技術的飛速發展,現代電子系統對頻率合成器的性能指標要求也越來越高,大頻帶、小步進、低雜散、低相位噪聲和快速變頻等成為頻率合成器的技術發展趨勢[2],同時高集成、小體積、低功耗和低成本等成為頻率合成器的應用發展方向。

本文介紹了一種基于鎖相技術的X波段線性調頻頻率合成器的設計方法,其核心器件采用了Hittite公司近期推出的集成VCO的鎖相芯片HMC767。該頻率合成器在HMC767 內置VCO的工作頻帶內可實現點頻和大帶寬線性調頻信號輸出,具有低相位噪聲、大帶寬、小步進、小體積、低功耗和低成本等優點。

1 鎖相芯片HMC767

HMC767為內置集成VCO的鎖相環芯片,內置VCO的輸出頻率范圍為8.45~9.55 GHz,輸出頻率分辨率典型值為3 Hz,支持小數分頻和整數分頻的工作模式;外部輸入的參考信號頻率最高可達350 MHz,內部鑒相器的鑒相頻率最高可支持115 MHz。較高的鑒相頻率一方面可以降低頻率合成器輸出信號的相位噪聲,另一方面在設計環路濾波器時可適當增加環路帶寬,從而可縮短鎖相環的鎖定時間[3]。

該芯片為6 mm×6 mm、40 引腳的QFN 封裝形式,底部有大面積的接地焊盤。該接地焊盤既保證了芯片良好的接地效果,也提供了芯片的散熱通道(該款芯片的電流較大,設計時需充分考慮芯片的散熱)。

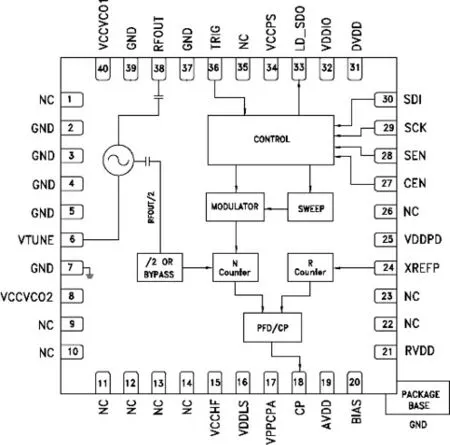

該芯片的內部功能框圖見圖1所示,主要包含了參考支路的R分頻器、反饋支路的N分頻器、VCO、鑒相器、電荷泵、△Σ 調制器、掃頻模塊和多個控制寄存器等。高集成的內部結構形式不僅使其應用時省去一些外部電路而提高了頻率合成器的集成度,同時也給芯片本身帶來了更為出色的相位噪聲性能。鑒相頻率為50 MHz時,芯片輸出9 GHz信號的單邊帶相位噪聲指標典型值約為-107 dBc/Hz@10 kHz(整數分頻模式)、-102 dBc/Hz@10 kHz(小數分頻模式)[4]。

圖1 HMC767 內部功能框圖

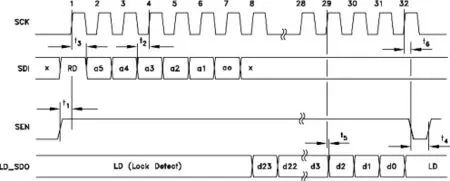

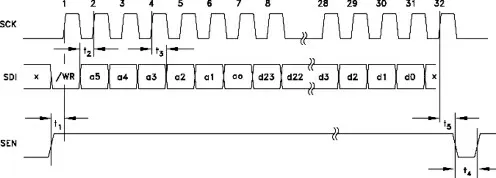

該芯片的控制主要由SDI、SCK、SEN、CEN、TRIG和LD_SDO 等引腳來實現。SDI、SCK和SEN 引腳以SPI 形式寫入控制數據,進行配置芯片內部的寄存器。詳細的讀、寫操作時序圖見圖2、圖3所示。HMC767芯片共有16個可配置的內部寄存器。不同的寄存器配置可以實現不同的功能,如果寄存器配置有誤,可能會導致頻率合成器無法正常工作,因此寄存器的配置非常重要。CEN為芯片使能引腳,高電平時芯片正常工作。TRIG為外部觸發引腳,在小數分頻模式下可觸發相關的功能。LD_SDO為多功能輸出引腳,可對該引腳進行配置,輸出芯片內部相對應的信號。

2 設計方案

圖2 讀操作時序圖

圖3 寫操作時序圖

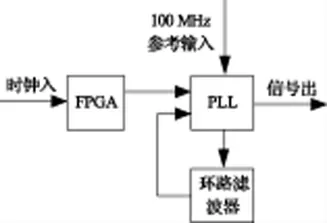

該頻率合成器的原理實現框圖見圖4所示,其中“時鐘入”為FPGA 芯片的低頻工作時鐘,“100 MHz 參考入”為鎖相芯片的參考時鐘,由100 MHz的低相噪恒溫晶振提供。該方案電路實現上主要由3個部分組成:FPGA、PLL和環路濾波器。FPGA為Altera 公司生產的FPGA,主要為鎖相芯片提供控制信號,對鎖相芯片的內部寄存器進行正確配置。PLL為HMC767 鎖相芯片,接收來自FPGA的控制信號,內部電荷泵輸出鑒相誤差脈沖信號送環路濾波器,并接收經過環路濾波器濾波輸出的調諧電壓,最后根據該調諧電壓VCO 輸出相應頻率的信號。

圖4 頻率合成器設計框圖

2.1 小數分頻鎖相技術

小數分頻鎖相技術是由整數分頻鎖相技術的理論發展得來的,它們的區別在于VCO 反饋支路的N分頻器不同。顧名思義,小數分頻鎖相電路的N分頻器可進行小數分頻,整數分頻鎖相電路的N分頻器只能進行整數分頻。目前,應用較多的小數分頻鎖相技術為Σ-△調制技術,其優點是全數字架構,易于大規模集成,可很好地抑制由小數分頻帶來的雜散。

整數分頻鎖相電路的最小頻率分辨率等于環路的鑒相頻率。所以,為了提高頻率合成器輸出信號的頻率分辨率,只能降低環路的鑒相頻率,在輸出頻率不變的前提下降低鑒相頻率就意味著提高環路反饋支路的分頻比。而鎖相電路的相位噪聲主要由環路近載頻噪聲(參考源、鑒相器的等效噪聲)和VCO 遠載頻噪聲組成[5],環路的分頻比越大,環路的近載頻噪聲就越差,環路的帶寬就越窄。由于小數分頻鎖相技術可對VCO 反饋支路的信號進行小數分頻,頻率合成器的最小頻率分辨率等于鑒相頻率的小數倍,從而降低了環路總的分頻比,有效地降低鎖相電路輸出信號的相位噪聲;而Σ-Δ 調制器的噪聲整形技術可以很好地抑制由小數分頻帶來的低頻噪聲(高頻噪聲可通過后級的環路濾波器濾除),從而提高輸出信號的質量。

因此,在實際的工程應用中,與整數分頻鎖相電路相比,小數分頻鎖相電路可用更高的鑒相頻率和更低的環路總分頻比,在實現高的頻率分辨率的同時,進一步提高頻率合成器的相位噪聲、捷變頻時間和雜散抑制等關鍵指標。

2.2 寬帶線性調頻信號

目前,寬帶線性調頻信號的產生主要有下面3 種方式:一是DDS 產生低頻線性調頻信號,再用鎖相環鎖至高頻段實現;二是DDS 產生低頻線性調頻信號,再通過倍頻、混頻的方式實現;三是基于數字直讀波形產生,數字直讀產生正交基帶信號,再進行射頻調制實現。本文介紹的是一種新的大寬帶線性調頻信號產生方式。該方案通過軟件配置鎖相芯片HMC767。該芯片內置的VCO 直接輸出大帶寬的線性調頻信號。該方式產生的線性調頻信號的帶寬僅受VCO 輸出的頻率范圍限制。與其他的寬帶線性調頻信號實現方式相比,本方式具有設備量小、線性度高、功耗低、集成度高、成本低和體積小等優點。

2.3 輸出頻率計算

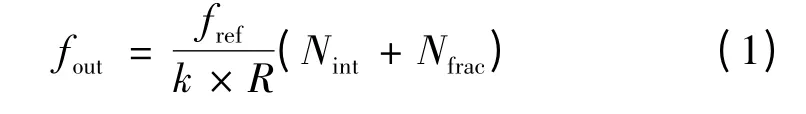

該鎖相芯片的輸出頻率計算公式為

其中,fout為鎖相環輸出信號的頻率,fref為輸入參考信號的頻率,k為VCO 反饋支路信號的分頻系數,R為參考支路R分頻器的分頻比,Nint為VCO 反饋支路N分頻器分頻比的整數部分,Nfrac為VCO 反饋支路N分頻器分頻比的小數部分。

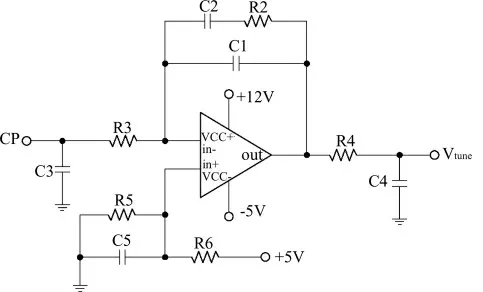

2.4 環路濾波器

環路濾波器的設計是整個頻率合成器設計的關鍵,主要作用是濾除鑒相誤差電壓中的高頻分量和噪聲。環路濾波器決定了頻率合成器的雜散抑制、相位噪聲、鎖定時間和穩定性等重要指標[6],在設計時應該合理兼顧各項指標的要求。

環路濾波器分無源環路和有源環路。無源環路濾波器受鎖相芯片電荷泵供電電壓限制,輸出的VCO 調諧電壓不高于電荷泵供電電壓,所以無源環路適用于VCO 調諧電壓較低的應用場合。在需要較高的VCO調諧電壓時,必須采用有源環路濾波器。在對輸入的鑒相誤差信號濾波的同時有源環路濾波器還提供一定的增益,將VCO的調諧電壓調整到合適的范圍。

由于本設計中實際使用時VCO的調諧電壓高于鎖相芯片電荷泵供電電壓,故采用了有源環路濾波器。圖5 給出了環路濾波器的設計原理框圖。

圖5 環路濾波器電路原理圖

2.5 相位噪聲

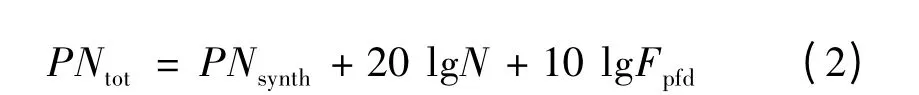

眾所周知,鎖相環的帶內相位噪聲可根據以下公式計算得出:

其中,PNtot為鎖相環輸出信號的帶內相位噪聲,PNsynth為鎖相環的歸一化帶內相位基底噪聲,N為VCO 反饋信號的分頻比,Fpfd為鑒相頻率。

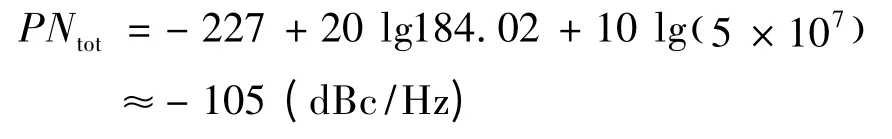

HMC767 在整數分頻模式下PNsynth典型值為-230 dBc/Hz,在小數分頻模式下PNsynth典型值為-227 dBc/Hz;若Fpfd為50 MHz,小數分頻輸出信號為9.201 GHz時,根據公式(2),帶內相位噪聲的理論計算如下:

3 測試結果

通過以上的分析,對該頻率合成器進行了性能測試,測試結果如下。

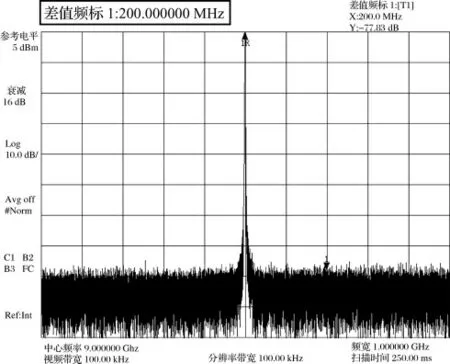

圖6為輸出9 GHz信號的頻譜圖,從圖上可以看出,該頻點的雜散抑制指標優于70 dBc。

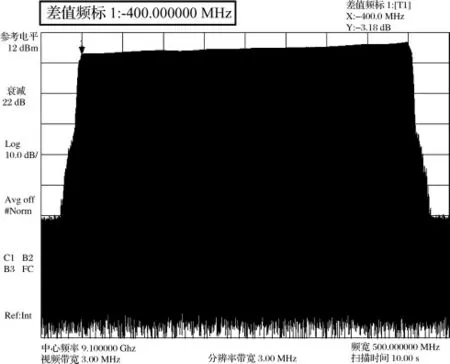

圖7為輸出中心頻率為9.1 GHz、帶寬為400 MHz線性調頻信號的頻譜圖。

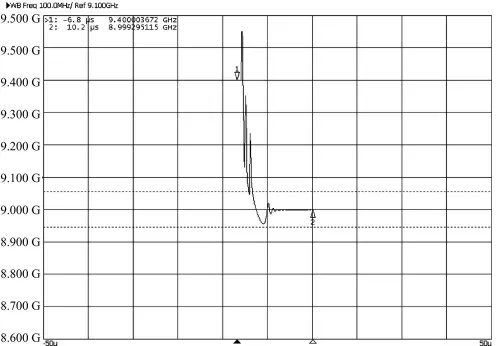

圖8為輸出頻率由9.4 GHz 變為9 GHz時的跳頻時間測試曲線。該頻率變化400 MHz時的跳頻時間約為17 μs。

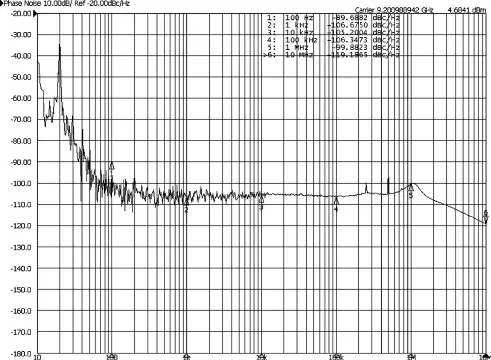

圖9為鑒相頻率為50 MHz時小數分頻輸出9.201 GHz信號的相位噪聲測試曲線,相位噪聲指標約為-106 dBc/Hz@1kHz、-105 dBc/Hz@10 kHz。實際測試的結果與前面計算出的理論值較為接近。

圖6 頻率為9 GHz的頻譜圖

圖7 400 MHz 帶寬線性調頻信號頻譜圖

圖8 跳頻時間測試曲線

圖9 相位噪聲測試曲線

4 結束語

本文基于小數分頻鎖相技術,采用了內置集成VCO的鎖相芯片,實現了X波段低雜散、低相位噪聲的頻率合成器的設計。實驗測試結果表明該頻率合成器性能優異。該頻率合成器實現電路簡單,在鎖相芯片內置VCO的頻率范圍內實現任意步進點頻信號和大帶寬線性調頻信號輸出,可用于雷達系統收發通道的本振信號和寬帶系統的超寬帶信號的產生。該頻率合成器具有設備量小、集成度高、體積小、功耗低、成本低等優點,為現代雷達和電子系統提供了新的頻率合成器解決方案。

[1]Vadim Manassewitsch.頻率合成原理與設計[M].何松柏,宋亞梅,鮑景富,等譯.3 版.北京:電子工業出版社,2008.

[2]劉永智,鮑景富,高樹廷.一種寬帶頻率綜合器的設計與實現[J].中國電子科學研究院學報,2011,6(1):24-27.

[3]潘玉劍,張曉發,袁乃昌.基于HMC830的低相噪低雜散頻率源設計[J].電子設計工程,2011,19(19):180-186.

[4]Hittite Microwave Corporation.HMC767LP6C Datasheet[DB/OL].2012.http://www.hittite.com/content/documents/data_sheet/hmc767lp6c.pdf.

[5]方立軍,馬駿,王元慶.分數分頻鎖相頻率合成器及其實驗研究[J].現代雷達,2002,78(1):36-40.

[6]趙彥芬.頻率合成器環路濾波器的設計[J].無線電工程,2006,36(4):39-41.