一種改進太陽能計算器芯片二極管穩壓電路設計

張立榮

(深圳方正微電子有限公司,廣東 深圳 518116)

1 引言

目前,市面上的民用計算器以電源類型分為兩種,一種是只用電池,一種是電池和太陽能雙用。后面這種即使不安裝電池,在普通的室內照明之下使用,也可由內置太陽能電池板供電。

對于電池和太陽能雙用的計算器,其核心芯片的穩壓電路設計是至關重要的。市面上大部分此類產品的穩壓電路的設計是串聯三個PN結二極管以達到穩壓目的。這種設計會出現以下問題:當外部光線太強時,由于太陽能電池板的供電電壓較高,而穩壓電路由于正向飽和壓降過高,不能及時將高電壓釋放掉,所以液晶屏會出現“鬼影”現象。本研究的目的在于改進二極管穩壓電路的設計,將其中一個PN結二極管改為肖特基二極管,使其正向飽和壓降處于一個合理的區間,避免上述的“鬼影”現象,從而達到改善太陽能應用的目的。

2 肖特基二極管的特性

肖特基二極管也稱肖特基勢壘二極管,肖特基二極管是以金屬(金、銀、鋁、鉑等)為正極,以N型半導體為負極,利用二者接觸面上形成的勢壘具有整流特性而制成的金屬-半導體器件。肖特基二極管具有以下特性:

(1)正向壓降小,約0.35V左右,比PN結二極管0.7V的壓降小很多;

(3)更穩定的溫度特性;

(4)有較高的工作頻率和開關速度。

圖1 肖特基二極管和PN結二極管曲線特性對比

從圖1可以看到,肖特基二極管的正向飽和壓降比PN結二極管小很多。

3 優化二極管穩壓電路設計的方法

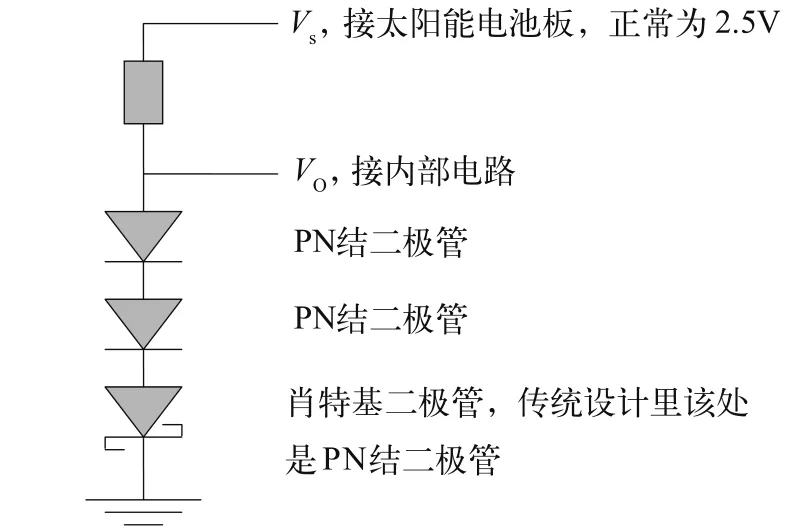

應用于太陽能的計算器芯片中的二極管穩壓設計電路如圖2所示。

Vo是接計算器內部電路的,它的電壓必須控制在1.6V~1.9V左右。當Vo大于1.9V時,3個二極管必須開啟,釋放多余電流,以保護Vo處的內部電路。所以3個二極管串聯的正向飽和壓降必須處于1.6V~1.9V之間。

(1)如果3個二極管的正向飽和壓降大于1.9V,當使用環境的光線太強時,Vo會比正常時偏高,而此時二極管又不能釋放電流,這樣就會出現顯示屏“鬼影”的現象,影響正常使用;

(2)如果3個二極管的正向飽和壓降小于1.6V,那么當計算器使用在電池狀態下時,電池就會漏電,影響電池使用壽命。

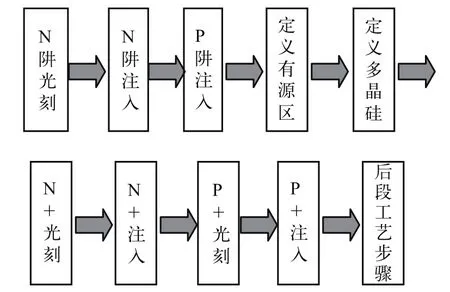

用以制造計算器芯片的0.8μm互補金屬氧化物半導體工藝簡易流程如圖3所示。 N阱注入和P+ 注入是形成PN結二極管的兩個重要工藝步驟。如果跳過P+注入,那么就會形成肖特基二極管。

圖2 穩壓電路的結構

圖3 0.8μm CMOS制造工藝流程

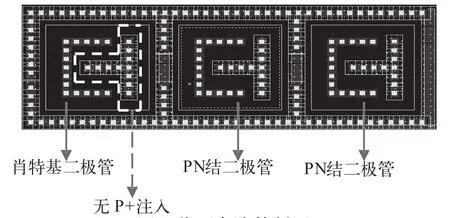

該設計電路版圖如圖4所示。其中第一個二極管,因為無P+注入,所以由原來的PN結二極管變成肖特基二極管。在修改設計前,必須用足夠的試驗數據證明:兩個串聯的PN結二極管再串聯一個肖特基二極管,其整體的正向飽和壓降在1.6V~1.9V。為此,我們在做工藝試驗時,只需要跳過P+注入,就可以將電路中的三個二極管全部制作為肖特基二極管,測試這三個肖特基二極管的正向飽和壓降,如果值在1.05V左右,即單個肖特基二極管是0.35V,便可證明此方案可行。同時,我們還需要做一些可靠性驗證,如溫度對正向飽和壓降的影響。

在企業的內部審計實踐中,規范的審計流程應分為事前準備、事中實施、事后反饋3個完整的階段,后續審計在整個審計過程中起著至關重要的作用,它能夠對企業是否已經將審計建議進行落實和糾正進行如實反饋,對審計工作起到監督落實的作用。JY酒店的審計流程如圖1—1所示,在此流程中,其開展的審計工作只包含內審的前兩個階段,忽略了后續審計,JY酒店的內部審計部門對審計事項進行前期準備并現場審計之后,提出了相應的審計意見以及整改事項,但沒有對財務部門的審計整改實施情況進行回訪與追蹤,后續審計不力,審計整改事項的落實更多依靠的是財務部門的主觀能動性。這樣的實踐降低了整個內審工作的效率和效果,不利于審計質量的提升。

圖4 穩壓電路的版圖

4 實驗結果討論

4.1 實驗過程

為了方便實驗,在工藝流片時,對于原先的3個普通二極管的mask設計,跳過P+注入,就可以將原來的3個普通二極管設計變成3個肖特基二極管。這樣就能夠驗證3個肖特基二極管的參數性能。

如果參數合格,那么就能說明,后續通過修改P+層次的mask設計,將原來的3個普通二極管設計改成2個普通二極管串聯1個肖特基二極管的設計能夠滿足此產品對參數的要求。

4.2 實驗結果

3個肖特基二極管的正向飽和壓降為1.05V,即單個肖特基二極管的壓降為0.35V,符合實驗預期。

圖5 肖特基二極管的正向飽和壓降

(1)測試方法:掃電壓,從0掃到2V,同時測試電流,當電流為150μA時的電壓即為正向飽和壓降。

(2)片內均勻性:一片晶圓測試20個點,上中左下右各5個點。數據顯示,片內的均勻性比較好,都在1V~1.1V間波動,平均值1.02V,如圖6。

圖6 肖特基二極管正向飽和壓降片內均勻性

(3)金屬厚度(Ti)對正向壓降的影響。將金屬厚度0.03μm和 0.05μm的正向壓降進行對比,數據顯示,不同金屬厚度的正向飽和壓降差別很小,只有約0.005V,說明即使工藝(金屬厚度)發生波動,對飽和壓降的影響也很小,工藝上是完全可行的。

(4)溫度對正向壓降的影響。民用計算器的使用溫度多在40℃以下。所以我們特別測試了室溫(23℃)和40℃時正向飽和壓降的變化。數據說明變化很小,只有約0.02V。

圖7 金屬厚度對肖特基正向飽和壓降的影響

試驗說明:(1)跳過P+注入后,正向飽和壓降的重復性和均勻性比較好,波動較小;(2)不同的金屬厚度(0.03μm和0.05μm)對正向飽和壓降的影響很小;(3)室溫下(23℃)測試和40℃下測試,正向飽和壓降波動較小,與理論上的分析也是一致的。

5 結束語

只需改變P+ mask,將其中一個二極管的P+去掉,三個二極管的正向飽和壓降可從2.1V降到1.75V左右,基本滿足應用要求,可避免“鬼影”現象產生。

[1] 李強,王俊宇. 標準CMOS工藝集成肖特基二極管設計與實現[J]. 半導體學報,2005,2.

[2] 章從福. 整合肖特基二極管的單片MOSFET [J]. 半導體信息,2008,2.