基于VHDL的MTM總線主模塊有限狀態(tài)機(jī)設(shè)計(jì)

王 超,白忠臣,李世雄,秦水介

(貴州大學(xué) 貴州省光電子技術(shù)及應(yīng)用重點(diǎn)實(shí)驗(yàn)室,貴州 貴陽(yáng) 550025)

MTM 總線 (Module Testing and Maintenance bus,MTM-bus)是一種同步、串行、用于系統(tǒng)級(jí)的背板測(cè)試及維護(hù)總線,可以實(shí)現(xiàn)IEEE1149.5標(biāo)準(zhǔn)所規(guī)定的故障檢測(cè)、容錯(cuò)以及擴(kuò)展的命令集[1]。該技術(shù)已經(jīng)被美軍“寶石柱”和“寶石臺(tái)”計(jì)劃的航空電子系統(tǒng)體系結(jié)構(gòu)采用[2]。

當(dāng)前MTM總線主模塊有限狀態(tài)機(jī)主要采用Verilog HDL程序編寫(xiě)的狀態(tài)機(jī)描述,Verilog HDL語(yǔ)言并不可以進(jìn)行系統(tǒng)級(jí)的硬件描述。

VHDL是一種標(biāo)準(zhǔn)化的硬件描述語(yǔ)言,不僅可以用于系統(tǒng)級(jí)的硬件描述而且在設(shè)計(jì)系統(tǒng)硬件時(shí)沒(méi)有嵌入與工藝有關(guān)的信息,在工藝更新時(shí)無(wú)須修改原設(shè)計(jì)程序。文中設(shè)計(jì)的狀態(tài)機(jī)采用“單進(jìn)程”式狀態(tài)機(jī)描述,與“三進(jìn)程”和“雙進(jìn)程”式相比可以有效地節(jié)省FPGA芯片的資源,從而進(jìn)一步減少功耗,提高系統(tǒng)的穩(wěn)定性[3]。

通過(guò)簡(jiǎn)要分析MTM總線的基本結(jié)構(gòu)、各模塊間的通訊方式、主模塊有限狀態(tài)機(jī)模型基于VHDL語(yǔ)言設(shè)計(jì)了主模塊有限狀態(tài)機(jī);并且利用QuartusⅡ9.0版本軟件和Cyclone系列EP1C6Q240C6芯片對(duì)所設(shè)計(jì)的MTM總線主模塊狀態(tài)機(jī)的VHDL代碼進(jìn)行了時(shí)序仿真和功能仿真。

1 MTM總線結(jié)構(gòu)設(shè)計(jì)

1.1 MTM總線的基本結(jié)構(gòu)

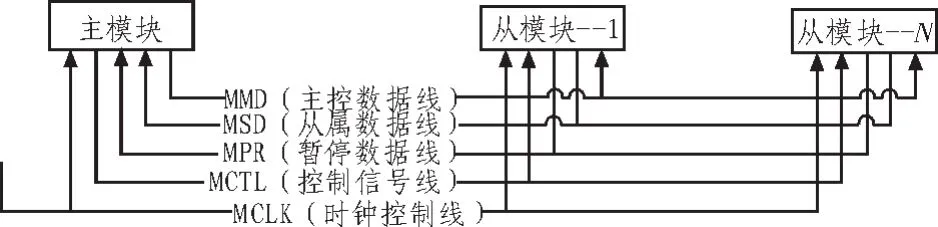

MTM總線的基本結(jié)構(gòu)如圖1所示,總線定義了4條必選信號(hào)線和一條可選信號(hào)線,即MCTL(控制信號(hào)線)、MMD(主模數(shù)據(jù)信號(hào)線)、MSD(從模塊數(shù)據(jù)信號(hào)線)、MCLK(時(shí)鐘信號(hào)線)和MPR(請(qǐng)求暫停信號(hào)線)。

圖1 MTM總線結(jié)構(gòu)圖Fig.1 MTM bus structure

MTM總線上的所有模塊采用主從結(jié)構(gòu)的通訊協(xié)議,該總線有且只能有一個(gè)主模塊,最多可以有250個(gè)能夠被獨(dú)立尋址的從屬模塊。MTM總線多站點(diǎn)結(jié)構(gòu)和尋址能力允許主模塊一次可以尋址一個(gè)從模塊、多個(gè)從模塊(多點(diǎn)尋址方式)和所有的從模塊(廣播尋址方式),并且與之通訊。MTM總線的主模塊有限狀態(tài)機(jī)是MTM總線主模塊的核心控制單元,它控制著整個(gè)信息傳輸過(guò)程[4]。MTM總線控者使用消息交換的方式與從模塊進(jìn)行通訊,消息是由一系列的包組成,包括一個(gè)頭包,一個(gè)可選答應(yīng)包和一系列數(shù)據(jù)包,包的長(zhǎng)度為17位,高16位數(shù)據(jù)信息,最低位用于奇校驗(yàn),消息包的控制必須由主模塊控制[5]。

1.2 MTM主模塊

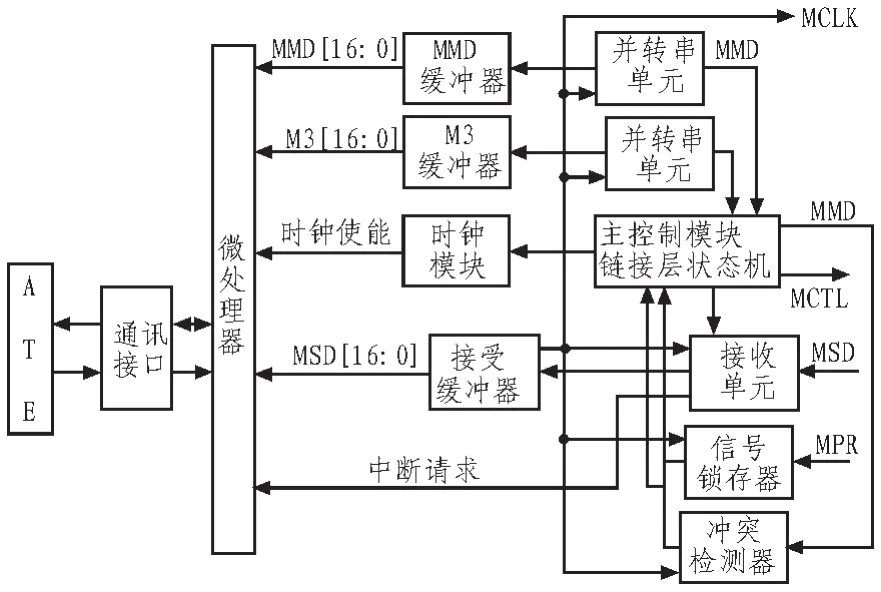

主控制模塊設(shè)計(jì)如圖2所示。主控制模塊在MTM總線協(xié)議中處于主控地位,主要功能是將來(lái)自微處理器的數(shù)據(jù)按照IEEE1149.5標(biāo)準(zhǔn)定義的消息格式進(jìn)行打包送到指定的從控制模塊;同時(shí)將來(lái)自指定從控制模塊的消息包進(jìn)行解包,并且提取有用數(shù)據(jù)傳回微處理器,供微處理器分析和處理。

圖2 主控制模塊設(shè)計(jì)Fig.2 Master control module design

主狀態(tài)機(jī)是主控制模塊的核心單元,它的作用是控制整個(gè)信息傳輸過(guò)程。

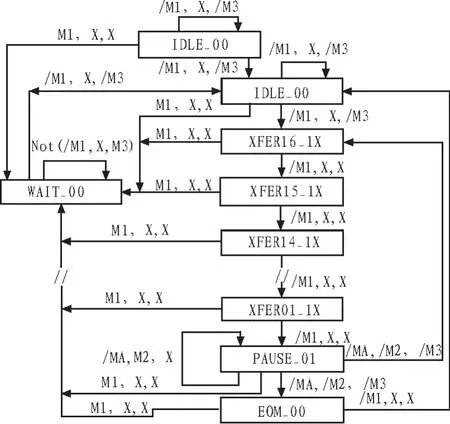

主狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換圖如圖3。當(dāng)主狀態(tài)機(jī)處于某個(gè)給定的狀態(tài)時(shí),MCTL和MMD信號(hào)的邏輯值在MCLK的上升沿產(chǎn)生;在每個(gè)MCLK信號(hào)周期,主狀態(tài)機(jī)根據(jù)控制信號(hào)的只發(fā)生狀態(tài)轉(zhuǎn)換;在主狀態(tài)機(jī)的17個(gè)傳送狀態(tài)下發(fā)送17位的數(shù)據(jù)包,其他狀態(tài)不發(fā)送數(shù)據(jù),同時(shí)接收MSD上的數(shù)據(jù);在每個(gè)數(shù)據(jù)包發(fā)送后,主狀態(tài)機(jī)至少保持在暫停狀態(tài)不少于4個(gè)MCLK周期,若當(dāng)前接收的MSD數(shù)據(jù)有效則使接收單元使能信號(hào)有效;當(dāng)主狀態(tài)機(jī)進(jìn)入結(jié)束狀態(tài)時(shí),當(dāng)前消息傳送結(jié)束[3]。

2 基于VHDL的主模塊有限狀態(tài)機(jī)的的設(shè)計(jì)

VHDL主要用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)、行為、功能和接口,同時(shí)支持層次化和模塊化設(shè)計(jì),并且可以進(jìn)行仿真和綜合。

數(shù)字電路分為組合邏輯電路和時(shí)序邏輯電路兩種。組合邏輯電路的輸出只與當(dāng)前輸入有關(guān),時(shí)序邏輯電路的輸出與當(dāng)前輸入和過(guò)去輸入都有關(guān)。狀態(tài)機(jī)是一種廣義的時(shí)序電路,一般包括用于狀態(tài)譯碼和產(chǎn)生輸出信號(hào)組合邏輯和存儲(chǔ)狀態(tài)的寄存器邏輯兩部分[4]。

根據(jù)MTM總線主模塊的狀態(tài)轉(zhuǎn)換圖,其基于VHDL有限狀態(tài)機(jī)的代碼如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

圖3 主狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換圖Fig.3 The Lord of the state machine state transition figure注:M1,M2,M3為狀態(tài)轉(zhuǎn)換的控制位。其中M1表示M1為1,/M1為0,X表示0或者1的任意值。

entity ztj is

port(

M1,M2,M3,clk:in std_logic;

state:out std_logic_vector(4 downto 0)

);

end ztj;

architecture hav of ztj is

typestis(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,

s14,s15,s16,powerup,idle,pause,eom,waiting);

signal ps,ns:st;

begin

process(clk)

begin

if clk’event and clk=’1’ then

ps<=ns;

end if;

end process;

process(M1,M2,M3,ps)

begin

case ps is

when powerup=>if M1=’1’ then

ns<=waiting;

elsif M3=’0’ then

ns<=powerup;

else

ns<=idle;

end if;

state<=“10001”;

…… ……

when s16=>if M1=’0’ then

ns<=s15;

else

ns<=waiting;

end if;

state<=“10000”;

…… ……

when s0=>if M1=’0’ then

ns<=pause;

else

ns<=waiting;

end if;

state<="00000";

…… ……

when waiting=>if M1=’0’ and M3=’1’ then

ns<=idle;

else

ns<=waiting;

end if;

state<="10101";

when others=>null;

end case;

end process;

end;

3 仿真驗(yàn)證

QuartusⅡ是Altera公司推出的集成開(kāi)發(fā)軟件,使用QuartusⅡ可以完成從設(shè)計(jì)輸入、綜合適配、仿真到編程下載整個(gè)設(shè)計(jì)過(guò)程,QuartusⅡ也可以直接調(diào)用Synplify Pro、以及ModelSim等第3方EDA工具來(lái)完成設(shè)計(jì)任務(wù)的綜合和仿真。

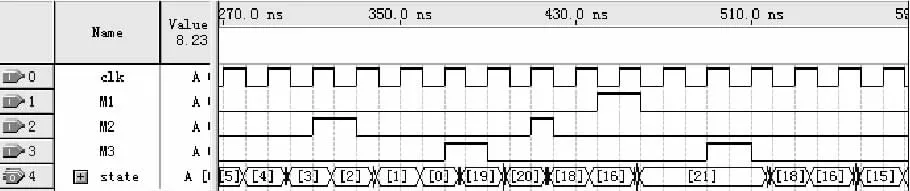

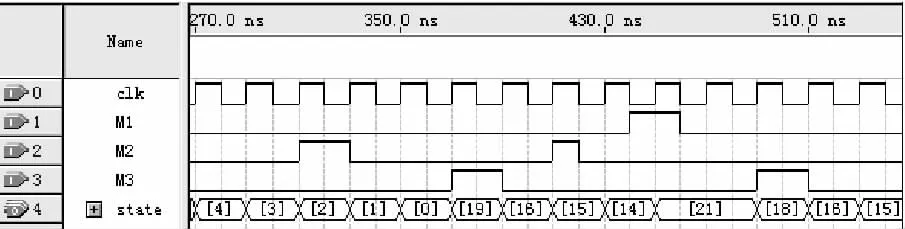

文中利用QuartusⅡ9.0版本軟件和Cyclone系列EP1C6Q240C6芯片對(duì)所設(shè)計(jì)的MTM總線主模塊狀態(tài)機(jī)的VHDL代碼進(jìn)行了時(shí)序仿真和功能仿真,分別如圖4、圖5所示。

圖4 時(shí)序仿真波形圖Fig.4 Timing simulation waveform figure

圖5 功能仿真波形圖Fig.5 Function simulation waveform figure

通過(guò)波形圖可以觀察到,該狀態(tài)機(jī)可以很好的實(shí)現(xiàn)主狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換。當(dāng)M1輸入為“0”時(shí)(此時(shí)M2、M3為無(wú)關(guān)狀態(tài)),MTM總線主模塊按照從高到低進(jìn)行消息傳送,直到進(jìn)入“PAUSE”(暫停狀態(tài))然后狀態(tài)回到“xfer16”(S16)繼續(xù)進(jìn)行消息傳送;當(dāng)M1輸入為“1”時(shí),主模塊無(wú)條件進(jìn)入“waiting”(等待狀態(tài));在主模塊處于“waiting”狀態(tài)時(shí)若M3輸入為“1”狀態(tài)轉(zhuǎn)入“idle”(空閑狀態(tài))再次由高到低位的消息傳送。

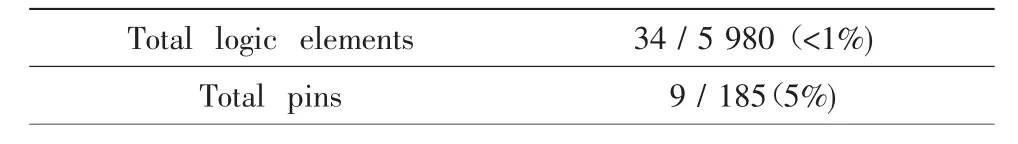

使用VHDL語(yǔ)言描述,語(yǔ)法更為嚴(yán)謹(jǐn),描述更為清晰簡(jiǎn)潔;采用“單進(jìn)程”式狀態(tài)機(jī)描述可以有效地節(jié)省FPGA芯片的資源(表1),從而進(jìn)一步減少功耗,提高系統(tǒng)的穩(wěn)定性。

表1 編譯報(bào)告Tab.1 Compilation report

4 結(jié)束語(yǔ)

文中通過(guò)研究MTM總線的基本結(jié)構(gòu)和主從模塊間的通訊協(xié)議,分析了主狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換,并使用VHDL語(yǔ)言設(shè)計(jì)了該有限狀態(tài)機(jī),并使用QuartusⅡ開(kāi)發(fā)軟件對(duì)該狀態(tài)機(jī)進(jìn)行了仿真和驗(yàn)證,仿真結(jié)果表明該程序可以正確描述主狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換,該有限狀態(tài)機(jī)使用“單進(jìn)程”式描述,與“三進(jìn)程”和“雙進(jìn)程”式相比程序簡(jiǎn)潔明了并且能夠有效地節(jié)省資源,減少功耗,提高系統(tǒng)的穩(wěn)定性。

[1]Kerr J L.A VHDL synthesis approach to the IEEE P1149.5 bus standard[S].1993:129-134.

[2]張小林,劉海彬.電子系統(tǒng)BIT設(shè)計(jì)技術(shù)初探[J].中國(guó)測(cè)試技術(shù), 2008, 34(3):80-83.ZHANG Xiao-lin,LIU Hai-bin.Design technology research for electronic system BIT[J].China Testing Technology,2008, 34(3):80-83.

[3]詹仙寧,田蕓.VHDL開(kāi)發(fā)軟件精解與實(shí)例剖析[M].北京:電子工業(yè)出版社,2009.

[4]孟小風(fēng),鐘波,徐進(jìn).基于MTM總線的測(cè)試系統(tǒng)設(shè)計(jì)方法[J].計(jì)量與測(cè)試技術(shù), 2009, 36(2):27-33.MENG Xiao-feng, ZHONG Bo, XU Jin.Design of testing system based on MTM bus[J].Metrology and Measurement Technique,2009, 36(2):27-33.

[5]盧上丁,雷加,黃新,等.MTM總線模塊間通信體系的研究與應(yīng)用[J].計(jì)算機(jī)工程, 2010, 36(3):254-259.LU Shang-ding,LEI Jia,HUANG Xin,et al.Research and application of communication system between modules in MTM-bus[J].Computer Engineering,2010,36(3):254-259.

[6]陳星,黃考利,連光耀,等.基于Verilog HDL的MTM總線主模塊有限狀態(tài)機(jī)設(shè)計(jì)[J].計(jì)算機(jī)測(cè)量與控制,2010,18(3):682-684.C HEN Xing,H UANG Kao-li,L IAN Guang-yao,et al.Design of MTM bus master modules finite state machine based on Verilog HDL[J].Computer Measurement and Control,2010,18(3):682-684.