基于DSP+FPGA的磁鐵電源控制器的設計

瞿 盛,龐科旺

(江蘇科技大學 電子信息學院,江蘇 鎮江 212003)

磁鐵電源大多作為電源中的一種特種電源被廣泛應用于加速器、質譜儀等設備,為磁鐵提供特定的勵磁電流以產生所需的磁場,對磁鐵電源的基本要求來源于磁場特性,因此基于數字化電源控制器的磁鐵電源為輸出高精度的穩定勵磁電流,以獲得符合運行模式的穩定磁場結構提供了重要保證[1-2]。文中介紹的磁鐵電源控制器采用DSP和FPGA的雙CPU結構,采用FPGA控制高精度模數轉換器AD7679進行采樣,通過DSP的SPI接口把采集到的數據送給DSP;由DSP運算處理后輸出用來控制磁鐵電源的帶有死區的PWM波形。

1 控制器總體結構

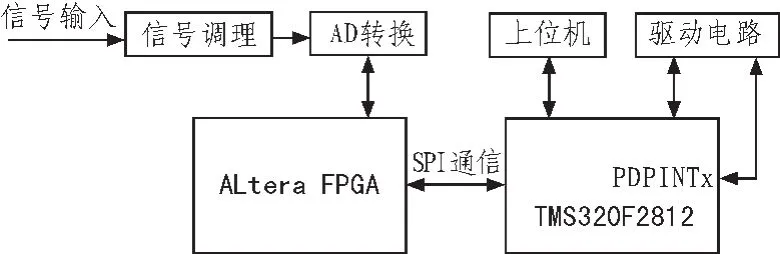

控制器采用DSP TMS320F2812為數字處理輸出模塊,以Altera公司的CycloneⅢ系列FPGA控制前端AD進行數據采集,數據傳輸部分由FPGA與DSP的SPI接口完成。通過DSP的SCI串口與上位機實現通訊,顯示并控制電源的運行狀態,后端的驅動電路中實現主電路和驅動電路的隔離。控制器總體結構框圖如圖1所示。

2 硬件電路設計

2.1 信號調理電路

圖1 控制器總體結構框圖Fig.1 Structure diagram of the magnet power supply controller

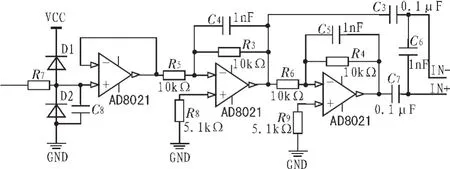

信號調理電路的主要作用是實現信號的放大和低通濾波。因為要保證將AD轉換器的采集信號限制在0~+5 V之間,為防止大電流信號時產生過高的輸入電壓會損壞A/D端口,設計了電平限制保護電路。AD轉換器輸入采用差分輸入方式,將單端信號轉換為差分信號,實現比例放大,有效的濾除了高頻噪聲,便于AD對輸入信號的高精度采集。圖2為信號限幅、隔離、濾波和放大電路。

圖2 信號調理電路Fig.2 Signal conditioning circuit

2.2 FPGA對AD的控制

本設計采用的AD7679是18位電荷分配的完全差分逐次逼近型模數轉換器,具有570 ksps的采樣速率,同時可以與5 V或3 V的數字邏輯電平兼容。為防止采樣點在開關脈沖之上,系統出現振蕩,可以使DSP在發出開關脈沖的同時給FPGA一個同步信號,作適當延時,等信號的尖峰脈沖消失后,FPGA再給ADC發出采樣命令。AD操作分為空閑、開始AD轉換、等待AD轉換、讀AD轉換結果4個狀態。在CONVST信號的下降沿后,開啟轉換過程,BUSY會自動置1,保持轉換。當BUSY信號變為低電平,CONVST保持高電平時,AD7679處于數據采集階段。FPGA對AD的控制如圖3所示,實際的電路中,FPGA和AD轉換器之間加入四通道的磁隔離器件ADuM1412進行數據隔離。

圖3 FPGA對AD的控制及FPGA與DSP的通信電路Fig.3 DSP control of the AD and circuit of communication between DSP and FPGA

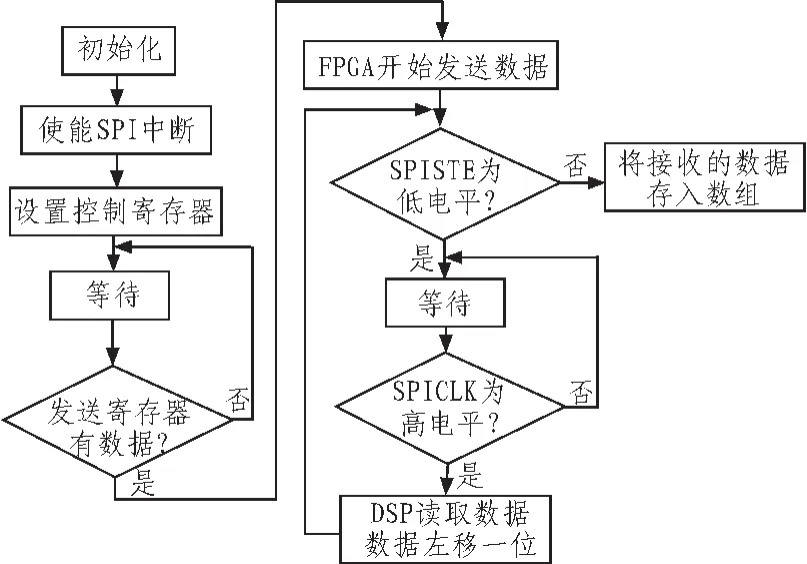

2.3 DSP與FPGA間的通信

TMS320F2812內部帶有一個SPI接口,通過定義控制寄存器,設置DSP為主設備,為通信提供時鐘信號,FPGA作為從設備。由于DSP和FPGA的I/O口引腳電壓相匹配(3.3 V),所以不需要電平轉換電路。設置FPGA在時鐘脈沖上升沿時發送數據,在下降沿時接收數據。由于FPGA發送的數據時總是將最高位的數據移出,接著將剩余的數據分別左移一位,所以DSP將接收到的數據逐位左移實現數據接收。當SPISTE引腳為低電平時,FPGA逐位發送數據;當SPICLK引腳為高電平時,DSP逐位讀取數據,并且左移一位后等待下一次SPICLK為高電平,當SPISTE為高電平時,則DSP已經接收完FPGA發送的數據,經過8個時鐘脈沖后,完成一次SPI時序,DSP將接收到的數據存儲到已經定義的數組中。DSP與FPGA通信引腳連接如圖3所示。

2.4 驅動電路的設計

圖4的驅動電路中高速光耦HCPL-4503快速實現信號的轉換和隔離,而故障信號經低速光耦TLP521-1隔離后送至PDPINTx引腳,PWM輸出引腳變為高阻態,同時產生一個中斷,封鎖驅動信號,關閉功率開關管。

3 控制器軟件設計

當發生中斷時,DSP的CPU會根據中斷響應的優先級和中斷向量表判斷,跳至相應的子程序執行,實現各自的功能。圖5為主程序的流程圖。

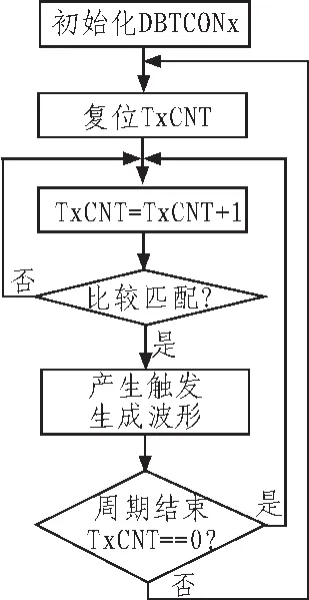

為防止上下兩橋臂開關器件同時導通,驅動波形需要具有一定的死區時間。設置DSP死區控制寄存器DBTCONx[8-11]位死區定時器周期為m,DBTCON[2-4]位的死區定時器預定標因子為x/p,若通用定時器時鐘周期為t,則死區時間tS=m*p*t[6]。死區部分控制流程如圖6所示。

圖4 后端驅動電路Fig.4 Backend driving circuit

圖5 主程序流程圖Fig.5 Flow chart of main program

圖6 死區部分控制流程Fig.6 Control-flowchart of dead zone

圖7為DSP和FPGA之間的通信流程。波特率的配置通過對DSP的SPIBRR寄存器的編程實現,在SPI接口設計時應注意使用系統時鐘對SCLK信號進行同步以減少SCLK引起的通信錯誤。

4 結束語

采用DSP+FPGA架構的磁鐵電源控制器兼有兩種信號處理芯片的優越性,有效的提高了運算速度和精度。在后續的研究中根據需要設置相應參數,選擇合適的控制算法,以滿足磁鐵電源輸出極低紋波和受精確控制的電流。

圖7 DSP與FPGA之間的通信流程Fig.7 Flowchart of SPIcommunication between DSP and FPGA

[1]馬紅霞,燕偉康,趙升.一種高穩定度軟開關加速器磁鐵穩流電源[J].電氣傳動自動化,2009,31(3):32-34.MA Hong-xia,YAN Wei-kang,ZHAO Sheng.A magnet stabilized-current supply of high-stability soft switch accelerator[J].Electric Drive Automation,2009,31(3):32-34.

[2]趙久籍,尹兆升.粒子加速器技術[M].北京:高等教育出版社,2006.

[3]李夕紅.基于DSP和FPGA的數字化開關電源的實用化研究[D].成都:成都理工大學,2008

[4]劉勇,祝忠明,羅文淵,等.基于FPGA+DSP的高精度數字電源數據采集系統設計[J].電子元器件應用,2009,11(1):25-27.LIU Yong,ZHU Zhong-ming,LUO Wen-yuan, et al.Design of high-precision digital power data collecting system based on FPGA+DSP [J].Electronic Components Applications,2009,11(3):25-27.

[5]劉鵬鵬,王晶,尹小杰,等.基于DSP和FPGA的通用控制器的設計[J].電子設計工程,2011,19(21):170-172.LIU Peng-peng,WANG Jing,YIN Xiao-jie, et al.Design of a genrral motion controller based on DSP and FPGA[J].Electronic Design Engineering,2011,19(21):170-172.

[6]顧衛鋼.手把手教你學DSP—基于TMS320X281X[M].北京:北京航空航天大學出版社,2010.