基于壓縮感知的低功耗高效率CMOS圖像傳感器設計*

趙士彬,姚素英,徐江濤

(天津大學電子信息工程學院,天津 300072)

CMOS 圖像傳感器(CMOS Image Sensor,CIS)以其單片集成、低功耗、體積小等特點,逐漸成為圖像和視頻采集的主流器件[1-3]。在現有圖像視頻采集處理系統中,圖像傳感器和圖像壓縮處理器往往彼此分離,部分傳感器輸出數據消耗了大量的功耗和帶寬,卻被壓縮處理器過程舍棄,這將降低了系統整體功耗和帶寬效率,限制其應用于圖像視頻無線傳感網等需要低功耗且帶寬壓力較高的領域[4-5]。

近年來,壓縮感知(Compressive Sensing)方法逐漸被引入到CIS的設計中,其設計思想核心在于借助CIS的單片集成特性將數據壓縮過程集成于圖像傳感過程中,從源頭削減舍棄圖像的產生。Chi Y M等人將全部圖像舍棄判別模塊集成于像素級[6-8],Viktor Gruev等人則通過增加輸出總線和時序優化等手段將圖像儲存、幀差求解和閾值判別等模塊分別集成在像素級和列級[9-10],然而,這兩種方法均無法兼顧像素面積、填充因子、固定模式噪聲、靈敏度、圖像儲存精度和功耗等CIS關鍵指標。此外,上述方法一般采用基于圖像舍棄標志位(Abandoned Flag Bit,AFB)的事件地址表示法[11](Address Event Representation,AER)讀出像素陣列的模擬輸出,既無法與現有的片上圖像信號處理(Image Signal Processing,ISP)相兼容,也缺乏針對集成ADC的更深層次的功耗和效率優化。

為克服上述不足,本文提出了一種基于列總線復用的像素結構設計,其可以通過較小尺寸的像素面積和較低的功耗,同時兼顧像素感光靈敏度和數據儲存精度。此外,提出了一種兼容于流水線型芯片級ADC結構的自適應讀出量化方法,通過AFB的流水化實現了對舍棄和非舍棄圖像的選擇化處理。

1 壓縮感知CIS的設計方法學

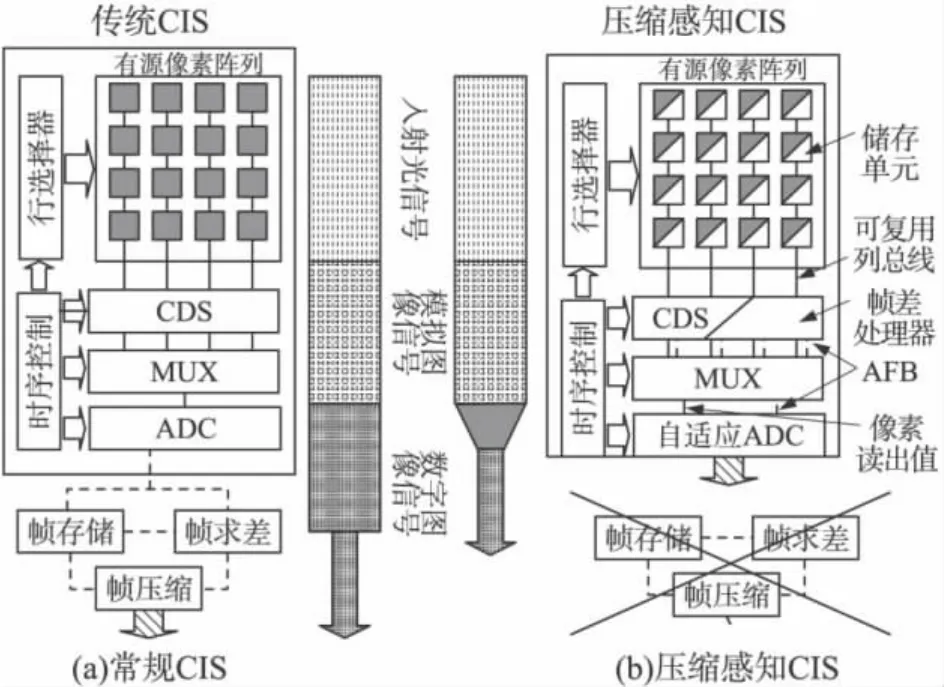

傳統CIS的結構和工作流程如圖1(a)所示。首先,像素陣列中的有源像素(Active Pixel Sensor,APS)在時序控制電路和行譯碼器的作用下進行復位和曝光以采樣光信號。隨后,像素復位信號和曝光信號通過相關雙采樣(CorrelativeDouble Sampling,CDS)和多路選擇器(MUX)等信號調理和尋址電路形成像素讀出值。其值經過集成ADC的量化后最終以幀為單位傳送到ISP形成數字圖像信號。ISP將相鄰獲取的本幀信號和儲存在幀存儲器中的參考幀信號進行求差處理,并將結果與設定的閾值比較以確定兩幀之間未發生實質變化的像素數據為舍棄數據。最終,非舍棄數據將進行編碼并得以儲存。在上述過程中,無論是傳感器對舍棄數據的感知還是壓縮處理器對舍棄數據的壓縮,都將消耗無謂的功耗、帶寬和儲存空間,最終阻礙圖像采集處理系統效率的提升。

圖1 兩種圖像傳感器工作流程對比圖

產生上述問題的根源在于傳統圖像傳感器缺乏自我計算、識別和消除圖像舍棄數據的能力,因此突破上述瓶頸的關鍵在于提高CIS的處理不同類型數據的智能性。易于單片集成是CIS最重要的優勢,這就為在像素陣列內部集成儲存單元提供了可行性。這種存儲單元可以在不影響本幀圖像感知的條件下保持并輸出前幀圖像感知信號,并通過像素級或列級集成的處理電路實現兩幀圖像的求差和閾值比較,獲取像素讀出值對應的舍棄標志位。更為重要的是,這些標志位可以用來進一步增強片上集成ADC的智能性,使其具有對不同類型的模擬圖像信號具有選擇性處理能力。

總之,這種新的圖像傳感過程是一種典型的壓縮傳感(Compressive Sensing,CS)過程。對于新的傳感器結構而言,舍棄數據是“不可見的”,因此,也就無需在ISP中設置類似于傳統CIS的片上圖像壓縮處理單元。這種將圖像的壓縮過程與傳感過程相集成的設計方法學可以從源頭削減舍棄數據,加強了感知和壓縮的協同性,有效突破了傳統CIS的效率瓶頸。

2 壓縮感知CIS的電路結構

根據上述設計思想,我們提出一種壓縮感知CIS結構,如圖1(b)所示。其主要由像素級電路、列級電路和芯片級電路組成:

(1)像素級電路包含兩部分:常規的有源像素和集成于像素中的存儲單元,分別完成本幀光信號的采集和前幀光信號的儲存記憶。兩者通過共享的輸出總線與列級電路相連。

(2)列級電路主要由常規的相關雙采樣(Correlated Double Sample,CDS)電路和列集成幀差處理器(Frame Difference Processor,FDP),分別用于讀出信號消噪和舍棄標志位(Abandoned Flag Bits,AFB)的生成。此二者同樣共享列總線,并經由多路選擇器MUX分別將像素讀出值和AFB輸出到芯片級模擬和數字總線上。

(3)芯片級電路主要由基于自適應量化的流水線ADC組成,其可以同時采樣像素讀出值和AFB信號,且每級流水線均可根據AFB狀態在壓縮模式和量化模式之間進行切換,因此,可以保證非舍棄數據的量化和舍棄數據的壓縮可同時進行而互不干擾。

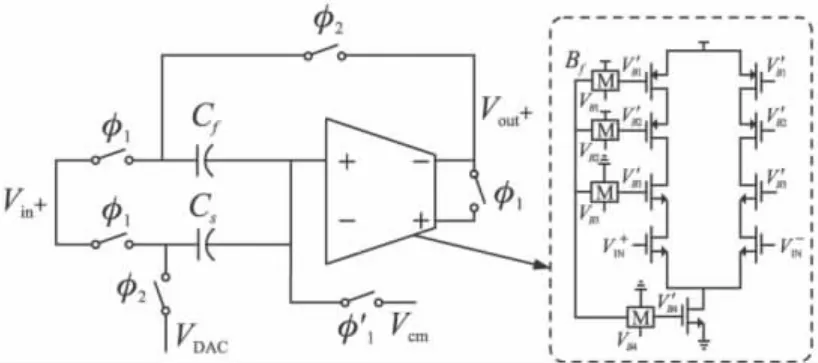

2.1 基于輸出總線復用的有源像素及其儲存單元

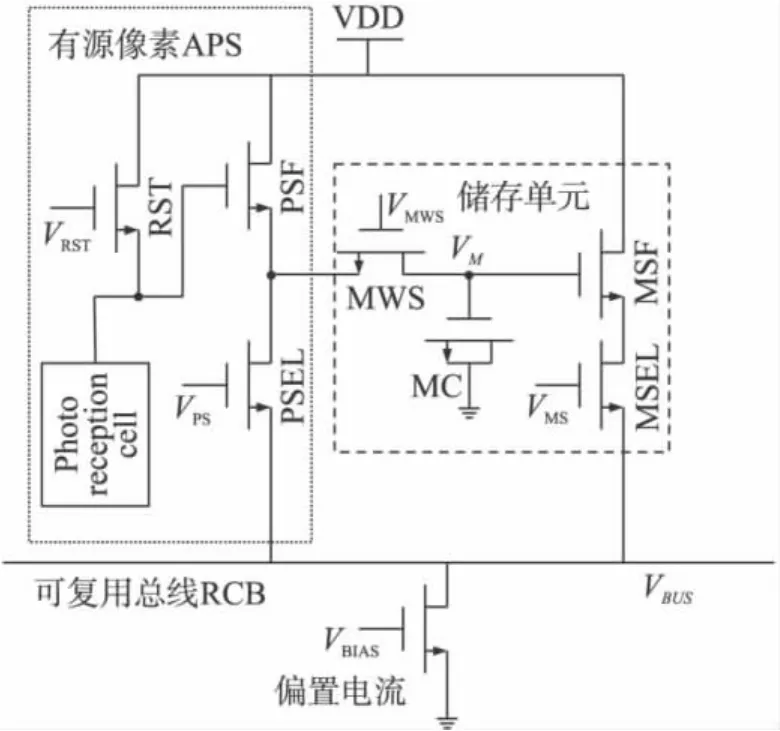

基于輸出總線復用的有源像素及其儲存單元結構如圖2所示。其中復位管RST、源級跟隨器PSF、選通管PSEL和感光單元(Photoreception Cell,PRC)組成有源像素APS,而存儲寫開關MWS、儲存電容MC、源級跟隨器MSF、選通管MSEL構成儲存單元.這兩者以PSF源級和可復用總線(Reused Column Bus,RCB)為端口互相連接,并共享列輸出偏置BIAS。

圖2 集成儲存單元的像素結構圖

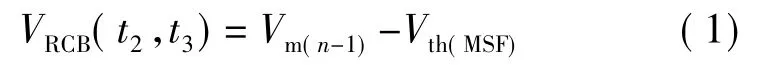

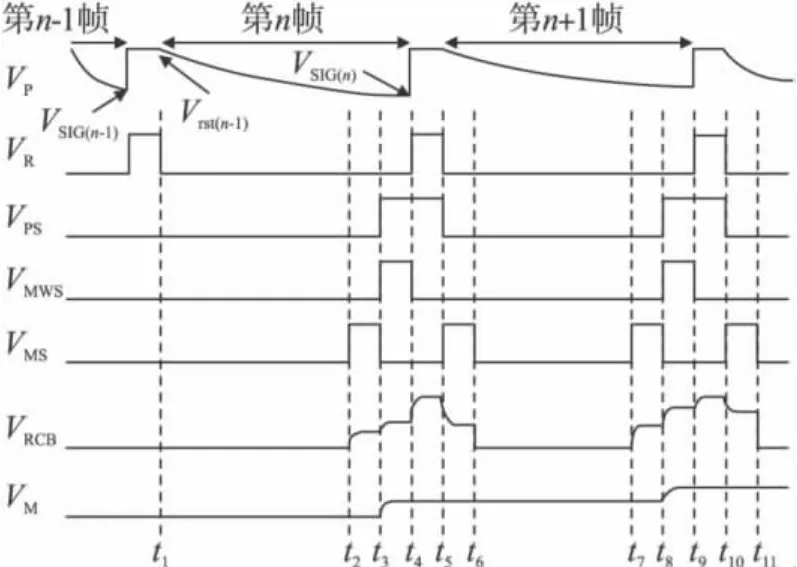

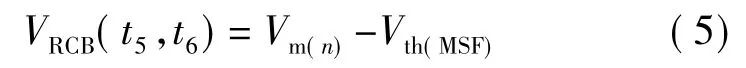

上述結構工作時序如圖3所示。假設先后經歷第n和n+1幀曝光,且后者光強大于前者。首先,在t1時刻,復位信號Vr下降,像素開始第n幀的曝光過程,正如下文分析所示,此時MC的柵極電壓Vm正比例于第n-1幀曝光信號Vsig(n-1)。到t2時刻,存儲單元選通信號Vms先于像素單元選通信號Vps變為高,此時 MSEL 被打開,Vm(n-1)經 MSF 緩沖讀出到RCB上,此時RCB電壓表達式為:

其中Vth(MSF)為MSF閾值電壓,其值在不同像素之間存在差異,并構成主要的固定模式噪聲(Fixed Pattern Noise,FPN)。待FDP對此RCB電壓完成采樣后,MSEL關斷,PSEL開啟,t1至t3時間內第n幀曝光信號經PSF緩沖讀出到RCB上,其表達式為:

與此同時,Vmws置高將MWS打開,MC電壓被更新為VRCB(t3,t4),待刷新完成后,MWS 斷開,Vr升高開啟RST管完成RPC的復位,此時RCB電壓表達式為:

在t3至t5時間段內,CDS電路采樣上述兩信號,并求差形成第n幀像素讀出信號Vread(n),其表達式為:

圖3 集成儲存單元像素工作時序圖

上述采樣完成后,PSEL在t5時關斷使得RCB處于空閑狀態,此時像素操作類似于前述t2時刻,Vms再次升高,將此時的Vm(n)輸出到RCB上,此時RCB電壓表達式為:

此時,FDP采樣此信號,并與先前完成采樣的VRCB(t5,t6)進行求差處理。假設不考慮隨機噪聲的影響,其兩幀復位電壓可以認為相等,則求差的結果可以代表幀差信號,其表達式為:

顯而易見,上述幀差信號中并不含有MSF或PSF的閾值電壓,這意味著幀差信號和經CDS產生的像素讀出值一樣同樣不會受到FPN的影響。上述時序設計同樣適用于從t5到t11的n+1幀的操作過程。

上述CDS和FDP電路的細節描述已經發表在我們先前的論文[12-13]中。其CDS結構不僅可以消除像素級FPN,而且可以消除列級FPN,且芯片占用面積小,可以為FDP電路的列級集成提供足夠空間。與其他整體在像素級集成的方案相比,所采用的FDP在電路面積方面的限制大大降低,更為復雜和精確的檢測電路結構可以被采用。通過上述兩模塊的操作,高精度低FPN的像素讀出值和AFB最終可以被儲存在列級。在MUX的尋址選通下,這兩個信號分別被輸出到全局模擬和數字總線上,供芯片級自適應ADC使用。

從上述分析可以看出,所提出的像素結構與其他相類似的方案相比[6-12],主要具有以下兩個優點:

(1)列總線復用一方面使得儲存單元的讀出無需額外增加偏置電流,可有效降低CIS陣列工作所需功耗;另一方面,也可以保證相鄰兩幀的曝光信號可以從同一個源級跟隨器緩沖讀出,有效避免FPN對于幀差檢測的干擾。

(2)由于存儲單元與感光單元完全隔離,二者可以根據其各自特性分別進行優化以期獲得更加良好的折衷性。例如,儲存電容可以增大以避免寄生二極管泄漏電流的影響,與此同時,PRC中的感測電容則可以減小,以期獲得更高的感光靈敏度。

2.2 基于芯片級流水線ADC的自適應讀出量化方法

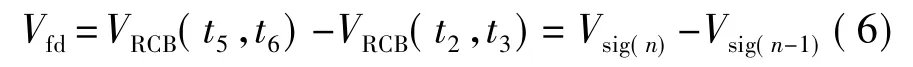

單片集成ADC進行讀出信號的片上量化是CIS超越CCD傳感器的主要特點之一,CIS集成ADC按其集成位置可分為像素級ADC、列級ADC和芯片級ADC三種。相比前兩者,芯片級ADC可以被全陣列共享,對列FPN沒有影響,且通過流水線處理其總體占用功耗較低,正在逐漸成為低功耗高分辨率CIS集成ADC的主流選擇[14-15]。對應于前述像素讀出值及其相應的舍棄標志位,壓縮感知CIS集成ADC需要兩種工作模式:正常模式與常規ADC操作相同,完成對非舍棄讀出信號的正常量化;壓縮模式則需要完成對舍棄數據的消減,同時避免處理舍棄信號所消耗的無用功耗。由于舍棄和非舍棄數據往往相互雜糅,上述兩模式相互切換所需時間必須盡可能的短,以便減小互擾,即實現模式切換的“無縫化”。然而,常規流水線ADC的處理延遲使得同一時刻各級處理數據并不屬于同一個像素讀出值,以流水線ADC為整體進行模式切換必然造成舍棄和非舍棄數據處理的相互干擾,無法滿足“無縫化”的要求。因此,需要對常規流水線ADC進行電路設計及其相關時序操作的調整,使得各個流水級在獨立的模式切換控制信號作用下進行相應的電路操作,根據待量化信號的類型進行自適應量化處理,其基本結構如圖4所示。

圖4 基于芯片級流水線ADC的自適應讀出量化結構圖

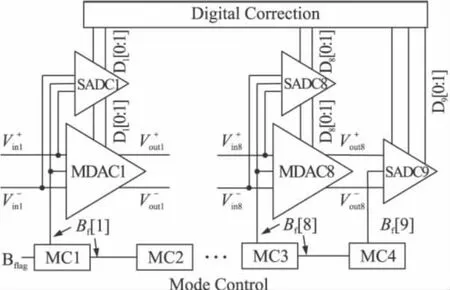

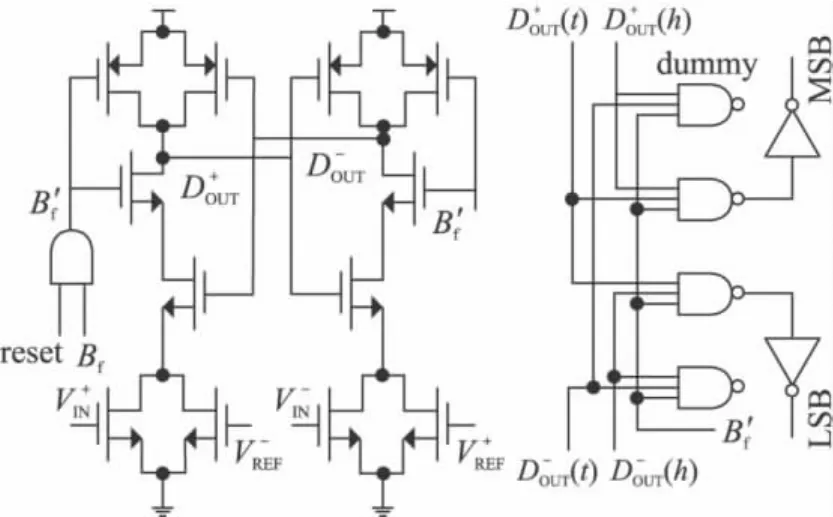

2.2.1 面向流水線級模式控制的電路設計改進

流水線型ADC對于信號量化最為重要的兩個核心模塊是MDAC中的開關電容放大器和Sub-ADC(SADC)中的動態比較器。前者通過采樣保持過程實現量化信號的調理和級間傳遞,決定了信號流水線操作的量化精度,且是功耗消耗的主要部分;后者則在采樣保持時鐘作用下完成信號和內建閾值電壓的比較,是產生量化輸出的主要單元。因此,面向兩種模式的電路設計改進也主要針對這二者進行:

圖5 MDAC結構示意圖

(1)MDAC的調整主要針對運放放大器的偏置電壓產生,如圖5所示,當Bf信號為高時,雙向選通開關M將放大器除輸入對管外的其他待偏置MOS管柵極接通到對應得偏置電路電壓輸出信號上,放大器偏置正常,進入正常模式;反之,M將這些柵極接通到對應的電源線上(PMOS為VDD,NMOS為GND),放大器無法正常偏置靜態電流,進入壓縮模式。雙向選通開關M的主要作用在于隔離偏置電壓輸出信號線和待偏置MOS管柵極,避免了從壓縮模式到正常工作模式切換時由于偏置電壓的重新建立延長切換所需時間。

(2)動態比較器及DAC由于不包含靜態電流,因此其調整主要針對工作時序。當Bf信號為高時,常規的復位信號reset可以正常通過與門對比較器和DAC施加作用,此時兩電路均工作在正常模式;當Bf信號為低時,Bf信號將reset信號屏蔽,一方面將比較器保持在復位狀態,減小其輸出電壓翻轉帶來的動態功耗耗損,另一方面將DAC的輸出進行置位,使每級輸出的MSB和LSB始終都保持為0。

圖6 SADC結構示意圖

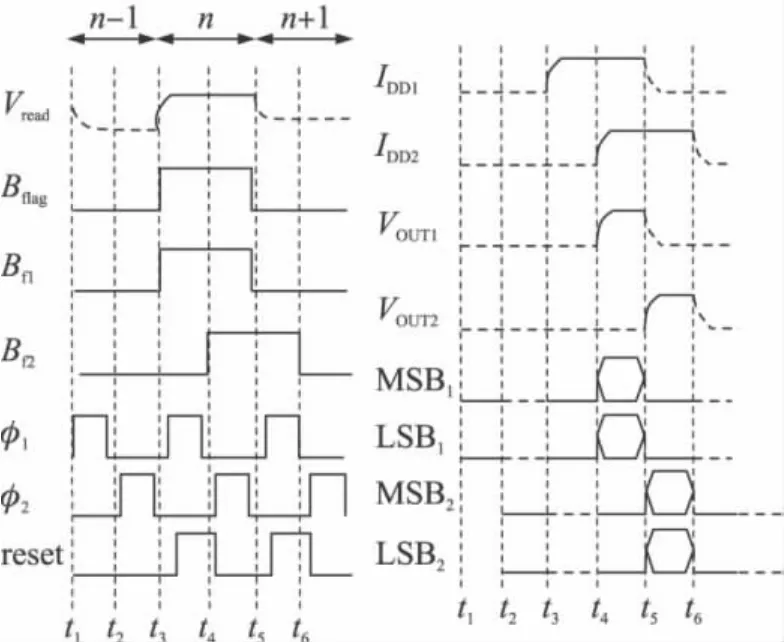

2.2.2 面向流水線級模式控制的控制時序設計

根據前述分析,常規流水線ADC無法以整體進行模式切換的主要原因在于流水線操作自身的延遲。因此,實現各級獨立的模式切換關鍵在于舍棄標志位也要同步于其對應像素讀出值的處理在流水線級間進行傳遞,即各級模式控制模塊(Mode Control,MC)對舍棄標志位的采樣同樣采用類似于ADC的流水線處理。首先,MC的控制時鐘周期必須與采樣保持時鐘周期保持相等。其次,后級MC對前級的采樣點應選擇在前級MDAC保持放大而本級MDAC采樣的時刻,為了簡化起見,下面以流水線前兩級處理第n-1,n和n+1次像素讀出值的電路操作和時序關系為例進行對選擇此時刻作為采樣點進行說明。

圖7 Bf信號時序延遲示意圖

(1)t1~t2時間內,MDAC1和MC1分別對第n-1個像素讀出值及其對應的舍棄標志位Bflag(其值為0)進行采樣,輸出第一級模式控制信號Bf1為0。此時MDAC1將進入壓縮模式,運算放大器在Bf1的作用下關斷所有的柵極信號,即將其靜態直流電流IDD1置零。SADC中的比較器完成相應復位操作。

(2)t2~t3時間內,Bf1信號保持0,仍處于壓縮狀態的MDAC1無法對前述采樣值進行余數求差,且reset信號同時仍被Bf1信號所屏蔽,比較器仍然處于復位工作狀態,對應的MSB1和LSB1輸出均為0。至此,第一級流水線級完成了對第n-1個像素讀出值的壓縮處理。然而,Bf1此時所代表的舍棄標志位必須傳遞到下一級模式控制模塊MC1中,才能最終使得整個ADC實現對此數據的壓縮處理。因此,在t2時刻,MC2對Bf1進行采樣形成Bf2,舍棄標志位0傳遞到第二級流水線,t2~t3時間內的MDAC2的工作過程類似于t1~t2時間內的MDAC1,同樣對第n-1個像素值保持了壓縮模式的處理。

(3)t3~t4時間內,MDAC1和MC1繼續對第n個讀出值和舍棄標志位進行采樣,此時第n個讀出值為非舍棄數據,對應采樣后的Bf1為高,MDAC1此時將進入正常模式,運算放大器的柵極重新與偏置電壓相連,IDD1恢復到正常水平。而此時MDAC2和SADC2在Bf2的控制下仍工作在壓縮模式,類似于t2~t3時間內的MDAC1和SADC1,仍保持低功耗和無量化數據輸出的狀態,實現了第二級流水線隊第n-1個像素值的壓縮操作。

(4)t4~t5時間內,Bf1仍為高,MDAC1和SADC1均保持正常模式,余數求差得以正常進行,并將求差結果輸出到Vout1總線上供后續流水線級進行采樣;Bf1信號也解除了對Reset信號的屏蔽作用,SADC也可以完成對非舍棄數據的量化操作,MSB1和LSB1為有效值,第一級流水線級完成了對第n個像素讀出值的正常量化轉換;在t4時刻,MC2再次對Bf1進行采樣,Bf2置高,第n個讀出值的舍棄標志位傳遞到Bf2上,t4~t5時間內的MDAC2和SADC2的工作過程類似于t3~t4時間內的MDAC1和SADC1,同樣對非舍棄信號保持了正常模式的處理。

可以看出,上述電路操作過程同樣適用于t4至t7時間內從非舍棄數據n到舍棄數據n-1的模式切換,這里不再贅語。綜上所述,通過上述電路設計改進和相應的控制時序設計,在類似于t3~t4和t5~t6這樣舍棄數據和非舍棄數據的過渡期,各流水線級可以獨立根據各自的控制信號進行相應模式的電路操作,通過進一步的優化設計,切換時間基本可以保證不干擾切換后模式的正常作用,完全滿足了壓縮感知CIS集成化ADC的要求。

3 芯片測試結果

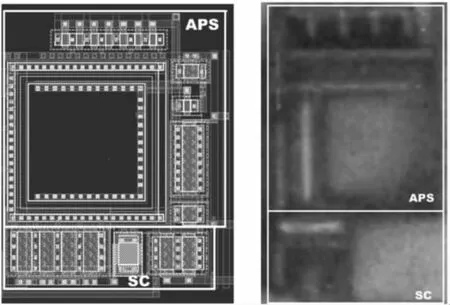

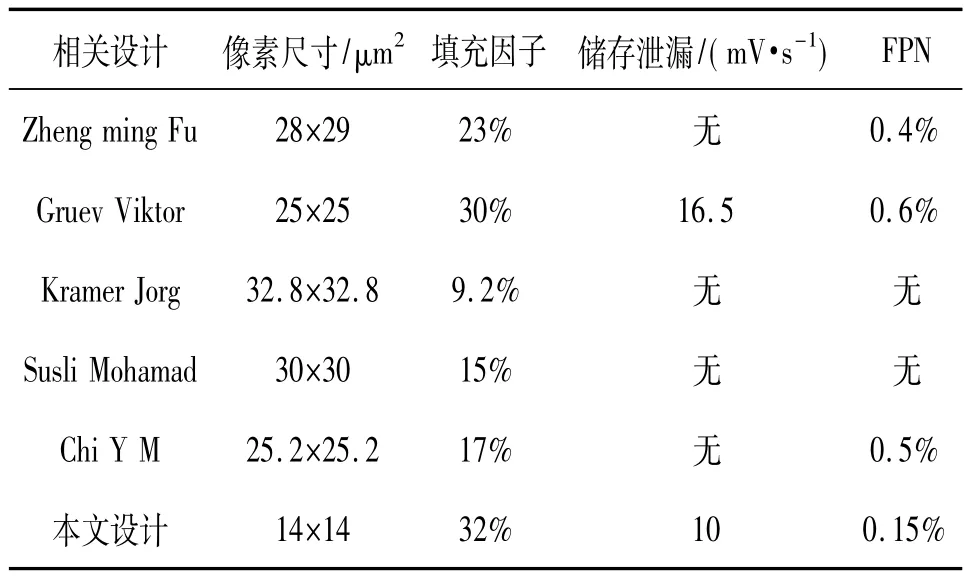

上述壓縮感知CIS已利用Global Foundry 0.18 μm Dual Gate Mixed-Signal Process進行了物理設計和投片驗證。圖8為基于輸出總線復用的有源像素及其儲存單元的版圖和芯片照片,有源像素APS和儲存單元SC標注如圖所示,其主要指標與其他已發表設計的對比如表1所示。結果顯示本文所提出的基于總線復用的有源像素APS集成儲存單元SC的方案可以在保持較高的填充因子的條件下有效降低像素尺寸,并且可以通過金屬掩蔽、增大柵電容、優化源漏面積等方法進一步降低儲存單元的泄漏電流水平。總線的復用時序也使得像素讀出值和幀差值都可以避免FPN的影響,從而從整體上降低了FPN的影響。

圖8 有源像素及其儲存單元版圖設計和芯片照片

表1 基于總線復用的像素設計和相關已發表設計特性對比表

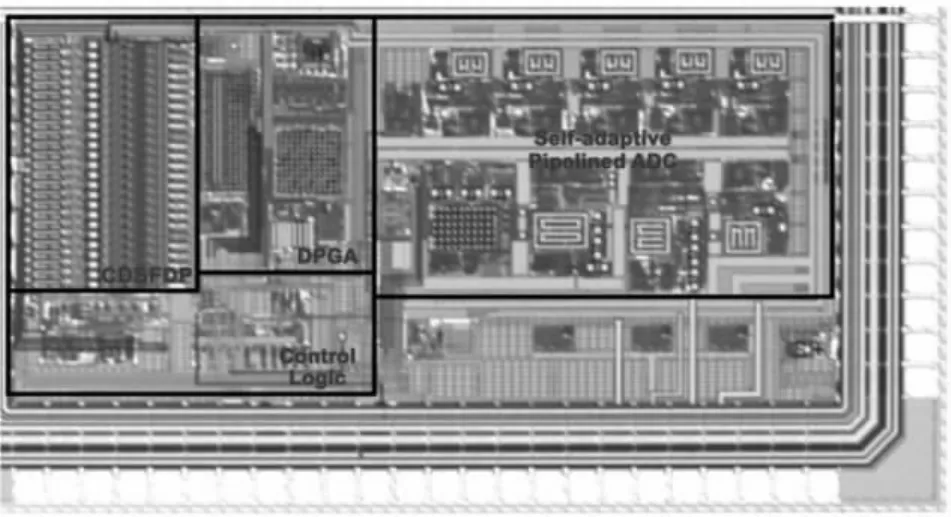

圖9為列級和芯片級電路的版圖照片,在電路設計中加入了數字可編程增益放大器(Digital Programmable Gain Amplifier,DPGA)用于調節 CDS 電路輸出的像素讀出值幅度,并對控制邏輯部分(Control Logic)進行了調整使其可以通過外部時序控制將AFB與自適應流水線ADC(Self-adaptive pipelined ADC)相隔絕,并控制ADC在整個量化過程中完全處于正常模式或壓縮模式,因而增強了測試方案的靈活性。

圖9 列級和芯片級電路的版圖照片

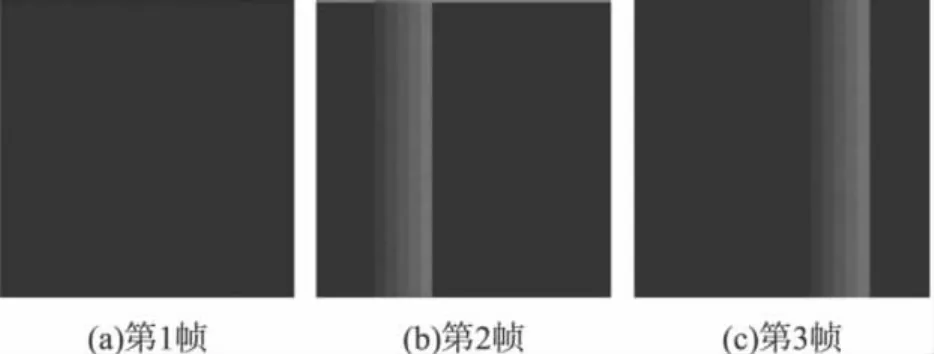

整體測試方案分3幀進行:第1幀作為參考幀,通過邏輯控制模塊隔離ADC與AFB,并將ADC始終置于正常工作模式,此時對應的像素陣列的光輸入為無光照的黑暗背景;隨后,令一條格光源自左向右運動至像素陣列和黑暗背景之間,先后完成第2幀和第3幀采樣,此時邏輯控制模塊去除AFB和ADC的阻隔信號,開始自適應讀出量化過程。

圖10 條格光源幀間運動測試結果

最終的3幀圖像輸出結果如圖10所示。其中,圖10(a)為第1幀參考幀,由于像素陣列和讀出量化電路均工作在正常狀態,像素KTC噪聲和閃爍噪聲等隨機噪聲使得無光照的黑暗背景存在一定程度的噪聲影響;圖10(b)為第2幀圖像,此時自適應讀出機制已通過外部控制信號激活,像素陣列可以識別出已運動至陣列左側的條格光源為非舍棄數據,其余部分像素陣列的輸入仍為未變化的黑暗背景,為舍棄數據,通過觀察分析可見,條格光源區域由于自適應讀出電路處于正常模式,因此在第1幀中存在的隨機噪聲仍可見,但在其他區域由于自適應讀出電路處于壓縮工作模式,輸出的圖像灰度均為0,以無法觀察到隨機噪聲;圖10(c)為第3幀圖像,此時條格光源已經從陣列左側運動至右側,一方面第2幀中條格光源所在的像素陣列部分輸入變為黑暗背景,另一方面兩幀之間條格光源又運動至陣列右側區域代替了部分黑暗背景作為像素陣列的輸入,因此這兩部分均被識別為非舍棄數據,對應的自適應讀出電路將保持正常狀態,兩區域均可觀察到隨機噪聲的影響,而其他區域的輸入仍為未變化的黑暗背景,被識別為舍棄數據,輸出圖像灰度均為0,且無法觀察到隨機噪聲的影響。縱上所述,無論是CDS/FDP對像素信號和幀差信號的讀出處理,還是基于芯片級ADC的自適應讀出量化電路均工作正常,配合良好,符合前述壓縮感知CIS的要求。

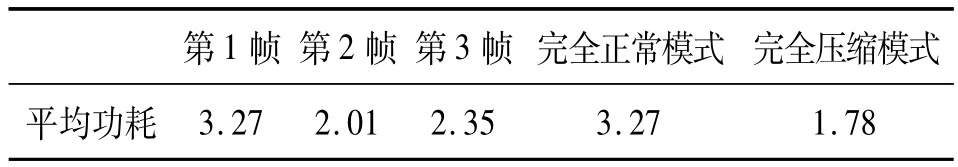

最后,分別對3幀圖像以及完全工作在正常模式和壓縮模式所對應的ADC平均功耗進行統計和計算,列表如表2所示。結果顯示第1幀即正常工作模式下功耗最高,完全壓縮模式功耗最低,約為正常值的54%;第2、3幀為正常模式和壓縮模式混雜的情況,且第3幀所含非舍棄數據多于第2幀,平均功耗相應也較高,兩者分別為正常值的61%和71%。

表2 各種工作情況下ADC平均功耗統計表 單位:mW

綜上所述,本文所提出的壓縮感知CIS在兼容傳統芯片級ADC的條件下,可以有效削減舍棄數據處理帶來的無謂功耗消耗,并完成對于舍棄數據的實時壓縮。

4 結論

本文利用基于輸出總線復用的有源像素及其儲存單元以及基于芯片級流水線ADC的自適應讀出電路,設計了一種壓縮感知CIS。理論分析和測試結果表明,其可以在兼顧像素面積、填充因子、固定模式噪聲、靈敏度、圖像儲存精度等關鍵CIS指標的前提下,同時輸出正常像素讀出值和對應的舍棄標志位,并可以利用舍棄標志位實現舍棄數據和非舍棄數據的自適應處理,有效提高了芯片的功耗效率,

實現了傳感過程和壓縮過程在CIS上的集成。結果表明,本CIS設計可適用于圖像視頻無線傳感網等需要低功耗且帶寬壓力較高的領域。

[1]Theuwissen A J P.CMOS Image Sensors:State-of-the-Art[J].Solid-State Electron,2008,52(9):1401-1406.

[2]El Gamal A,Eltoukhy H.CMOS Image Sensors[J].IEEE Circuits and Devices Magazine 2005,21(3):6-20.

[3]Bigas M,Cabruja E,Forest J,et al.Review of CMOS Image Sensors[J].Microelectronics Journal,2006,37(5):433-451.

[4]陸洲,王寶光.基于FPGA的嵌入式彩色圖像檢測系統[J].傳感技術學報,2007,20(3):618-622.

[5]王永燦,馮遠靜,俞立.基于無線視頻傳感網的高壓塔架監控系統研究[J].傳感技術學報,2008,21(12):2039-2043.

[6]Chi Y M,Mallik U,Clapp M A,et al.CMOS Camera with in-Pixel Temporal Change Detection and ADC[J].IEEE Journal of Solid-State Circuits,2007,42(10):2187-2196.

[7]Kramer J.An on/offTransientImager with Event-Driven,Asynchronous Read-out[C]//IEEE International Symposium on Circuits and Systems,Arizone,IEEE,2002:165-168.

[8]Susli M,Boussaid F,Shoushun C,et al.Efficient Event-Drivern Frame Capture for CMOS Imagers[C]//9th International Symposium on Signal Processing and Its Applications,Sharjah,IEEE,2007:1-3.

[9]Gruev V,Etienne-Cummings R.A Pipelined Temporal Difference Imager[J].IEEE Journal of Solid-State Circuits,2004,39(3):538-543.

[10]Dickinson A,Ackland B,Eid E S.A 256×256 CMOS Active Pixel Image Sensor with Motion Detection[C]//IEEE International Solid-State Circuits Conference,San Francisco,IEEE,1995:226-227.

[11]Culurciello E,Etienne-Cummings R,Boahen K.Arbitrated Address Event Representation Digital Image Sensor[C]//IEEE International Solid-State Circuits Conference,San Francisco,IEEE,2001:92-93.

[12]Zhao Shibin,Yao Suying,Xu Jiangtao,et al.Smart APS Pixel with Full Frame Self-Storage and Motion Detection Capabilities[C]//International Symposium on Photoelectronic Detection and Imaging,2009,Proc.SPIE,7384:73842R-73842R-6.

[13]Zhao Shibin,Yao Suying,Nie Kaiming,et al.Area-Efficient Low Power CMOS Image Sensor Readout Circuit with Fixed Pattern Noise Cancellation[J].Transactions of Tianjin University,2010,16(5):342-347.