自適應數字頻率計教學課題的設計

汪小會

(解放軍電子工程學院,安徽合肥 230037)

本文介紹了一種基于FPGA的自適應數字頻率計的設計方案。它以數字電子技術和可編程邏輯器件的控制原理為切入點,貫穿了數據選擇器、觸發器、計數器和鎖存器等功能器件的基本原理和應用方法。設計方案在FPGA器件上實現,采用圖形輸入方式,由數字電子技術課程介紹的基本模塊構成。

現有資料介紹自適應數字頻率計設計方法,大多采用VHDL設計[1]。但是,掌握VHDL設計要用較多時間,且本科生教學設計課題成功率較低,如果用數字邏輯電路和可編程邏輯器件FPGA設計,通常可以完成課題設計任務。

1 數字頻率計測量原理及系統框圖

數字頻率計是直接用十進制數字來顯示被測信號頻率的一種測量裝置[2]。對于非矩形波信號測量時需先進行處理,整形變換成幅度為5V的矩形波。本文討論對矩形波信號基本測量頻率為10kHz(顯示四位十進制數)和擴大10倍量程信號頻率即100kHz測量。

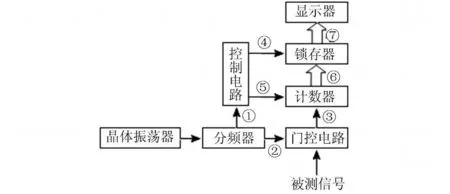

本系統由脈沖輸入電路、控制電路(由FPGA構成)和輸出顯示電路組成。控制的核心芯片是FPGA,它由兩大功能模塊組成:①頻率計數模塊,包含選通時間控制部分和計數兩個部分。②顯示模塊。如圖1所示。

該系統的工作原理是:被測信號經門控電路整形生成矩形波,輸入到控制核心芯片FPGA的計數模塊,計數器根據矩形波上升計數。計數時間則由選通時間控制電路決定,可根據頻率所處的范圍來決定檔位。最后將計數的結果給顯示電路,在數碼管上顯示頻率。

圖1 基本測頻系統總體框圖

2 電路設計方案

本課題在FPGA的開發環境QuartusⅡ中進行,學生使用邏輯符號設計方式[3]。在QuartusⅡ圖形文件編輯過程中,輸入器件型號即可調出所需器件。由于QuartusⅡ的基本元件庫幾乎囊括了所有中規模集成器件,QuartusⅡ還具有兆功能函數庫中的參數化模塊,含有所有基本數字邏輯功能器件。這些參數化功能模塊的輸入、輸出以及各種控制方式都可由用戶設定。學生的設計基本不受器件資源的限制,能夠實現真正意義上的自主設計。

1)電路實現方案

本文是以一個閘門信號低電產控制被測信號通過門控電路。通過門控的信號由計數器來統計,閘門信號一個周期內完成一次信號數量統計,同時刷新一次顯示數碼,即閘門信號選通結束時將計數器內數碼轉移到鎖存器,鎖存器內數碼作為顯示狀態。其后清除計數器內數據。故電路中需要有控制電路產生鎖存器鎖存控制信號(圖1中④)和計數器清零信號(圖1中⑤)。

2)計數器與鎖存器

計數器為同步型(10000)10進制加法計數器,鎖存器(圖1中⑥)由2片74373鎖存4片74160十六位二進制數碼組成[4]。

3)閘門信號和控制信號

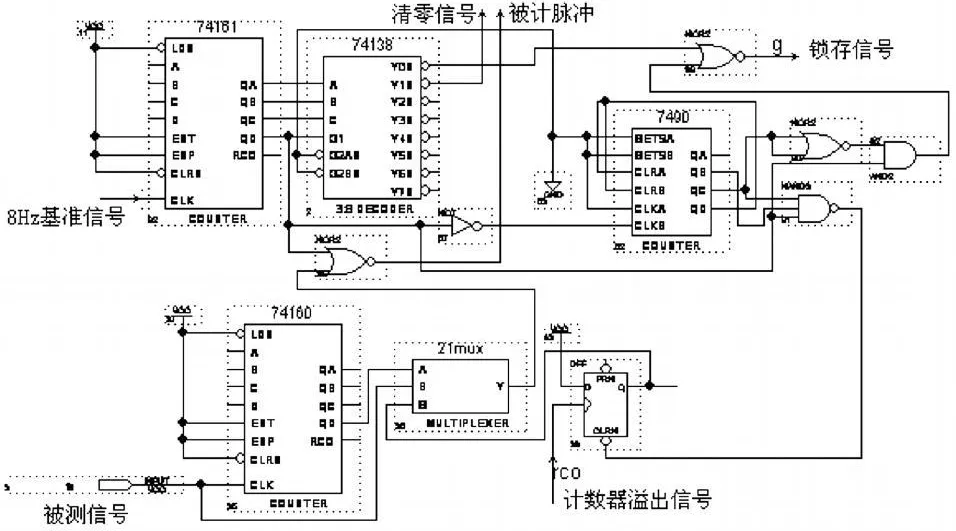

將晶體振蕩器信號分頻產生一個正脈沖或負脈沖(本文以負脈沖)寬度為1秒的信號(圖1中②)作為閘門信號(圖2中74161輸出QD)。晶體振蕩器分頻中產生另一個8Hz信號(圖1中①)作為計數器74161時鐘信號。74161輸出用74138譯碼產生鎖存控制信號g和計數器清零信號(圖2中74138輸出Y1N)。

4)溢出信號產生電路

計數器在閘門信號選通期若最高位數碼由1變0(即下降沿)就說明所測信號超出范圍,這時產生一個信號(圖2中DFF輸出Q)為1,用此信號去控制圖2的二選一數據選擇器。有溢出時將測信號十分頻(圖 2中74160)后作為待測信號,把圖 4中DFF輸出Q信號用作指示燈示意被測信號進行了十分頻,或用于控制顯示的數碼管小數點。

圖2 閘門信號和控制信號產生電路

在閘門信號選通期如有溢出在本周期內計數器統計的脈沖數目并非是實際信號數目,所以此時計數器狀態不進行鎖存即不顯示,在下一個閘門信號周期才鎖計數器狀態即顯示,再下一個周期應將溢出信號完成清除(置0)。圖2中在7490右邊電路就是為此目的設計所用。

5)更大范圍測頻設計

可將上面的計數溢出信號進行計數,判定是否溢出,其后對被測信號進行十分頻。類似進行上面處理及控制數碼管該點亮的小數點及單位符號。

最后編程下載至FPGA,經測試測量矩形波信號基本檔誤差±1Hz,擴張檔誤差±10Hz。

3 結語

本課題是筆者多年從事數字邏輯電路和可編程器件開發應用教學多個課題中一個典型代表,其綜合知識范圍廣,設計思想新穎,十分適合用于教學實驗。本課題設計是采用原理圖輸入法完成,部分模塊還可采用硬件描述語言法來做。數碼的顯示還可用動態數碼管顯示,如果這樣做可提高學生對各種知識綜合運用能力的提高。

[1] 楊剛,龍海燕.現代電子技術-VHDL與數字系統設計[M].北京:電子工業出版社,2004

[2] 黃正瑾.CPLD系統技術設計入門與應用[M].北京:電子工業出版社,2002

[3] 趙曙光.可編程邏輯器件原理、開發與應用[M].西安:西安電子科技大學出版社,2006

[4] 中國集成電路大全[M].國防工業出版社,2000