基于FPGA具有自適應功能的數據采集系統(tǒng)設計

魏海潮,李麗芳,裴峰,馬英卓,胡鵬,張謙

(中北大學信息與通信工程學院,山西太原,030051)

0 引言

在工業(yè)控制和智能測量系統(tǒng)中,一般信號的變化幅度大,若采用單一的放大增益,那么小信號經放大器放大后,幅值仍然很小,經A/D變換后,會影響數據的精度,而大信號放大后又有可能超出A/D轉換的量程,因此設計開發(fā)增益自動可調的程控增益放大器,使允許輸入的模擬量在很大的范圍內動態(tài)可調,方便與微機接口,已成為現代測控設備的必然要求,隨著可變增益放大技術的不斷發(fā)展,它在自動測控、智能測控、智能儀器儀表等重要領域的應用也越來越廣泛[1-2]。

1 系統(tǒng)框圖與結構原理

本設計系統(tǒng)完成的功能是完成對小信號的自適應算法的放大和模擬數據量化處理[2]與FPGA數據的處理。基于FPGA的自適應放大電路的設計系統(tǒng)的內容包括信號的濾波、小信號的放大、信號的采集及數據的處理。輸入的小信號經過濾波電路后送入程控放大器,程控放大器根據FPGA的信號來控制信號的放大倍數,放大器輸出的信號一路送入A/D轉換器中,一路送進電壓比較器,電壓比較器有一個基準電壓,放大器輸出的電壓與基準電壓比較后得到一個信號送到FPGA中,FPGA經計算A/D轉換后的信號與電壓比較器的信號,就可以得出控制程控放大器的放大倍數,根據以上要求分析,確定系統(tǒng)方案的系統(tǒng)硬件結構框圖如圖1所示。

圖1 系統(tǒng)框圖

2 硬件電路設計

微弱信號采集系統(tǒng)硬件電路由信號調理電路和數據采集處理模塊兩部分組成,信號調理電路主要是消除共模干擾,對微弱小信號進行放大、濾波、電壓抬升、信號傳輸;主要由前置放大器、反饋型抗混疊低通濾波器、程控放大器、電壓比較電路和A/D轉換電路構成[3-4]。數據采集處理模塊主要有FPGA芯片Cyonlc EP2C20、數據存儲和傳輸模塊構成,完成對模擬輸入信號的采樣、過采樣處理、信號振幅的計算、數字濾波和數據的傳輸。

2.1 程控放大電路設計

FPGA是新型的可編程邏輯器件,內部含有大量的門陣列,響應時間短,可以精確地控制時鐘的輸出。FPGA的處理速度很快,完全適合采集速度比較高的場合[3]。更重要的是FPGA采用系統(tǒng)可編程技術,即使整個數據采集系統(tǒng)已經投入生產,也可以根據實際情況改變系統(tǒng)的配置和功能,下載到FPGA芯片中即可完成功能的修改。

2.2 抗混疊濾波電路設計

有源濾波器不僅體積小,而且輸出阻抗和截止頻率fc無關,能夠前、后級之間相互獨立的設計。抗混疊低通濾波器具有通頻帶比較平坦,且下降快等優(yōu)點。在該系統(tǒng)的濾波器設計中,采用反饋型低通濾波器。根據“奈奎斯特采樣定律”, 在對模擬信號進行離散化時,采樣頻率f2至少應2倍于被分析的信號的最高頻率f1,即:f2≥2 f1;否則可能出現因采樣頻率不夠高,模擬信號中的高頻信號折疊到低頻段,出現虛假頻率成分的現象[5]。我們設計低通濾波器的采樣頻率為25kHz。

2.3 程控放大電路的組成

LTC6910-1是一種電壓增益數字可編程的小外形寬帶反相DC放大器。FPGA通過在G(G2、G1和G0)腳上的3位數字輸入來控制8種電壓增益選擇(0、1、2、5、10、20、50 和 100)。

自適應放大原理如圖2所示:在LTC6910放大輸出信號,其中一路信號接A/D轉換芯片的輸入端,另外一路接一個電壓比較器,電壓比較器的基準電壓為2.5V,與LTC6910放大輸出信號相比較,如果電壓比較器的輸出為1,則FPGA輸出信號控制自動增益放大器的放大倍數減小,反之,則控制自動增益放大器的放大倍數增大。

圖2 程控放大電路

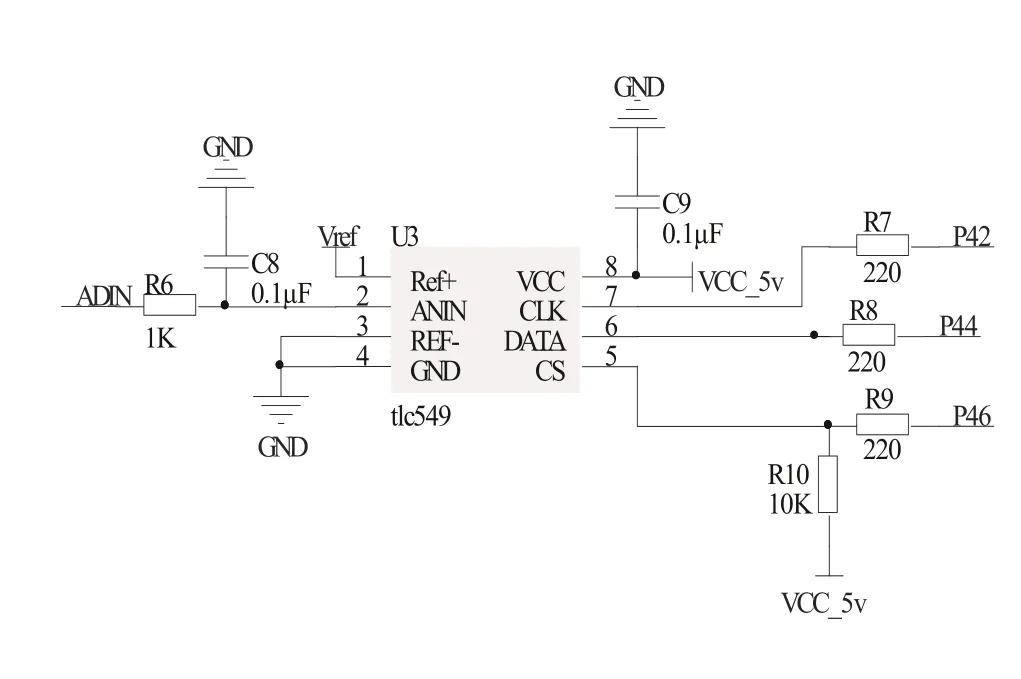

2.4 TLC549A/D采樣電路的設計

本系統(tǒng)以8位A/D轉換芯片TLC549為核心部件,它適合完成單通道8位轉換,即比較適合在速度要求不是很高的時候,組成的一種數據采集系統(tǒng)。TLC549芯片可以方便地與具有外圍串行接口控制器連接使用。按照TLC549嚴格的時序,它在完成A/D轉換后,其串行輸出的A0--A7二進制數據可由時序控制,并串行輸出到串入并出的移位寄存器。將該寄存器的8位數據與微處理器的數據總線相連,即可完成數據傳遞。由此設計的基于TLC549的數據采集電路如圖3所示。

圖3 A/D采樣電路

將圖3中的5、6、7管腳與FPGA相連接,就能實現基于數據的通信和控制。對于該電路,可從端口ADIN輸入外部模擬信號,而端口1Ref+與基準穩(wěn)壓電源相連。這樣,TLC549轉換得到的數據就可以由FPGA直接通過讀結果程序[7-8]讀出,而不需要其他硬件支持,因而可以節(jié)約硬件資源,同時也可以簡化電路的拓展。

3 系統(tǒng)實驗測試結果

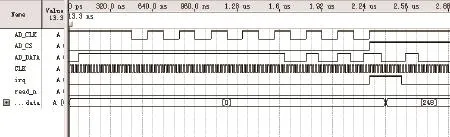

在程控放大器的設計中,是FPGA根據采集到的A/D的數據實現對程控放大器的控制的,其中FPGA對A/D的驅動時序如圖4所示。

圖4 A/D采樣驅動程序仿真

在數據采集實驗中,我們采集的信號是示波器輸出的0~2V的頻率為100kHz的正弦信號為例,通過FPGA對A/D進行500點的采樣,其中FPGA的采樣頻率為1MHz,將FPGA得到的數字信號通過MATLAB的相關處理就可以得到采樣圖像如圖5的左半部分,然后再對采樣后的圖像進行傅里葉變換就可以得到其相應的頻譜圖如圖5的右半部分,我們通過圖可以看到所設計的系統(tǒng)在100kHz時能實時的不失真的采集到輸入的數據,實現信號的自適應數據的采集。其A/D數據采樣及頻譜分析如圖5。

圖5 A/D數據采樣及頻譜分析

4 結 語

(1)所設計的系統(tǒng)能根據被測信號的振幅自動調節(jié)放大器的增益,從而自適應地完成對不同幅值振動信號的測量和處理,降低了數據采集過程中程控放大器增益的頻率,節(jié)約了CPU開銷。

(2)本系統(tǒng)的創(chuàng)新點是利用了MATLAB與FPGA共同對采集到的數據進行分析,既方便又簡單。

[1]馬建明.數據采集與處理技術[M].西安:西安交通大學出版社,2005:2-4.

[2]王云飛,王家禮,呂永生.自適應前饋微波超線性功率放大器算法研究[J].西安電子科技大學學報:自然科學版,2004,31(6):949-951.

[3]諸振勇,翁木云.FPGA設計及應用[M]. 西安:西安電了科技大學出版社,2002:124-157.

[4]田磊,汪小志,劉志剛.自適應濾波算法及應用研究[J].電子測試,2008(1).

[5]夏宇聞.Verilog數字系統(tǒng)設計教程[M]. 北京:北京航空航天大學出版社,2007:65-136.

[6]史增芳,韓艷贊.自適應相干模板法在51系列單片機中的實現[J].電子質量,2009(10):72-73.

[7]楊海燕,黃輝,張雄偉.一種改進的自適應回波抵消器的設計與實現[J].電子質量,2006(12):17-19.

[8]肖鵬韜.基于遺傳算法的RLS自適應算法研究[J].電子測試,2010(5):16-18.