陣列存儲在遙測圖像采集系統中的應用

孟令軍,彭晴晴,藺志強

(中北大學 電子測試技術國家重點實驗室,山西 太原 030051)

0 引言

隨著圖像采集器件性能的提高,圖像的采集速率和信息量也在不斷增加[1],同時,由于LVDS技術在圖像數據傳輸中的廣泛應用,圖像數據的實時處理和下傳已經成為圖像采集系統中非常關鍵的部分[2]。以SRAM陣列的存儲方式可以有效地緩解圖像數據的傳輸速率,為CPU進行圖像數據處理爭取了大量時間,并保證了穩定下傳。本文以微處理器為核心,用FPGA控制SRAM陣列進行存儲和下傳,CPU負責陣列存儲區的管理和可靠穩定的記錄數據,完成圖像數據在陣列中的分布存儲。

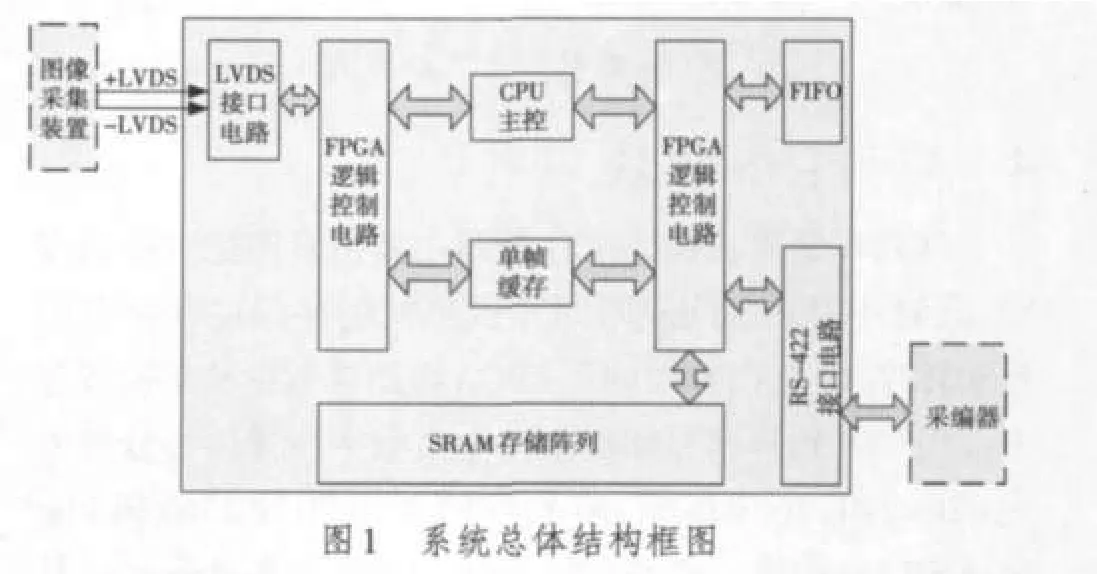

1 系統總體結構

圖像數據采集系統主要負責實時接收圖像采集裝置的高速圖像數據,同時將數據連續串行下發給采編器。本文以CPU處理器為核心,主要控制系統的總體工作流程,同時以FPGA或CPLD為輔助,完成系統各模塊與處理器之間的通信,實現圖像數據的分區存儲和連續下發。基于嵌入式處理器的圖像存儲系統硬件電路采用CPU+FPGA器件進行時序控制,遙測圖像數據首先通過LVDS接口芯片將串行數據解串為并行數據,存入單幀緩存中(由1片SRAM構成)。由于圖像數據發送速率和接收速率之間存在差距,為了保證20幅圖像數據的有效接收,主存儲器使用20片SRAM構成存儲陣列以實現20幀圖像數據的有效存儲。CPU是整個系統的中心控制器,負責控制圖像數據的接收和轉發編碼。FPGA主要負責依據CPU的控制信號接收圖像數據存至單幀緩存,轉存至存儲陣列和以PCM碼形式轉發至采編器。為了保證轉發數據的無縫傳輸,在轉發時使用FIFO進行緩存。本設計總體結構如圖1所示,主要包括7個部分:LVDS接口電路、FPGA數據處理模塊、單幀緩存讀寫模塊、CPU控制模塊、主存儲陣列、FIFO緩存模塊以及RS-422接口電路。

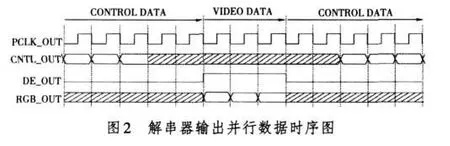

2 LVDS接口模塊

LVDS技術以其低誤碼、低功耗和高傳輸速度等優點而廣泛應用于圖像數據的高速傳輸中,可以實現一對多或者一對一傳輸[3]。本文采用點對點的數據傳輸方式,使用專門的LVDS串化/解串芯片,相同的串化/解串時鐘頻率控制,保證數據的同步傳輸。LVDS解串器完成LVDS電平到TTL電平的轉換,實現圖像幀、行同步信號與圖像數據的分離和輸出,并輸入到FPGA中進行處理。圖像數據是在幀同步信號VSYN為高電平時有效,故將幀同步信號VSYN與數據使能信號DE_IN連接,在幀同步信號VSYN有效時,解串芯片輸出DE_OUT,有效輸出16位圖像數據及控制信號。并行數據輸出時序如圖2所示。

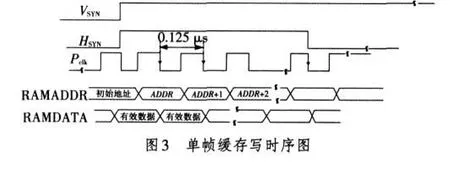

3 單幀緩存模塊

由于圖像數據傳輸速率遠大于主存儲設備的存儲速度,并且在數據轉存的同時還要對每幀圖像數據進行編碼,因此為了實現接收和轉發數據流之間的速度匹配,需要在主存儲器之前使用緩存,并且要在下一幀數據到來之前將數據轉存,以保證圖像數據的無縫緩存[4]。本文選用1片SRAM構成單幀緩存,在幀同步VSYN和行同步HSYN同時為高時,SRAM寫地址跟據PCLK的上升沿遞推,PCLK低電平時將數據寫入SRAM中緩存,時序如圖3所示。

4 陣列存儲模塊

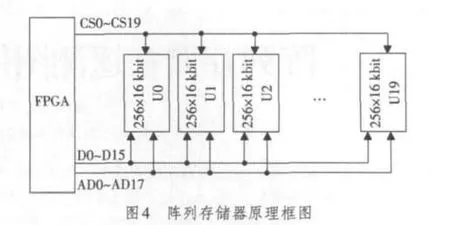

陣列存儲模塊作為主存儲器主要負責圖像數據的存儲,同時還要在幀間隔時間完成單幀緩存到主存儲器的自動轉存,即在CPU控制下FPGA將圖像數據從單幀緩存中讀出寫入到陣列存儲器中。本文數字圖像信號分辨力為320×240,16位模式;陣列存儲器由20片256×16 kbit高速SRAM構成。陣列存儲模塊的原理如圖4所示。其中共用16位數據線和18位地址線,采用獨立片選線。

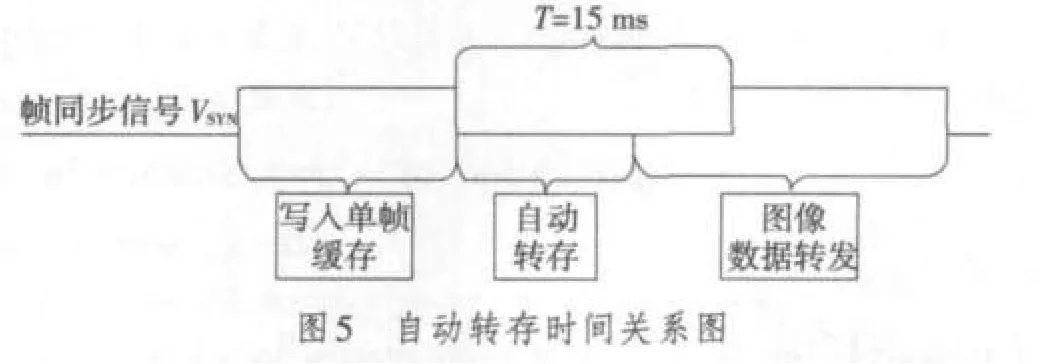

自動轉存能否成功進行是整個系統的關鍵部分。如圖5所示,兩幀間的間隔決定了自動緩存時間。圖像數據在VSYN為高時寫入單幀緩存中,為低時開始圖像數據的自動轉存。依據設計需要,兩幀間的最小間隔為15 ms,所以用于自動轉存的時間必須小于15 ms。

自動轉存一幀的圖像數據量約為(320×240×2)bit=153.6 kbit,由此可得出自動轉存最小理論頻率為[0.015/(320×240)]-1Hz≈5 MHz。實際操作時,要留有一定的后操作時間,本文確定的轉存時鐘為8 MHz,寫入陣列存儲器一幀圖像的時間約為(320×240/(8×106))s=9.6 ms。因此,根據計算有足夠的時間將單幀緩存中的圖像數據轉存入陣列存儲器中。

5 PCM編碼模塊

PCM碼是無線遙測系統中常用的一種編碼過程,本系統由采編器提供碼同步(YCK)和字同步(YZM)信號,將并行圖像數據編碼輸出為串行PCM碼流。在YZM變為高電平時,系統在YCK的上升沿輸出一個圖像數據位,每個圖像數據字節用8個YCK輸出。在讀主存儲器之前,CPU首先向FIFO寫入幀頭和幀計數,然后CPU控制FPGA讀取圖像數據寫入FIFO,最后依據YCK和YZM信號從FIFO中讀出數據進行PCM編碼,以60 kbyte/s的速率通過RS-422接口下發給采編器。

6 系統調試結果

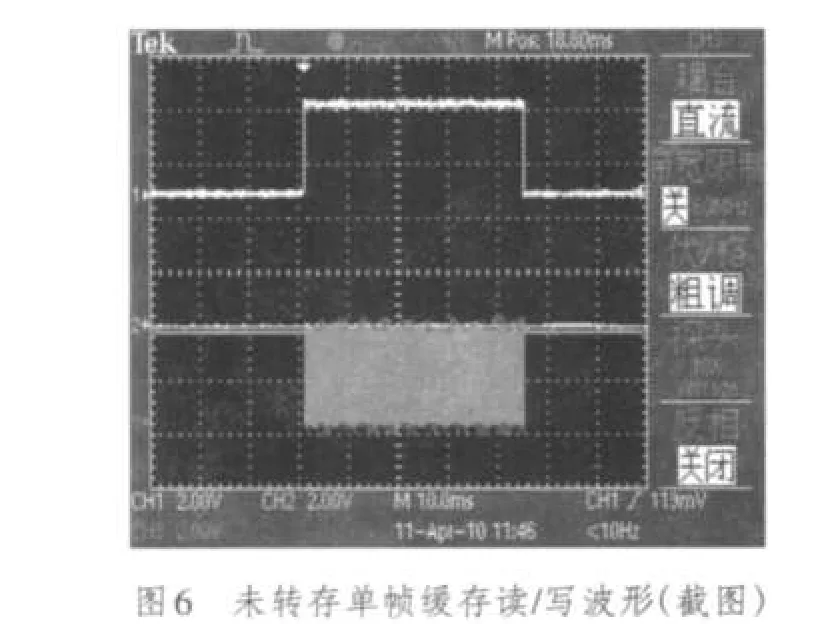

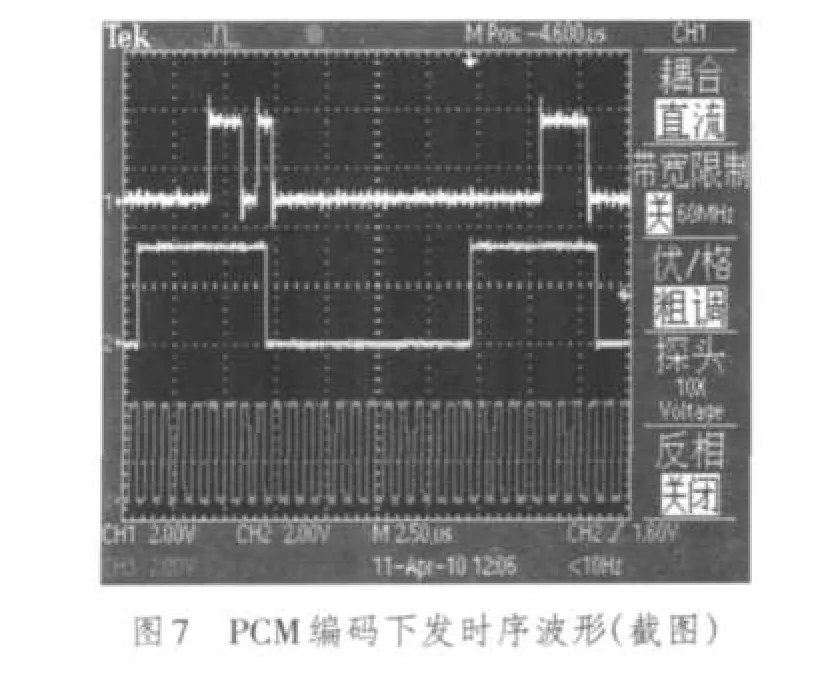

圖6為初始20幀的單幀緩存狀態,CH1為圖像數據的幀同步信號,CH2為寫單幀緩存信號。在陣列存儲器沒寫滿時,圖像數據先存入單幀緩存,然后自動轉存到陣列存儲器。編碼測試如圖7所示,FIFO中讀出的圖像數據在YZM為高時進行PCM編碼,CH1為編碼數據YDT,CH2為字同步YZM,CH3為碼同步YCK,圖中下發的YDT為0x0D和0x0E。

7 小結

本文利用CPU+FPGA的組合設計方法,實現了遙測圖像數據的無縫緩存,完成圖像數據的PCM方式串行下傳。設計中采用單幀緩存和陣列存儲的數據處理方式,并對圖像數據自動轉存的關鍵參數進行了詳細的分析,針對系統的功能進行了實際測試,測試結果表明陣列存儲可以高速有效地緩存圖像數據。

[1]孫榕,劉峰.高清視頻編解碼芯片選型及壓存系統的設計[J].電視技術,2007,31(11):26-28.

[2]蔡波.視頻實時圖像處理系統研究及設計[J].電視技術,2005,29(5):23-25.

[3]孫春鳳,袁峰,丁振良,等.基于LVDS技術的高速圖像采集系統的設計[J].儀表技術與傳感器,2009(3):46-48.

[4]張國兵.基于LVDS的圖像存儲轉發裝置的設計與實現[D].太原:中北大學,2010.