SRAM型FPGA單粒子翻轉測試及加固技術研究

邱金娟,徐宏杰,潘 雄,朱明達

(北京航空航天大學,北京 100191)

0 引言

空間輻射環境中的帶電粒子會導致航天器電子系統的半導體器件發生單粒子效應,嚴重影響航天器的可靠性和壽命,其中高能質子和重離子是導致單粒子效應的主要因素。必須對航天器用電子元器件的單粒子效應進行評估,采取一定的抗輻射加固措施,提高其可靠性。因此,空間輻射的單粒子效應研究具有重要意義[1]。隨著航天事業的發展,小型化已經成為衛星發展的主要趨勢,它要求所用電子元器件必須具有集成度高、尺寸小的特點,這就使得現場可編程門陣列(Field Programmable Gate Array,FPGA)成為星用電子元器件的主要器件。

SRAM型FPGA是目前應用最廣泛的FPGA架構,使衛星在軌編程成為可能,因此在空間得到了廣泛的應用。但空間應用表明,SRAM型FPGA器件具有較弱抗輻射能力,這使得FPGA器件的輻照效應研究成為空間電子元器件輻照效應研究的一個重要課題。針對單粒子翻轉進行了相應的試驗設計,為星載SRAM型FPGA的運行壽命評估及加固設計提供了重要的參考依據[2]。

1 單粒子翻轉

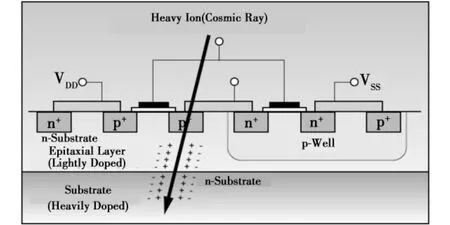

單粒子翻轉(Single Event Upset,SEU)是一種位翻轉,它既不損害器件也不干擾器件以后的工作,只會改變器件的當前狀態。當一個高能帶電粒子穿過pn結的靈敏區時,在其路徑上,粒子能量的一部分被硅原子所吸收,并在硅中產生電子——空穴對。這些電子——空穴對在pn結電場作用下發生漂移運動和擴散運動,電荷被收集之后,可使pn結誘發一個零點幾納秒的電流脈沖。瞬態電流會使節點電勢發生變化,達到一定程度會使導通管截止,截止管導通,引起器件邏輯狀態翻轉,這就是單粒子翻轉[3]。如圖1所示。

圖1 重離子引發的SEUFig.1 Heavy ion caused SEU

SRAM型FPGA內的配置存儲器、塊存儲器、觸發器等資源是單粒子翻轉的敏感區。單粒子翻轉尤其備受關注,因為它不但影響用戶設計的觸發器和BRAM塊,而且還影響器件的配置存儲器,它們可能改變電路的功能。全面估計SEU的敏感度是非常困難的,所以地面測試是不可避免的一個階段。

2 單粒子翻轉的測試技術

2.1 單粒子翻轉的靜態測試

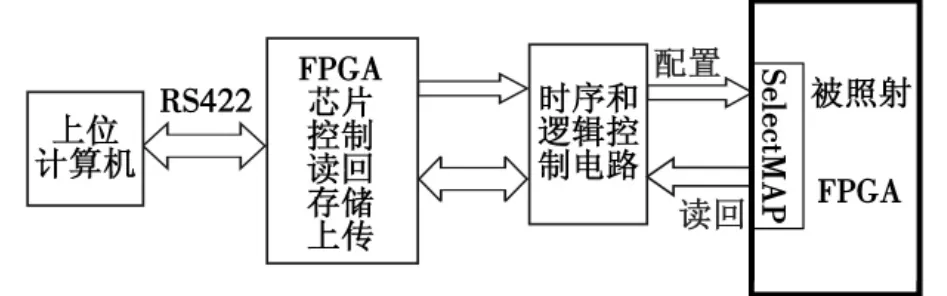

靜態測試是相對器件而言的,用來測試整個器件設備對輻射的敏感程度,它主要是測試FPGA內的配置存儲器、塊存儲器,從而獲取FPGA器件的配置存儲器的翻轉截面及塊存儲器的翻轉截面。圖2是FPGA單粒子效應靜態測試系統的測試方案。

圖2 FPGA靜態測試方案Fig.2 Static test scheme

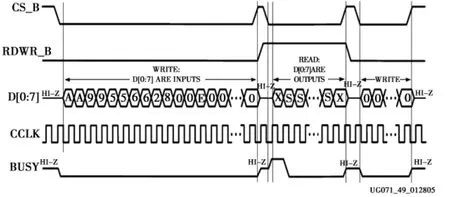

圖2的FPGA芯片是用于存放FPGA的讀回(Readback)命令、配置命令以及上傳讀回數據。邏輯控制模塊主要用于實現被測FPGA的SelectMAP接口的讀寫控制時序(見圖3)。SelectMAP接口是一個8位的雙向數據端口,可以通過它對Virtex進行配置,也可以通過它讀回配置數據,它是Virtex最快的配置方式[4-5]。用SelectMAP進行配置需要8位數據 D0:D7和7個控制狀態信號,分別是 CCLK、PROG、DONE、INIT、CS_B、RDWR_B、BUSY。

圖3 SelectMAP接口讀回時序圖Fig.3 Readback time sequence of SelectMAP

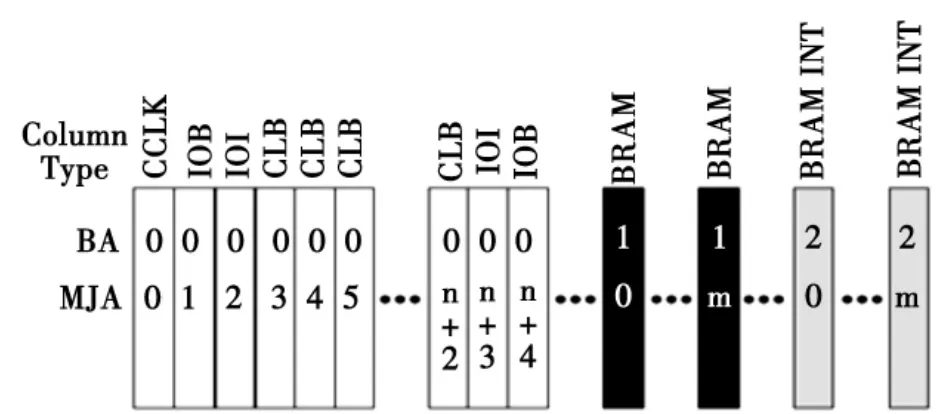

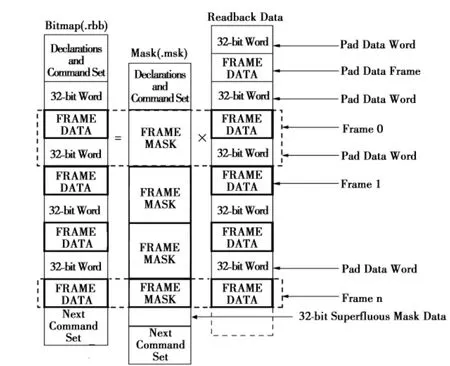

在輻照前,上位計算機把提前設計好的程序下載到被測器件中,然后根據以上時序圖,通過下位FPGA的SelectMAP接口讀回配置文件并將其上傳給上位機進行儲存作為原始文件,然后打開輻射源進行照射,經過一定時間或一定劑量的照射后,再次讀回配置文件并上傳,然后上位計算機在掩碼文件的幫助下,比較原始讀回文件相應字節與照后讀回內容的異同。讀回文件的內容分布如圖4,讀回數據有效性的計算關系如圖5。不相同時,根據圖4和圖5所示的配置數據分布與配置存儲器物理地址的映射關系給出具體錯誤發生的位置,并將錯誤數與位置上傳上位機。

圖4 配置文件內部分布圖Fig.4 Configuration memory map

圖5 讀回數據正確性判斷Fig.5 Verifying the correctness of readback data

2.2 單粒子翻轉的動態測試

靜態測試難以測試到FPGA內部觸發器及全局寄存器等資源,并且不能探測到程序運行時FPGA對輻射的敏感度。為了彌補這一不足,本系統還設計了動態測試的功能,用于測試FPGA內部有數據傳輸時,其內部BlockRAM(塊存儲器),CLB(配置邏輯單元)的單粒子翻轉敏感度。

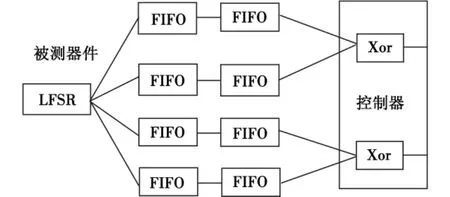

將BRAM配置成8×8192的FIFO(First Input First Output)。用線性反饋移位寄存器(LFSR)產生相同的隨機數填滿FIFO。當4路FIFO被隨機數填滿后,開始不斷向外溢出;將4路不斷溢出隨機數進行比較,不同的位數即為翻轉的位數。為了防止比較器受到單粒子效應的影響,精確地測試BRAM的翻轉敏感度,將比較電路設計在控制器中。采用LFSR產生的隨機數填滿FIFO,即使LFSR發生翻轉也不影響測試結果。此動態測試方法占用了BRAM 90%以上的資源,能夠較準確地評估 BRAM的單粒子翻轉敏感度[6]。其配置框圖見圖6。

圖6 BRAM測試圖Fig.6 Test circuit of BRAM

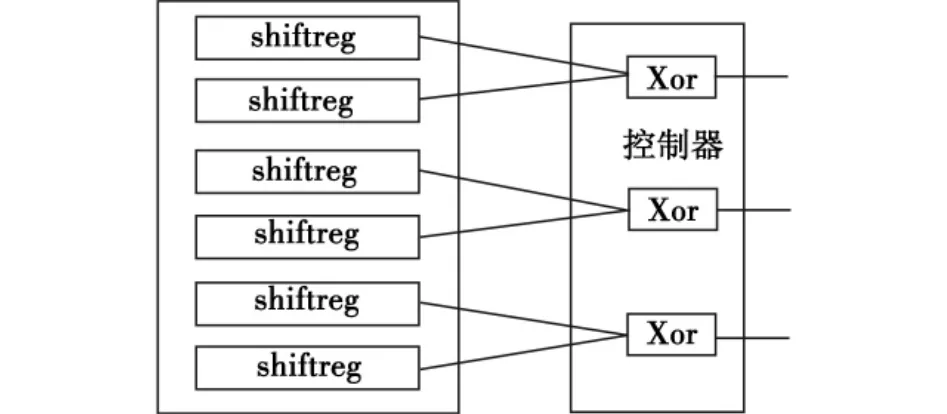

將CLB配置成6路1×1450的SR(Shift Register),用相同的數填滿SR,在相同時鐘下進行移位,將輸出數據進行比較,得到的翻轉結果上傳上位機。此動態測試方法占用了CLB 80%以上的資源,能夠較準確地評估CLB的單粒子翻轉敏感度。其電路配置見圖7。

圖7 CLB測試圖Fig.7 Test circuit of CLB

動態測試的翻轉結果也將實時地上傳并顯示到上位機界面上,沒有翻轉發生時的仿真結果見圖8。

為了驗證其可靠性,進行了故障模擬,在程序設計時故意將6路數據中任意一路注入錯誤,經試驗觀察都可以實時地上傳并顯示到上位機界面上。

圖8 CLB和BRAM測試無翻轉的仿真結果Fig.8 Simulation result of CLB and BRAM

3 單粒子效應的防護方法

SRAM型FPGA具有速度快、容量大、可反復編程的能力,是目前衛星通信平臺使用的主要器件。由于反熔絲的FPGA不具備二次編程能力,而基于Flash的CPLD的容量規模比較小等原因不適合在衛星平臺上使用,所以本文討論的對抗單粒子效應的方法也是基于SRAM型FPGA的。目前比較常用的對抗單粒子效應特別是發生頻率較高的SEU效應,主要有以下幾種方法[7-8]。

3.1 整體屏蔽減少輻射

在電子設備的外面一般采用一定厚度的材料進行輻射屏蔽,屏蔽可以減少設備所受的輻射效應。不同的材料對不同的粒子有著不同的屏蔽性能,經常采用的材料有鋁、鉛、鉭和某些酯類化合物等。整體屏蔽的辦法在航天電子設備中使用較多,國內也進行了不少有關抗輻射材料的研究。

3.2 冗余設計

常用的應對單粒子翻轉的技術是硬件冗余技術,可以將FPGA作為冗余的對象或者采用片內多模冗余。采用多片FPGA冗余有可能增加印制板布局布線的困難,增大設備的功耗、體積、重量等,片內冗余常用的三模冗余(TMR)是將電路三備份,利用設置在FPGA片內或片外的多數表決器對輸出信號進行表決。它能容忍一個備份模塊發生錯誤。雖然TMR帶來了可靠性的提高,但是也會使模塊的速度降低(有的甚至低到原來的80%),占用資源和功率增加(約為3.2倍)。所以設計時可以根據實際情況對關鍵部分使用部分3倍冗余法。

3.3 配置存儲器的回讀和重構

控制器負責從非易失大容量存儲器中讀取Xilinx FPGA的配置數據對其進行配置,然后在運行期間,對最容易受輻射效應影響的配置存儲器按列進行讀操作,然后與標準數據進行比對,一旦發現錯誤就進行重配置。另外,也可以通過對讀回數據進行CRC校驗來檢驗配置存儲器是否出現錯誤。對配置存儲器的讀回校驗和重配置(或局部重配置)是一種有效的抵抗輻射效應的方法。目前 NASA[9-10]、日本的 Smart Sat衛星工作組都在研究基于這種結構的衛星信號處理平臺,國內某高校從2001年起也在對這種結構進行研究與應用,并取得了較大成效。本文設計的測試電路板也可以實現回讀與重配置。

4 測試結果與分析

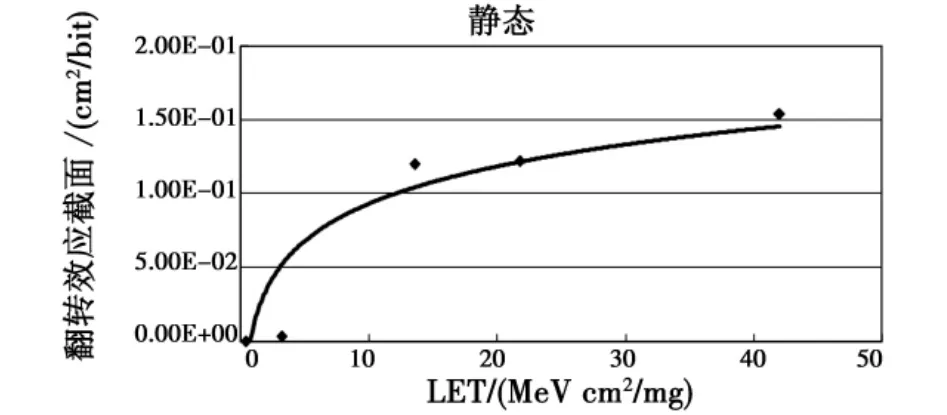

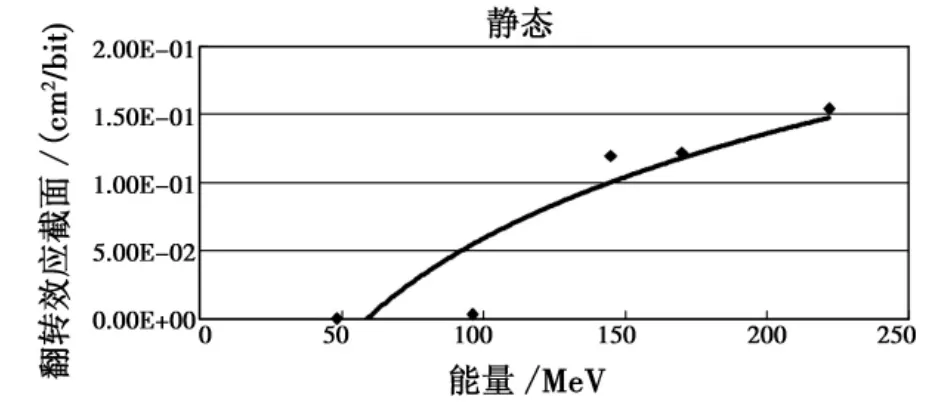

靜態SEU測試,測試配置位的翻轉敏感度。測試開始設置線性能量傳遞(LET)值為42 MeV cm2/mg,并逐漸被減少來觀察發生翻轉的極限值,最低的LET測試值是0.42 MeV cm2/mg。隨SEU數量的累積,器件功耗電流隨之增加,停止輻照,大電流狀態保持,重配置后,電流值恢復到正常。圖9顯示了翻轉效應截面與LET的關系,并進行了相似性擬合。圖10顯示了翻轉效應截面與能量的關系。

圖9 靜態測試SEU與LET的關系Fig.9 Static test SEU cross section versus LET value

圖10 靜態測試SEU與能量的關系Fig.10 Static test SEU cross section versus energy

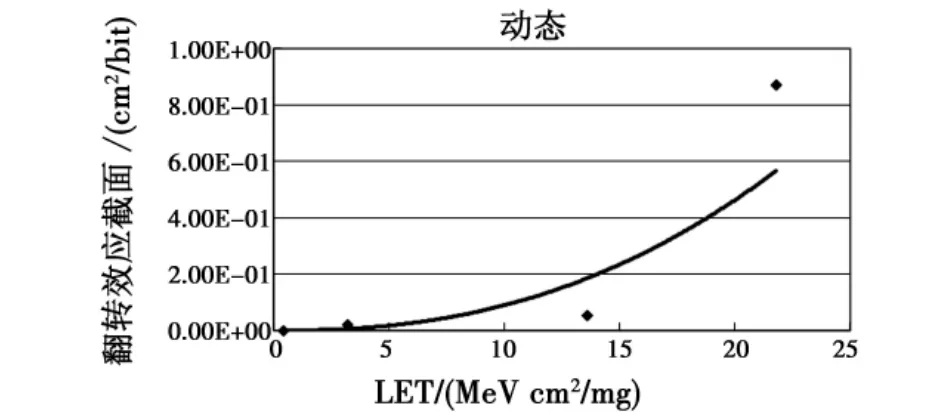

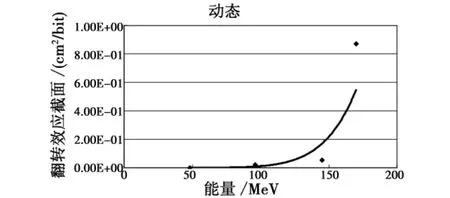

動態SEU測試,從試驗現象觀察,當注入量大于700 ion/cm2時,開始有翻轉出現。當程序運行正常時,配置位有翻轉,這顯示了靜態的翻轉對動態有可能不起作用。隨著注入量的增大,觀察到了大量翻轉,這種現象又包含了兩種可能:一種是配置位翻轉影響到動態測試;一種是用戶邏輯的翻轉。從試驗現象分析得知,配置位的控制邏輯出錯,導致了動態測試大量錯誤的出現。由于配置出錯,因而試驗中未曾得到BRAM和CLB翻轉截面,但是從試驗觀察看BRAM和CLB對單粒子的敏感度遠小于配置存儲器。為了評估動態測試下配置存儲器的敏感度,記錄了動態測試下配置存儲器SRAM的SEU截面與LET的關系,如圖11所示。

圖11 動態測試SEU與LET的關系Fig.11 Dynamic test SEU cross section versus LET value

SEU截面與能量的關系,如圖12所示。由試驗數據以及擬合所得到的走向趨勢可以看出靜態與動態下配置存儲器SRAM的SEU截面與LET、能量的關系是呈現相反方向的。

圖12 動態測試SEU與能量的關系Fig.12 Dynamic test SEU cross section versus energy

試驗結果表明,SRAM型FPGA單粒子翻轉敏感,同時存在單粒子功能中斷,對于航天器控制系統等關鍵部位,應慎用SRAM型FPGA。若使用則需要相應的加固技術。

5 結束語

本文詳細闡述了單粒子翻轉的靜態和動態的測試方法。靜態測試的讀回設計,采用了8位并行的SelectMAP接口,可以快速地讀回配置數據。動態測試程序對所測對象的覆蓋率可達90%,可以有效地評估其單粒子翻轉的敏感度。此試驗得到了動靜態下SEU的翻轉截面,對在地面上進行FPGA可靠性評估具有重要意義。另外文章結合工程實踐給出了解決常見的輻射失效問題的方法,利用FPGA配置數據可讀回的功能,系統可以應用在要求高可靠性的航天領域中,通過將FPGA的讀回數據和原始配置數據進行比較,判斷配置數據是否發生錯誤,若有錯,則重新配置FPGA,這是一種抗單粒子翻轉的有效措施,為進一步研究SRAM型FPGA輻照效應的機理和防護措施奠定了基礎。

[1]姚志斌,何寶平,張鳳祁,等.靜態隨機訪問存儲器型現場可編程門陣列輻照效應測試系統研制[J].強激光與粒子束,2009,21(5):749-755.

[2]馮彥君,華更新,劉淑芬.航天電子抗輻射研究綜述[J].宇航學報,2007,28(5):1071-1080.

[3]FULLER E,CAFFREY M,SALAZAR A,et al.Radiation testing update,SEU mitigation,and availability analysis of the virtex FPGA for space reconfigurable computing[C]//IEEE Nuclear and Space Radiation Effects Conference,2000:30-41.

[4]Xilinx Inc.Virtex-II platform FPGA user guide[Z].UG002(V2.1)28 March 2007.

[5]YUI C C,SWIFT G M,CARMICHAEL C,et al.SEU mitigation testing of Xilinx Virtex II FPGAs[C]//IEEE Nuclear and Space Radiation Effects Conference,2003:92-97.

[6]趙又新.SRAM輻射效應測試裝置的研制與應用[J].核電子學與探測術,2006,26(4):414-416,445.

[7]邢克飛,楊俊,季金明.空間輻射效應對SRAM型FPGA的影響[J].微電子學與計算機,2006,23(12):107-110.

[8]ALLEN G R,SWIFT G M.Single event effects test result for advanced field programmable gate arrays[C]//IEEE Radiation Effects Data Workshop,2006:115-120.

[9]HODSON R F,SOMERVILLL K,WILLIAMS J,et al.An architecture for reconfigurable computing in space[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference(MAPLD),2005:1-8.

[10]BERG M.Effectiveness of internal vs external SEU scrubbing mitigation strategies in a Xilinx FPGA:Design,test,and analysis[J].IEEE on Nuclear Science,2008,55(4):2259-2266.