基于FPGA的高性能DAC芯片測(cè)試與研究

馬 騰, 袁 著

(電子科技大學(xué) 電子科學(xué)技術(shù)研究院,四川 成都 610054)

0 引言

D/A 轉(zhuǎn)換器作為連接數(shù)字系統(tǒng)與模擬系統(tǒng)的橋梁,不僅要求快速、靈敏,而且線性誤差、信噪比和增益誤差等也要滿足系統(tǒng)的要求[1]。因此,研究DAC芯片的測(cè)試方法,對(duì)高速、高分辨率DAC芯片的研發(fā)具有十分重要的意義。

目前,波形測(cè)量和分析協(xié)會(huì)已提出了DAC測(cè)試的技術(shù)標(biāo)準(zhǔn) IEEE Std.1057[2],里面的術(shù)語(yǔ)和測(cè)試方法為 DAC測(cè)試提供了更多的參考。傳統(tǒng)的標(biāo)準(zhǔn)測(cè)試只適于信號(hào)發(fā)生器、示波器等測(cè)試儀器,但是測(cè)試精度不高;大規(guī)模芯片測(cè)試時(shí)則使用自動(dòng)測(cè)試設(shè)備(ATE),但是成本很高;最近提出的DAC的測(cè)試方法,比如結(jié)合V777數(shù)字測(cè)試系統(tǒng)可以進(jìn)行DAC測(cè)試[3],應(yīng)用模擬濾波器進(jìn)行音頻DAC測(cè)試[4],利用數(shù)模混合信號(hào)測(cè)試系統(tǒng)Quartet對(duì)高速DAC進(jìn)行測(cè)試,等等[5],這些方法在通用性、精確度和成本方面無(wú)法同時(shí)滿足。為了達(dá)到上述要求,提出了基于FPGA的高性能DAC芯片回路測(cè)試法。

1 DAC主要技術(shù)參數(shù)

DAC 的主要技術(shù)參數(shù)基本上可以分為靜態(tài)特性參數(shù)和動(dòng)態(tài)特性參數(shù)。DAC的靜態(tài)特性參數(shù)用來(lái)確定其轉(zhuǎn)換的精確度,主要包括失調(diào)誤差(Offset Error)、增益誤差(Gain Error)、積分非線性誤差(INL)以及微分非線性誤差(DNL)等。DAC動(dòng)態(tài)特性參數(shù)用來(lái)確定其交流條件下的性能,主要包括信噪比(SNR)、信號(hào)噪聲和失真比(SINAD)、有效位數(shù)(ENOB)、總諧波失真(THD),以及無(wú)雜散動(dòng)態(tài)范圍(SFDR)等。

2 測(cè)試方案

2.1 設(shè)計(jì)原理

DAC芯片參數(shù)回路測(cè)試法,就是將待測(cè)信號(hào)形成一個(gè)完整的信號(hào)回路。首先,使用 FPGA產(chǎn)生待測(cè)信號(hào),經(jīng)過(guò) DAC芯片后轉(zhuǎn)換成模擬信號(hào),再經(jīng)過(guò)濾波、放大電路和ADC芯片轉(zhuǎn)換成數(shù)字信號(hào),存儲(chǔ)在FPGA的RAM里,然后使用Quartus II 軟件Signal tap II工具取出數(shù)據(jù),導(dǎo)入Matlab軟件后,就可以對(duì)數(shù)字信號(hào)進(jìn)行分析和計(jì)算,從而得到DAC的技術(shù)參數(shù)[6]。在ADC采樣之前使用模擬信號(hào)接收器,如示波器、頻譜儀等,可與后端測(cè)試結(jié)果比較分析。設(shè)計(jì)原理如圖1所示。

由于 FPGA使用非常靈活,通過(guò)配置不同的編程數(shù)據(jù)可以產(chǎn)生不同的電路功能[7],對(duì)于不同分辨率和采樣速度的DAC芯片都可以進(jìn)行參數(shù)測(cè)試;濾波和運(yùn)算放大電路盡可能地降低信號(hào)在轉(zhuǎn)換和傳遞過(guò)程中的噪聲;數(shù)字信號(hào)在分析和計(jì)算方面比模擬信號(hào)更加準(zhǔn)確,保證了測(cè)試系統(tǒng)的精確度;相對(duì)于其他DAC測(cè)試系統(tǒng)來(lái)說(shuō),本測(cè)試方案使用的元器件比較少,成本比較低。

圖1 設(shè)計(jì)原理

2.2 硬件實(shí)現(xiàn)

DAC使用12位分辨率、250 Ms/s采樣速度的DAC芯片,芯片采用LVDS差分電路、PTAT基準(zhǔn)源以及4+4+4電流源陣列等關(guān)鍵技術(shù)設(shè)計(jì),可以滿足高速高分辨率轉(zhuǎn)換電路處理的要求。FPGA是Altera公司Cyclone III系列EP3C25Q240 C8芯片,功耗小,系統(tǒng)綜合能力強(qiáng),價(jià)格較低,包含了24624個(gè)邏輯單元、594 Kbit內(nèi)存空間和4個(gè)鎖相環(huán),硬件資源完全可以滿足測(cè)試的要求[8]。ADC是 LINEAR公司的LTC2242-12芯片,交流特性非常好,降低了測(cè)試系統(tǒng)帶來(lái)的誤差。運(yùn)算放大器是ADI公司的AD8008芯片,非常好的驅(qū)動(dòng)特性保證了DAC芯片輸出信號(hào)的質(zhì)量,提高了DAC的驅(qū)動(dòng)能力。

2.3 軟件設(shè)計(jì)

軟件代碼采用硬件描述語(yǔ)言Verilog實(shí)現(xiàn)。FPGA產(chǎn)生待測(cè)信號(hào)包括Test(全零、全一等)、Ladder(階梯波)和Sin(正弦波)。其中Test信號(hào)用于測(cè)試DAC芯片的靜態(tài)特性參數(shù)失調(diào)誤差和增益誤差,Ladder信號(hào)用于測(cè)試DNL和INL,Sin信號(hào)用于測(cè)試動(dòng)態(tài)特性參數(shù)SNR、SINAD、ENOB、THD和SFDR。

數(shù)據(jù)分析和計(jì)算過(guò)程主要通過(guò)Matlab軟件實(shí)現(xiàn)。DAC芯片輸入全零和全一信號(hào),可計(jì)算出失調(diào)誤差和增益誤差;使用階梯波信號(hào)測(cè)試INL和DNL時(shí),為了測(cè)試精確度,將 12位輸入數(shù)據(jù)分成高中低各四個(gè)位進(jìn)行測(cè)試。DAC的動(dòng)態(tài)特性參數(shù)測(cè)試采用快速傅里葉變換的方法,將Signal tap II工具取出數(shù)據(jù)經(jīng)過(guò)FFT和其他運(yùn)算,得到SNR、SINAD、ENOB、THD和SFDR等動(dòng)態(tài)特性參數(shù),它們可以全面地反映DAC的動(dòng)態(tài)特性,這里精確到14階諧波。

3 測(cè)試結(jié)果

Test信號(hào)測(cè)試:DAC輸入全一狀態(tài)的輸出電壓為760 mV,輸入全零狀態(tài)的輸出電壓為276 uV,經(jīng)過(guò)Matlab計(jì)算,失調(diào)誤差是0.036%,增益誤差是3.63%。

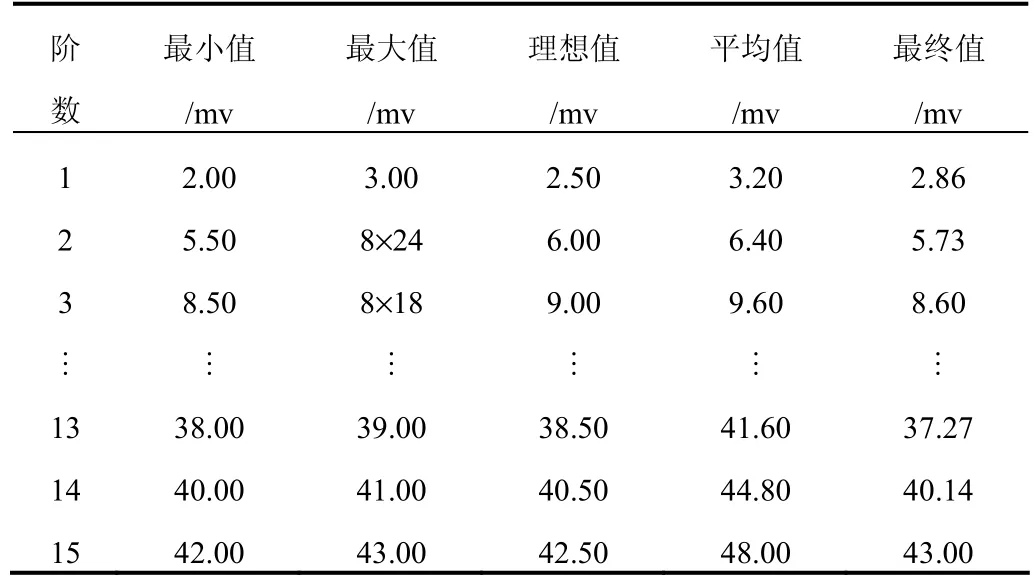

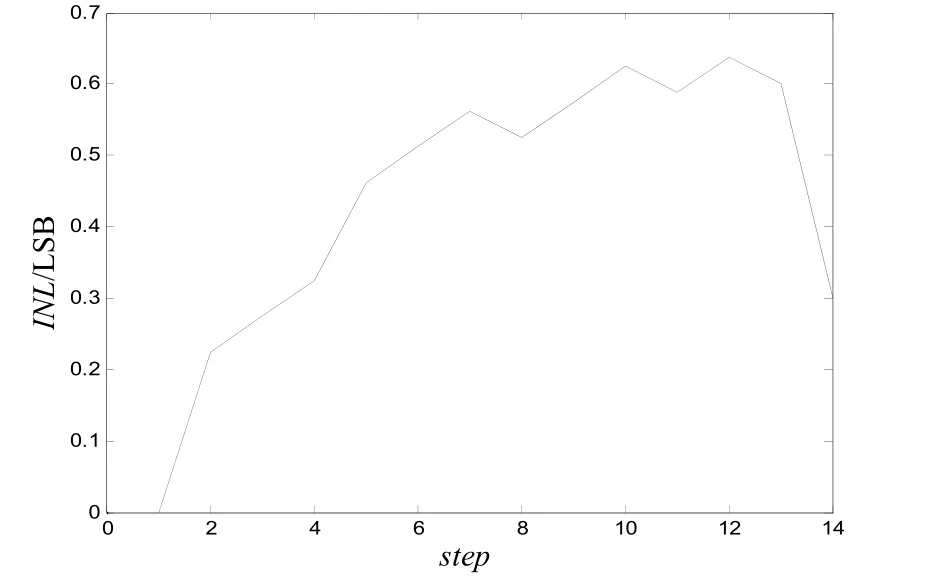

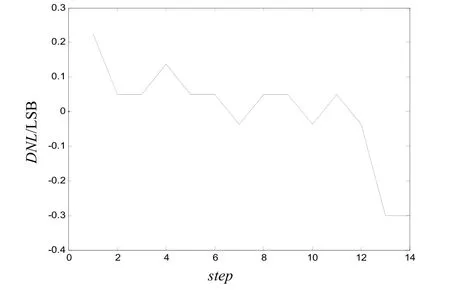

Ladder信號(hào)測(cè)試:在計(jì)算INL和DNL時(shí),DAC輸入高中低各四個(gè)位的測(cè)試原理相同,以中四位為例來(lái)介紹。n=12,i從24~28位變化,用1LSB來(lái)表示,測(cè)定輸出的15次(Step)階梯波,轉(zhuǎn)換成電壓值,部分?jǐn)?shù)據(jù)如表1所示,每列數(shù)據(jù)分別表示階數(shù)、測(cè)試最小值、測(cè)試最大值、測(cè)試平均值、理想數(shù)值以及考慮小電流影響后最終電壓值。使用Matlab軟件分析數(shù)據(jù)后得到INL和DNL曲線如圖2和圖3所示。

表1 15次階梯波電壓值

圖2 INL分析曲線

圖3 DNL分析曲線

Sin信號(hào)測(cè)試:輸入正弦波頻率 25 kHz,AD采樣率為100 MHz/s,輸出數(shù)字信號(hào)經(jīng)過(guò)Matlab分析計(jì)算后,測(cè)得SNR是58 dB,SINAD是57.75 dB,SFDR是62.84 dB,THD是58.62 dB,ENOB是9.3位。時(shí)域波形和FFT變換后14階諧波的頻譜如圖4和圖5所示。

圖5 sin信號(hào)輸出頻域波形

4 結(jié)語(yǔ)

以12位、250 Ms/s DAC芯片為例,在FPGA的基礎(chǔ)上使用回路測(cè)試法,測(cè)試了其靜態(tài)特性參數(shù)和動(dòng)態(tài)特性參數(shù)。實(shí)驗(yàn)結(jié)果表明,可以有效地測(cè)試DAC芯片的靜態(tài)特性參數(shù)和動(dòng)態(tài)特性參數(shù)。同時(shí)可以測(cè)試不同分辨率和采樣速度的DAC芯片,測(cè)試結(jié)果比普通模擬測(cè)試儀器的精度高,測(cè)試系統(tǒng)比專用DAC自動(dòng)測(cè)試設(shè)備成本低。

[1]BURNS M, ROBERTS G W. An Introduction to Mixed-signal IC Test and measurement[M]. New York: Oxford University Press, 2001:1-389.

[2]IEEE. IEEE Standard for Digitizing Waveform Recorders[s].[s.l.]:IEEE,1994.

[3]陸強(qiáng),孫曉麗. V777測(cè)試系統(tǒng)DA/AD測(cè)試技術(shù)的研究[J].電子與封裝, 2008(08):13-17.

[4]唐智軍. 濾波器在音頻 DAC測(cè)試中的應(yīng)用[J]. 中國(guó)集成電路,2009(121):65-69.

[5]趙步云,管杰,戴昌培.基于 Quartet測(cè)試系統(tǒng)的高速 DAC芯片測(cè)試[J].電子工業(yè)專用設(shè)備,2005(127):37-42.

[6]李媛媛,徐巖,王靖岳. 對(duì)MATLAB實(shí)現(xiàn)數(shù)字信號(hào)的QPSK的頻譜分析[J].通信技術(shù),2008,41(01):41-42

[7]張煒,楊虎,張爾揚(yáng). 一種靈活的實(shí)時(shí)FPGA數(shù)據(jù)配置方法[J].通信技術(shù),2003(02):23-24

[8]Altera Corporation. Cyclone III Device Handbook, Volume 1[R].[s.l.]:Altera Corporation, 2008.