繞制精密螺旋線的系統技術

文祖祥

(西北機器公司,陜西 西安 710119)

螺旋線螺距的精度指標和要求,是繞制精密螺旋線系統的研制核心。近年來,我們組織研究的繞制系統,螺旋線螺距精度實現了 (3~5)×10-3mm,安裝、調試簡單、使用可靠。

1 系統分析

1.1 螺旋線的基本要求

(1)螺距和螺旋線直徑決定了電磁波的相速,也決定了行波管工作電壓,因此,繞制螺距的精度高。

(2)要提高行波管效率,電子注要交出能量,就必須和電磁波同步。但電子交出能量后速度變慢,電磁波相速也必須變慢就要變螺距;為了減小交調也要變螺距;為了抑制返波振蕩要求改變螺距,又要保持相速不變,就必須同時改變螺旋線直徑。因此,要求螺距和螺旋線直徑可變。

(3)如果螺距發生突變,會造成反射,如果有兩個反射點存在就會造成反饋。由于行波管工作頻帶很寬,總會在某些頻率處形成正反饋,就有可能引起振蕩。即使由于反饋不夠大而不引起振蕩,也會由于有的頻率處是正反饋或負反饋而造成增益波動。因此,要求螺距必須均勻,沒有突變點。

(4)螺旋帶緊貼芯桿,無翹起。螺旋帶能和夾持桿緊貼以利于通過夾持桿散熱。

1.2 主要技術指標

芯桿直徑:φ5~φ10mm

繞制材料:鎢或錸鎢合金

材料規格:(0.10~5.00)mm×(0.08~0.50)mm

基本螺距:0.5~12.0mm

螺距精度:±(3.00~5.00)×10-3mm

繞制轉速:1~260 r/min

繞制方式:單層單向

繞制模式:等螺距、漸變螺距、跳變螺距、混合螺距等。

1.3 系統基本原理

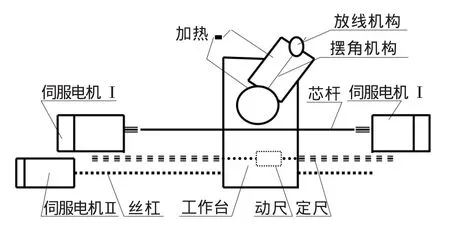

系統基本原理詳見圖1。

(1)繞線。通過兩個伺服電機Ι同步驅動芯桿旋轉實現。

(2)排線。伺服電機Ⅱ驅動絲杠帶動工作臺沿導軌移動。

(3)排線定位。光柵尺。

(4)帶材張力。放線機構中設置有張力調節功能。

(5)螺旋帶材緊貼芯桿。在繞制過程中,帶材素線與芯桿的母線須有交叉角才能使帶材帖在芯桿上形成螺旋帶,設置擺角機構。

圖1 原理簡圖

2 放線與繞線的動態分析

放線與繞線的基本運動是定軸轉動和平動,其過程有升速、運行、降速三個階段。

2.1 升速階段

由于芯桿和放線卷的外形尺寸與質量的差異,各自的加速時間不一致,按照繞線的要求,加在放線卷的阻力大小、外徑的變化、芯桿升速過程轉速的變化等要求匹配恰當,保持材料基板恒張力。

2.2 降速階段

隨繞線過程的深入進行,放線卷的外徑減小、轉速上升,引起的材料張力變化導致已繞成的螺旋線松散。

2.3 運行階段

如果繞線、放線的速度波動幅度大,就出現升速或降速的不良現象。

3 控制與誤差補償

(1)靜態誤差補償主要指由于制造和安裝帶來的誤差。用干涉儀對安裝后的系統進行測定、標定和補償,補償數據存放在計算機中,由軟件實現靜態補償。由于這種誤差具有線性積累的特性,隨著位置的增加可能會增大,補償間隔不宜太大[1,2]。

(2)動態誤差實時補償情況比較復雜,產生動態誤差的因素主要有制造精度、裝配造成的誤差如絲杠的螺距誤差、各部分之間的反向間隙、傳動或響應滯后、外部干擾或擾動等。

(3)將傳動機構之前的位置檢測信號反饋到控制器上參與控制,可大幅度縮短整定時間,因此,無論是傳動的間隙還是傳動的滯后都可以得到實時補償和修正。

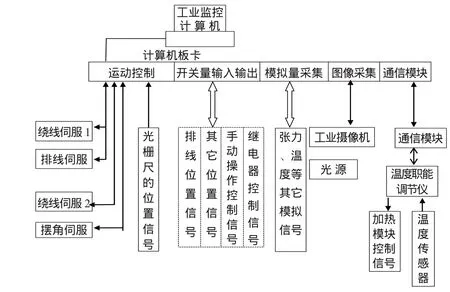

(4)控制系統硬件結構如圖2所示。

圖中:光學成像系統包括光源、大景深鏡頭、高分辨率工業攝像機;圖像采集系統由高速、高分辨率的圖像采集、圖像采集驅動軟件和高速計算機組成;圖像處理系統由圖像處理軟件、操作界面軟件、模式匹配軟件及專用圖像處理算法組成,其運算結果——擺角值作為擺角伺服系統的測量值;運動控制系統由基于PCI總線的運動控制卡、伺服驅動器及伺服電機構成。

圖2 控制系統硬件結構

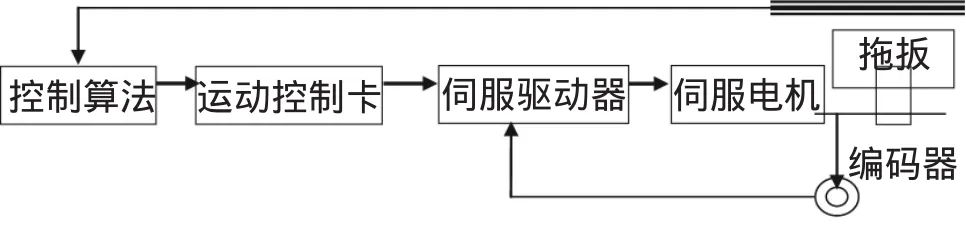

(5)為保證系統螺距的控制精度,用編碼器與伺服驅動器組成速度的半閉環,用光柵尺與監控工控機組成排線系統的位置全閉環,形成一個高精度的雙閉環控制系統[3,4,],見圖 3。

圖3 閉環控制系統功能框圖

(6)張力由張力傳感檢測,在上位機中實時顯示張力值。

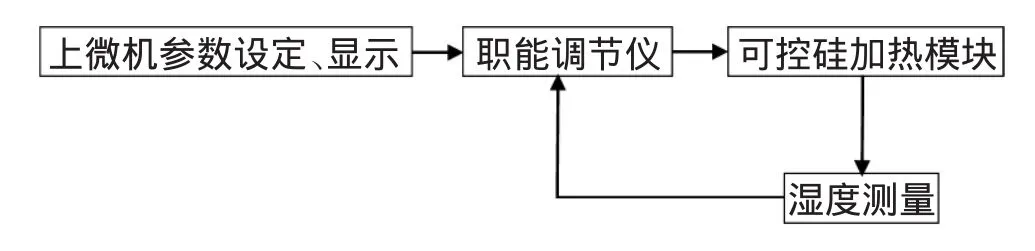

(7)溫度智能調節控制系統由智能調節儀、可控硅加熱模塊、溫度測量傳感器及上位機參數設置與顯示部分組成。功能框圖見圖4。

圖4 溫度智能調節控制系統功能框圖

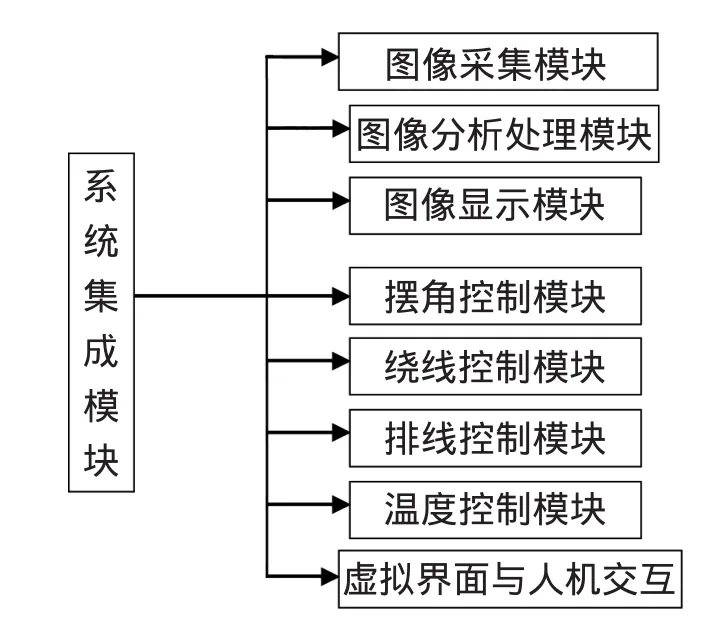

(8)軟件結構。軟件是系統的研究重點,要求操作簡單,界面符合操作習慣和中文信息幫助。軟件體系結構分為圖像采集、圖像處理、運動實時控制、溫度實時控制、張力實時顯示、模擬參數采集顯示、人機交互界面和系統集成等,見圖5。

圖5 軟件結構示意圖

4 測試數據分析

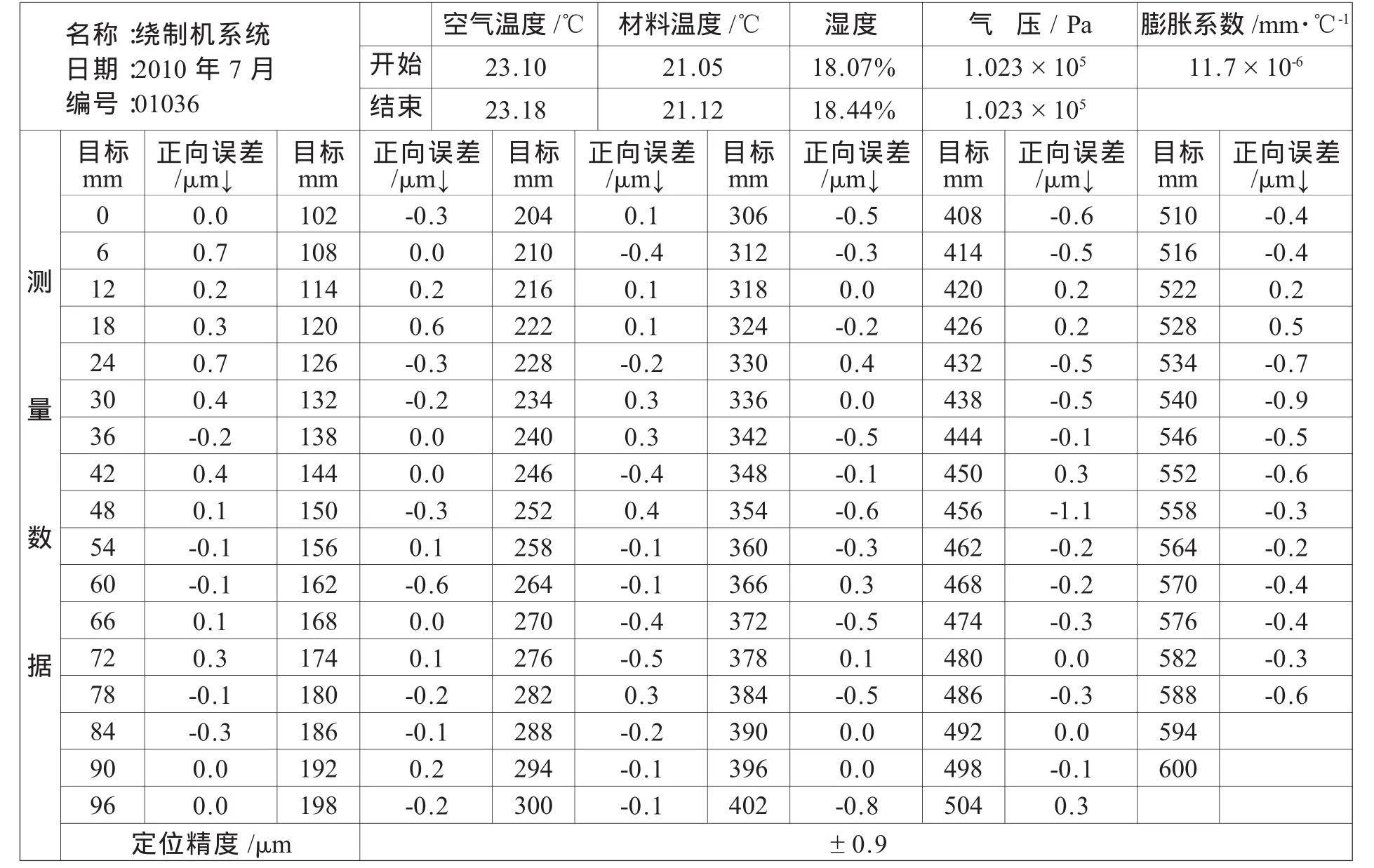

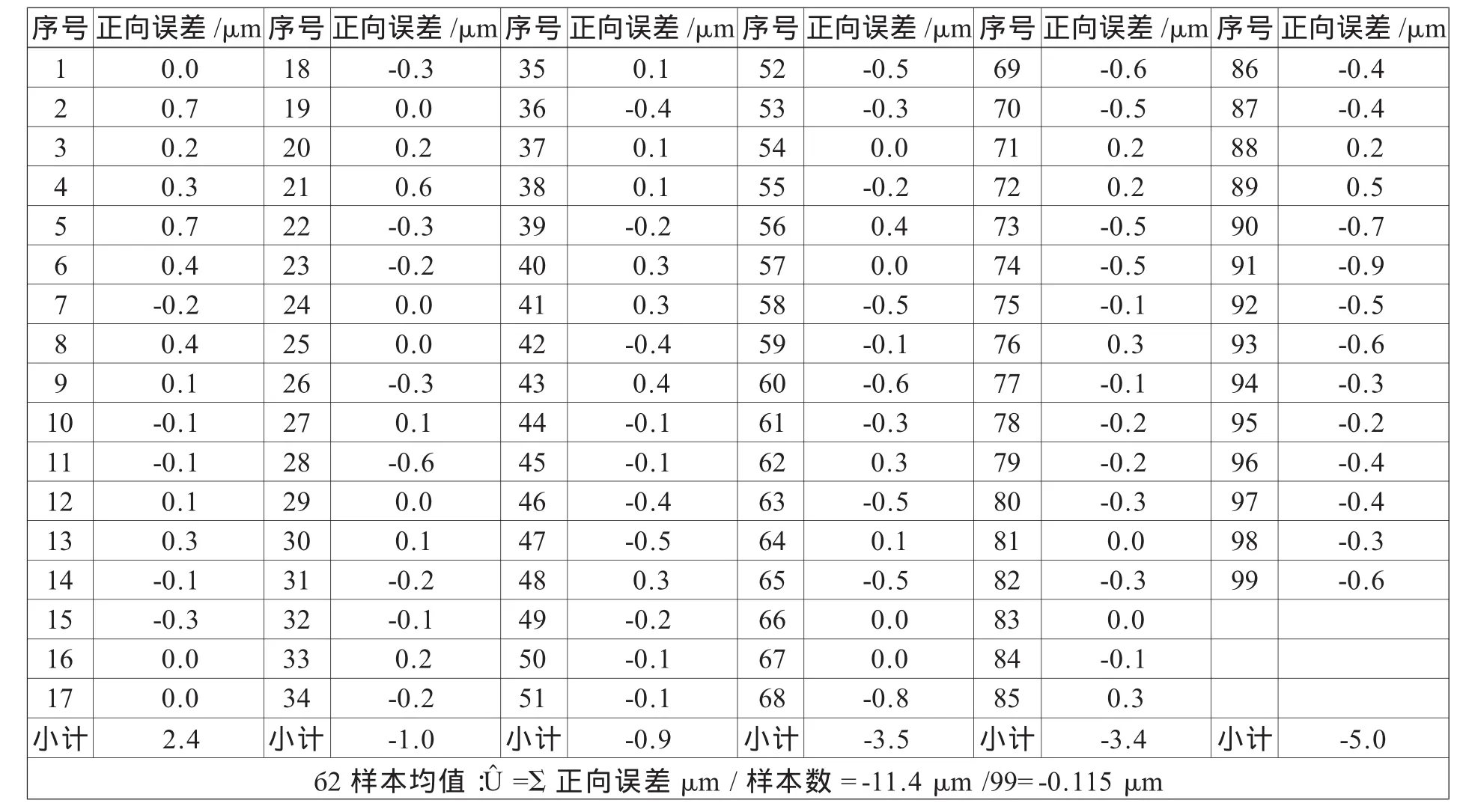

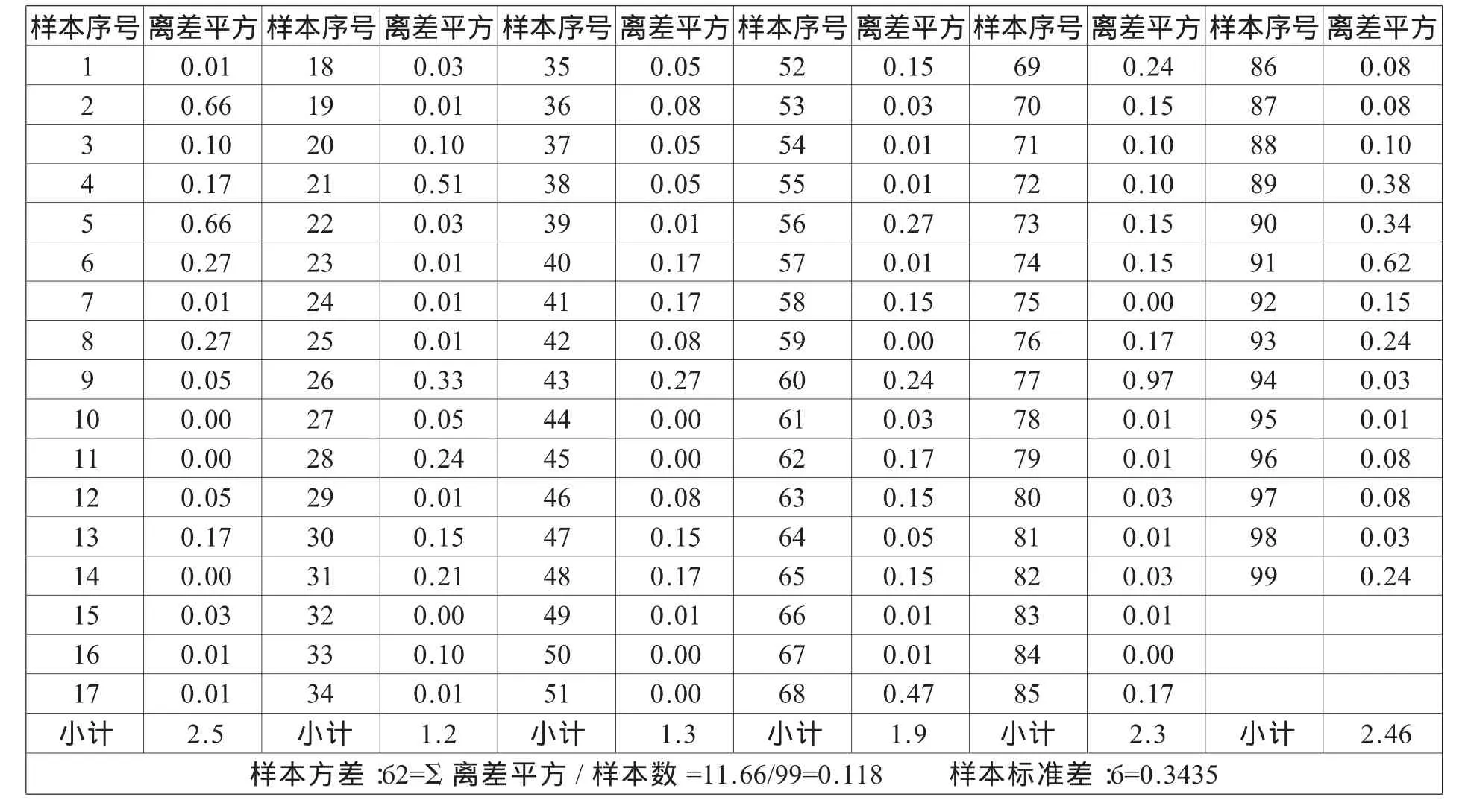

對系統進行檢測的結果(見數據表1、表2、表 3)。

系統定位精度不超過±1×10-3mm

平均精度為-0.115×10-3mm

置信區間 [-0.68×10-3mm,0.45×10-3mm](概率90%)

螺距控制精度±(3~5)×10-3mm可信系統補償點數100,定位精度不超過1×10-3mm滿足螺距精度(3~5)×10-3mm的要求

表1 X方向位置精度檢測數據

表2 X方向位置精度數據

表3 X方向位置精度數據分析

[1]田耘.無線通信FPGA設計[M],.北京:電子工業出版社,2009.

[2]吳湛擊.現代糾錯編碼與調制理論及應用[M].北京:人民郵電出版社,2008.

[3]牟崧友.卷積碼編碼器和Viterbi譯碼器的FPGA實現[J].電子工程師.2008,34(8):21-24.

[4]韓學超 韓新春.通信系統中卷積碼編解碼器的VHDL實現[J].通信技術.2009,42(10):72-74.