基于FPGA的像素探測器數據緩存設計

楊 萌,王祖強

(山東大學 信息科學與工程學院,山東 濟南104221)

粒子對撞機[1]是建立在高能同步加速器上的一種粒子對撞裝置。對撞機運行時,能量強大的粒子在其內部經過加速后對撞,以達到一定的相互反應速率。對實驗數據進行分析研究,可以幫助實驗者了解相應粒子的形態等特性,從而推動各種理論或技術的發展。

像素探測器[2]是粒子對撞機內部用于探測質子撞擊后所形成的離子軌跡的裝置,是一種專用傳感器,由像素探測器探測得出的數據結果即可繪制出撞擊后的離子軌跡。目前,像素探測器主要采用以下幾種設計方法:ASIC設計方法[3],其優點是集成度高且功耗低,但是設計成本高、周期長且風險較大;分立元件采用微處理器的設計方法,其優點是成本低、設計周期短且風險小,但是速度慢且體積大。針對這幾種設計方法,本文結合FPGA[4]提出了一種基于粒子對撞機像素探測器的數據緩存方法設計。相對ASIC設計方法,具有設計投入低、參數設置靈活、開發風險低而且開發周期短的優勢;相對于分立元件采用微處理器的設計方法,具有體積小、功耗低且速度快的優勢。

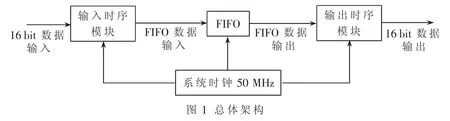

由于像素探測器的數據輸出具有保持時間短(最少保持時間為25 ns)、數據間隔時間不確定等特征,所以對于數據的存儲必須經過時序轉換電路將數據事先存入緩存,再寫入存儲器。本文的數據緩存設計由FIFO輸入時序模塊、FIFO模塊和FIFO輸出時序模塊三部分組成,通過驗證可以實現由探測器數據輸出端到存儲器的數據緩存功能。

1 總體設計

FPGA是一種新型的可編程邏輯器件,可以通過硬件描述語言生成所需的硬件,相對于傳統的ASIC設計,具有設計周期短、靈活性高、開發費用少、設計風險低等優點,是ASIC的一種高效低成本解決方案。本設計使用的FPGA是Altera公司的CYCLONE2芯片,最高時鐘頻率100 MHz。總體架構如圖1所示。

2 模塊設計及說明

2.1 FIFO模塊

FIFO即先進先出緩存器。FIFO與其他存儲器的最大區別就是沒有外部讀寫的地址線,因此應用起來十分方便簡單,但是相應的缺點就是只能順序寫入或者順序讀取,其尋址方式由內部指針自加自減完成,不能對特定的地址進行讀寫。FIFO通常使用在不同速度的接口數據交換中,通過FIFO使得時序分別符合兩個接口的特定速度,以進行數據傳輸。

Altera的FIFO按照驅動時鐘分類有兩種:單時鐘FIFO(SCFIFO),即讀和寫FIFO用的同一個時鐘信號;雙時鐘FIFO(DCFIFO),即讀和寫FIFO分別使用不同時鐘信號。其中雙時鐘FIFO還根據不同的端口數據寬度分為DCFIFO和DCFIFO_MIXED_WIDTH,所謂DCFIFO是輸入數據和輸出數據具有相同的數據寬度;而DCFIFO_MIXED_WIDTH是指輸入輸出端口可以使用不同的數據寬度。

使用Altera的FIFO MegaWizard inteface launched對FIFO進行構建,像素探測器模型中有16路傳感器輸出,每路輸出需要記錄100個數據。根據模型需要,構建FIFO的主要參數如下:

構建完FIFO后,對其進行時序仿真,仿真結果如圖2所示。

參照時序仿真圖對各個端口及時序進行說明:

aclr:異步清零端,1 bit。清零所有輸出狀態端口,對于 DCFIFO,3個 wrclk時鐘上升沿后清零wrfull端口,清零rdfull端口。如果輸出端口定義reg類型的則會被清零;否則會保持輸出值。

data:數據輸入端口,16 bit。當寫請求 wrreq有效時,保持數據直到數據被寫入FIFO。當使用手動定義FIFO時,其數據寬度用參數LPM_WIDTH定義。

1.增——增加作業形式,變單一為多元。著名心理學家布魯納說過:“學習的最好刺激是對所學材料的興趣。”課堂作業要將過去單一的“寫”的文本作業形式改進為口頭形式作業、操作演示作業、探究查詢作業、生活模擬作業等多種類型的作業。

q:數據輸出端口,16 bit。當有數據請求時(rdreq有效時),輸出數據。對于DCFIFO,輸出數據的寬度可以與輸入數據data端口寬度不同,具體用參數LPM_WIDTH_R定義。

rdcld:上升沿出發時鐘,1bit。用來同步以下信號:q、dreq、dfull、dempty、rdusedw。

rdempty:輸出數據為零時輸出高電平,1 bit。不管目標設備是什么,在讀請求發送前必須查詢rdempty信號是否為高電平,以避免錯誤指令發出。

rdreq:讀請求信號端口,1 bit。當需要從FIFO中讀數據時,向rdreq端發送讀請求,讀取數據個數與rdreq持續的時鐘數相同。需要注意的是,當rdempty有效時不能發送rdreq信號。對于這種情況,可以開啟空保護功能,通過設置參數UNDERFLOW_CHECKING高電平實現,當rdempty為高電平時rdreq信號自動被置為無效。

rdusedw:輸出數據顯示FIFO中可讀數據的數據量,7 bit。在DCFIFO中,其端口寬度要與手動設置參數LPM_WIDTHU相等。需要注意的是,對于Cyclone系列的FPGA,當顯示數據滿時實際FIFO的存儲數據量有可能并沒有達到存儲的最大值,因此應該參考full或者wrfull端口來執行正確的寫操作,參考empty或者rdempty端口來執行正確的讀操作。

wrclk:寫數據時鐘,上升沿觸發有效,1 bit。用于同步以下端口:data、wrreq、wrusedw、 wrfull和 wrempty。

wrfull:寫數據滿信號,1 bit。當此端口電平有效時,FIFO已經被寫滿。其注意事項同rdfull。總體而言,rdfull信號要比wrfull信號有所延遲,因此,應該通過wrfull信號的電平來判斷是否可以發送寫請求信號wrreq。

wrreq:寫請求信號。當需要向FIFO寫入數據時,向wrreq端發送讀請求,讀取數據個數與wrreq持續的時鐘數相同。需要注意的是,當wrfull有效時不能發送wrreq信號。對于這種情況,可以開啟溢出保護功能,通過設置參數OVERFLOW_CHECKING高電平實現,當wrfull為高電平時wrreq信號自動被置為無效。同時在取消aclr信號時不應輸入wrreq信號,否則aclr信號的下降沿和wrreq信號置為高電平后寫數據的上升沿會產生競爭冒險現象。對于CYCLONE系列的FPGA中DCFIFO器件,可以選擇添加同步電路同步aclr信號和wrclk信號,在手動設置中也可以通過設置參數WRITE_ACLR_SYNCH有效實現同步。

wrusedw:輸出數據顯示FIFO中寫入數據的數據量,7 bit。在DCFIFO中,其端口寬度要與手動設置參數LPM_WIDTHU相等。需要注意的是,對于Cyclone系列的FPGA,當顯示數據滿時實際FIFO的存儲數據量有可能并沒有達到存儲的最大值,因此應該參考full或者wrfull端口來執行正確的寫操作,參考empty或者rdempty端口來執行正確的讀操作。

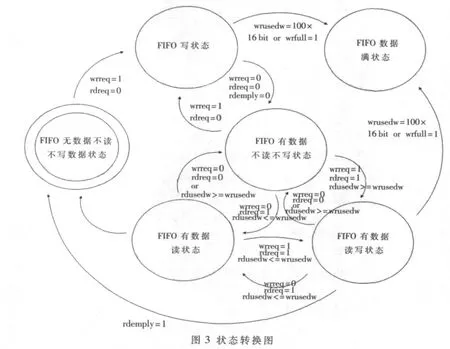

FIFO工作時的狀態轉換圖如圖3所示。

2.2 FIFO輸入時序模塊

FIFO輸入時序模塊用于使TIME COUNTER_WITHID模塊(用于對信號進行計時)的輸出數據時序符合FIFO輸入數據時序的接口要求。FIFO的寫請求信號wrreq的長度所包含的周期數為寫入FIFO數據的個數,并且寫請求信號有效時輸入數據端口的數據即被寫入FIFO,幾乎沒有延遲,因此輸入數據長度應符合FIFO的時鐘信號周期長度,并且寫請求信號長度也需要符合FIFO時鐘信號周期長度,兩者在時間上需要達到同步。

為了測試輸出數據長度符合FIFO接口的時序要求,分別進行了圖 4(a)、圖 4(b)、圖 4(c)所示的波形仿真,輸入信號的持續長度分別為10 ns、20 ns、30 ns。如圖所示三種輸入的輸出皆為10 ns保持時間,同時輸出10 ns write_en使能信號,符合FIFO接口要求。

參照時序仿真圖對各個端口及時序進行說明:

clk:FIFO輸入時序模塊時鐘輸入,1 bit。用于同步datain16、dataout16、write_en、complete、enable、usedw 信號,與FIFO中wrclk信號相頻相同。

complete:數據接收完成信號,1 bit。當 從 timecounter_withid模塊接收數據完成時發送給 timecounter_withid模塊,持續時長 1周期,timecounter_withid接收到信號時對內部數據進行初始化,做好準備對新的信號輸入進行計時。

datain16:16位數據輸入端口,16 bit。用于輸入16位數據。

dataout16:16位數據輸出端口,16 bit。用于輸出16位數據。

enable:數據寫入輸入時序模塊使能,1 bit。當有數據要寫入模塊時,首先在此端口輸入高電平,然后輸入數據方可被正確接收。

usedw:FIFO中可用數據端口,7 bit。用于查詢FIFO中可用數據量,以此判斷是否有剩余空間,進而確定是否向FIFO中寫數據。

write_en:寫使能信號,1bit。當要向FIFO中寫入數據時為高電平,dataout16進行數據輸出。

模塊流程圖如圖5所示。整個模塊以posedge clk為同步時鐘進行循環判斷。當寫入模塊使能enable有效且寫入完畢信號complete無效時,首先對FIFO的存儲情況進行判斷,當FIFO中字節小于 7FH時,說明FIFO未被寫滿,可以向其輸入數據。數據輸入FIFO的同時,寫使能write_en置為有效,對于計數模塊輸出的接收完成信號complete信號置為有效。對一個周期的計數寄存器counter進行判斷,如果counter為1即計時一周期到,則寄存器清零。counter的數值是在每次posedge clk信號到來時對write_en判斷后進行加 1,即當 write_en為有效電平時,counter才被加1用來計時。

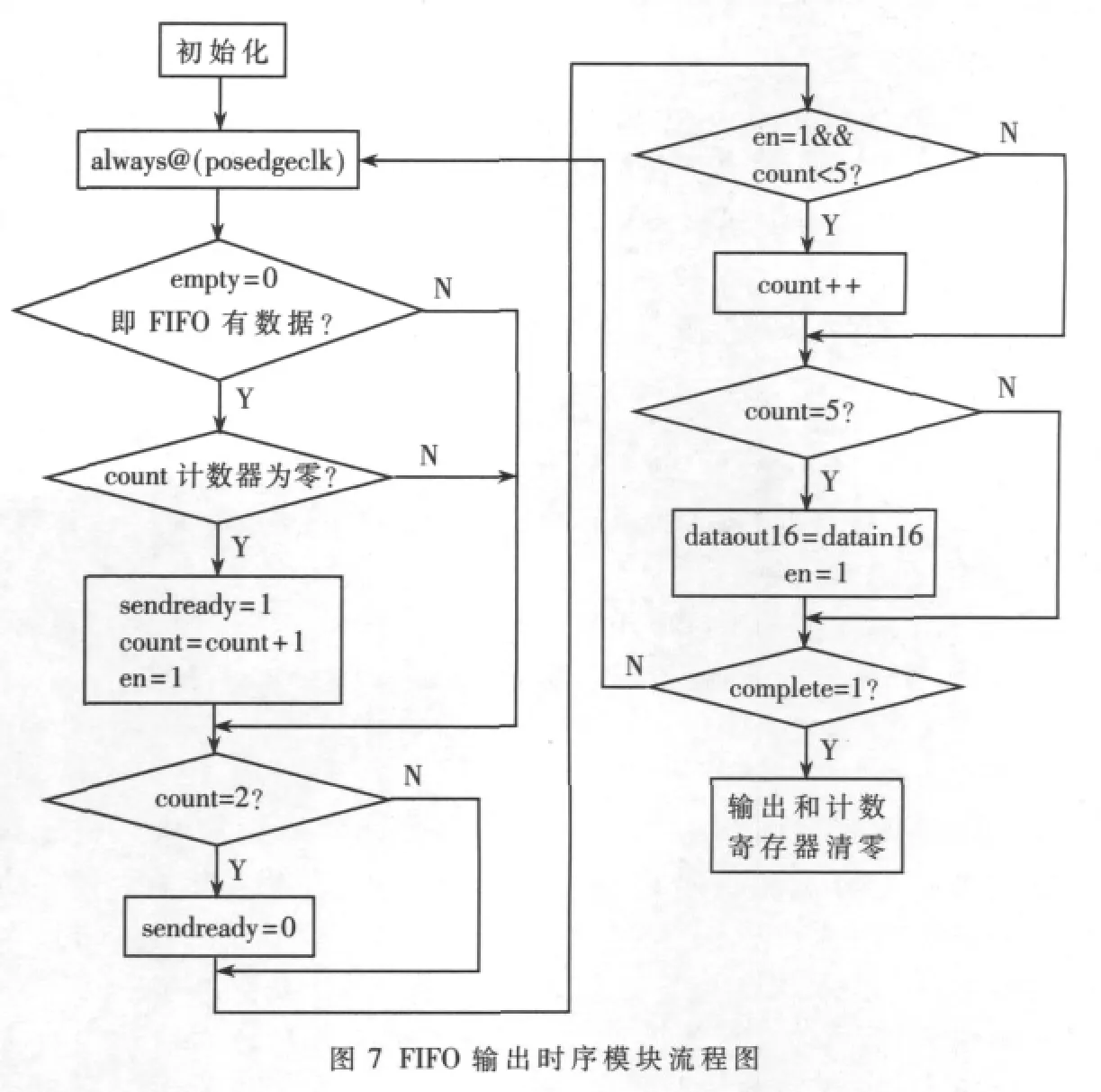

2.3 FIFO輸出時序模塊

FIFO輸出時序模塊用于使FIFO的輸出信號符合Flash讀寫時序規范。由FIFO的時序仿真圖可以看出,當讀請求信號rdreq發出后,數據要延遲15 ns左右才會輸出。如果Flash控制器發出讀請求信號后立即讀FIFO的數據,則會造成差錯。因此本模塊可以銜接FIFO和Flash控制器的端口時序。

時序仿真圖如圖6所示。由時序仿真圖可以看出,sendready信號相對于empty信號延遲了13 ns左右,dataout信號相對于sendready信號延遲了20 ns左右。可以滿足FIFO時序要求。

參照時序仿真圖對各個端口及時序進行說明:

clk:FIFO輸入時序模塊時鐘輸入,1 bit。用于同步datain16、dataout16、empty、complete、sendready 信號,與FIFO中wrclk信號相頻相同。

complete:數據接收完成信號,1 bit。當存儲器從模塊接收數據完成時發送給FIFO輸出時序模塊,持續時長1周期,FIFO輸出時序模塊接收到此信號時對內部數據進行初始化,開始對新的信號輸入進行計時。

datain16:16位數據輸入端口,16 bit。用于輸入 16位數據。

dataout16:16位數據輸出端口,16 bit。用于輸出16位數據。

sendready:數據準備就緒信號,1 bit。當FIFO收到讀數據請求信號并且有數據輸出時sendready發送有效信號,存儲器讀取輸出數據。

write_en:寫使能信號,1 bit。當要向 FIFO中寫入數據時為高電平,dataout16進行數據輸出。

模塊流程圖如圖7所示。

3 設計驗證

3.1 驗證

將程序下載到CycloneII FPGA芯片中,并且用按鍵作為輸入信號進行了測試,在控制臺上打印 FIFO的輸出結果,結果如圖8所示。

3.2 驗證結果分析

當FIFO中的數據經過時序轉換模塊可以向存儲器寫入時,ready信號為1,同時數據寫入寄存器并在控制臺打印,然后再將寄存器中的數據寫入存儲器,并向時序轉換模塊返回完成信號complete高電平1,等待從FIFO中讀取新數據。經過驗證,本設計可以將輸入數據進行緩存并且輸出給NiosII CPU,符合像素探測器數據緩存要求。

本文結合FPGA對粒子對撞機像素探測器的數據緩存提出了解決方法并進行了設計和驗證。相對于傳統的ASIC構建方法,具有高效率、低投入的優勢,提高了探測器升級和參數設置等方面的靈活性;相對于分立元件的設計方法,具有高速、低功耗和集成度高的優勢。通過時序仿真和FPGA驗證,能夠滿足像素探測器的設計需要。

[1]王直華.粒子對撞機與宇宙大爆炸[J].科技潮,2008(10).

[2]孟祥承.新型半導體探測器發展和應用[J].核電子學與探測技術,2004,24(1):87-96.

[3]GAGLIARD G.The ATLAS pixel detector electronics.Nuclear Instruments and Methods in Physics Research,2001:275-281.

[4]楊海鋼,孫嘉斌,王慰.FPGA器件設計技術發展綜述[J].電子與信息學報,2010,32(3):714-727.