基于FPGA圖像分塊解碼的系統設計

楊 揚,鄧家先,劉文進

(海南大學 信息科學與技術學院,海南 海口 570228)

0 引言

為了快速、準確地傳輸圖像信息,實現高速圖像編解碼,采用FPGA實現圖像編解碼,速度快、集成度高、可移植性強、容易實現大規模的系統,而且支持并行和流水線結構,它主要應用于衛星、醫學、通信、生物等領域。在傳統的系統設計中,由于FPGA開發板的集成度不高、內部資源有限,只能采用外掛RAM的形式對處理數據進行存儲和緩存,處理速度慢,占用資源也較大;而現在的FPGA集成度高,內部資源也比較大,采用內部的IP核實現片內存儲和緩存,以圖像分塊處理的方式且采用多路并行[1-2]和流水線結構,大大節約了硬件資源,提高處理速度,真正實現圖像高速解碼,保證了圖像高速解碼的實時性和正確性。

在圖像解碼前需要對圖像進行預處理,如頭文件處理,頭文件是處理圖像的一些附加信息,如壓縮包頭、圖像塊號、壓縮標識、圖像精度等。在對壓縮碼流進行檢測時,需要檢測壓縮包頭,通過標識符來識別碼流路數,而有的信息需要提取,如圖像壓縮比、精度、高、寬;有的需要剔除,如特殊標識,這就需要對輸入的壓縮碼流進行正確的檢測,檢測模塊輸出的是剔除了無用信息和標識的碼流信息,最后送到解碼模塊進行多路并行解碼。

1 硬件系統設計

1.1 一般的FPGA結構設計

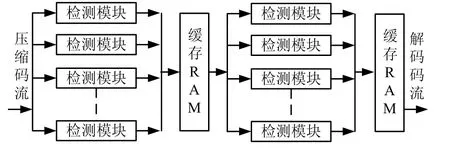

在以前的工程領域中,通常采用順序的多路解碼的方法。即在對圖像數據進行緩沖完后,依次在各個模塊中進行數據處理。其系統結構如圖1所示。

圖1 一般的結構框

這種結構的主要優點是占用的硬件資源少。但這種設計方法的致命缺陷是,每次處理都必須檢測輸出的碼流完全存入緩存RAM后,才能對啟動解碼模塊進行解碼,非常浪費讀寫RAM的時間,而且不能實現檢測與解碼同時進行。限于FPGA和RAM的接口帶寬,其處理速度不可能太高,而且占用的外掛RAM資源較大。

1.2 改進的分塊解碼結構設計

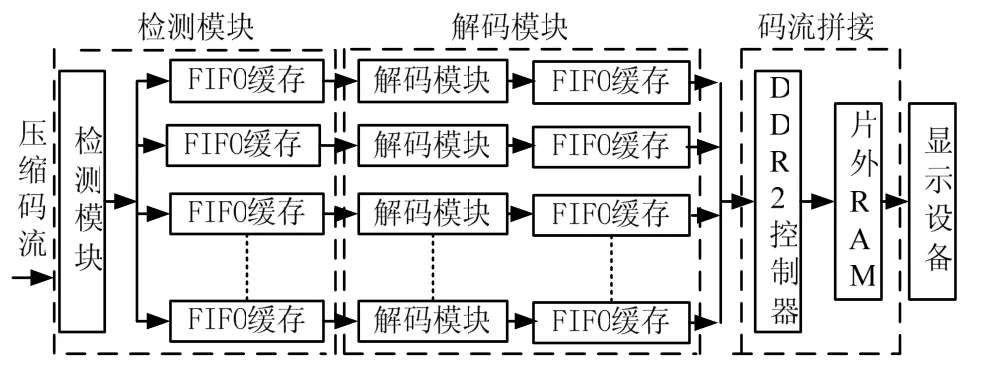

針對一般的順序多路解碼方法的缺陷,充分利用Xilinx公司的Virtex-5系列的FPGA[3]資源大、集成度高等特性,設計了一種采用1路檢測多路并行解碼方式,節約了硬件資源,而且不需將碼流完全存儲完,直接通過能同時讀寫的異步FIFO進行緩存,實現檢測與解碼同時進行,并采用多路并行和流水線操作,使解碼速度更快。系統選用VHDL硬件描述語言對JPEG-LS圖像壓縮標準[5-6]的解碼功能進行RTL級描述,并在集成開發環境ise11.1下,進行綜合優化、實現、配置,同時使用專業仿真工具Modelsim6.5完成行為和時序仿真。該系統結構框圖如圖2所示。

圖2 改進的結構框

系統設計的基本思路:將一幅圖像數據分成8塊的壓縮碼流,依次送入檢測模塊進行碼流的檢測,對包頭進行處理,通過檢測到的有關信息和圖像塊號,根據圖像塊號,將處理后的碼流順序存入選中的FIFO中進行緩存,緩存完后,經FIFO控制信號的選擇,進入多路并行圖像碼流的解碼模塊進行解碼,每一路解碼對應一幅圖像中的1塊,采用并行結構實現一幅圖像的8塊并行解碼,處理后的碼流經FIFO緩存后,通過DDR2接口控制器送入外掛RAM中進行碼流拼接,拼接存儲和處理后輸出到顯示設備上,而且采用流水線操作實現N幅圖像的連續解碼。

1.3 流水線操作技巧

流水線操作[7]的最大特點是,數據流在各個步驟的處理從時間上看是連續的。流水線設計的一個關鍵在于整個設計時序的合理安排,要求每個操作步驟的劃分合理。如果前級操作時間恰好等于后級的操作時間,設計最為簡單,前級的輸出直接匯入后級的輸入即可;如果前級操作時間大于后級的操作時間,則需要對前級的輸出數據適當緩存才能匯入到后級輸入端;如果前級操作時間恰好小于后級的操作時間,則必須通過復制邏輯,將數據流分流,或者在前級對數據采用存儲、后處理方式,否則會造成后級數據溢出。

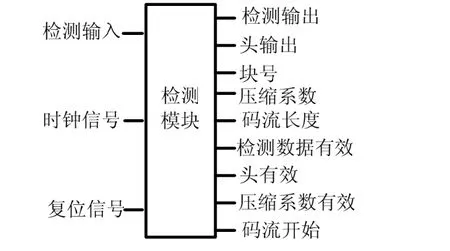

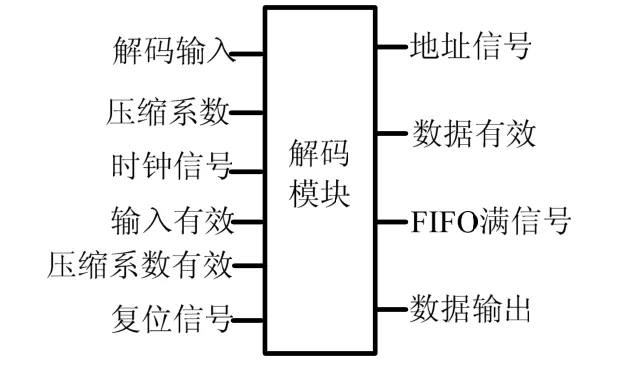

1.4 檢測模塊設計

由于解碼模塊解碼需要的時間遠比檢測模塊耗費的時間多,設計中所耗費的時間主要都來源于解碼模塊的解碼,所以這里并沒有采用8路檢測模塊進行檢測,只采用1路檢測模塊,節約了硬件資源,降低了設計的復雜度,通過測試總體花費的時間并沒有增加,這也是分塊圖像解碼優勢之一。例如,選用100幅圖像來進行測試,對每一幅圖像進行分塊,都按照一幅分8塊原則,當選擇8路檢測模塊時,第一幅圖像碼流送到第一路檢測模塊檢測完后,再送入解碼模塊進行解碼,解碼需要耗費大量時間,在第2路檢測模塊檢測完后需要等待上一路的解碼結束,這與用1路檢測模塊檢測相比,沒有明顯的優勢,反而增加了硬件資源和設計復雜度。檢測模塊的模塊圖如圖3所示。

圖3 檢測模塊

1.5 緩存模塊設計

在設計中,存在不同時鐘域的數據傳輸問題,即數據由某一個時鐘域的控制信號寫入,而由另一個時鐘域的控制信號讀出。解決這個問題比較好的方案是使用異步FIFO來做不同時鐘域的數據傳輸的緩沖區,這樣既可以使不同時鐘域的數據傳輸的時序要求變得寬松,也提高了它們之間的傳輸效率。在這里,使用FPGA的集成開發環境ise11.1自帶的IP核[4],可降低設計復雜度和提高綜合效率。使用IP核來產生異步時鐘的FIFO來對檢測和解碼后的碼流進行緩存,生成的FIFO的位寬、深度及其他參數需要根據圖像的大小來合理的配置,選擇時遵循無碼流溢出原則。例如,在實現多路并行解碼時,選用高度為64位,寬度為512位,精度為10位的圖像壓縮碼流,FIFO緩存碼流的位深為64×512=32 768位,用于檢測后緩存的FIFO位寬需8位,而用于解碼后緩存的FIFO位寬需11位。在FIFO的控制時,需要準確控制FIFO的讀、寫、空、滿信號的時序,否則會出現碼流的頭或尾數據丟失,從而導致解碼模塊解碼出錯。

1.6 解碼模塊設計

[8]。在整個系統中,解碼過程耗費的時間和占用的硬件資源主要來源于解碼模塊,所以合理設計的解碼模塊在整個設計中起著關鍵性的作用。考慮到這個問題,該系統使用圖像分塊解碼,并使用并行流水線操作。基本過程:假設總共有100幅原始圖像,將每一幅圖像壓縮成8塊碼流后送入檢測模塊進行檢測,當檢測到的圖像塊號為1,且FIFO的讀和空信號有效時送入第1路FIFO緩存,緩存后的碼流在FIFO的寫和滿信號有效時將碼流送入第1路解碼模塊進行解碼,解碼后通過FIFO緩存送入RAM,為碼流拼接做準備;當檢測到的圖像塊號為2,且在FIFO的讀和空信號有效時送入第2路FIFO緩存,緩存后的碼流在FIFO的寫和滿信號有效時將碼流送入第2路解碼模塊進行解碼,解碼后再通過FIFO緩存送入RAM,為碼流拼接做準備,當圖像塊號為3,……,8時操作同上,這樣就實現了8路并行解碼。在8路解碼模塊解碼沒有結束時,第2幅圖像碼流又緩存到8路FIFO中等待,等到第一幅圖像解碼結束立即啟動第二幅圖像的解碼,充分利用流水線結構操作,實現了高速解碼。解碼模塊的模塊圖如圖4所示。

圖4 解碼模塊

2 綜合與仿真

系統實現了JPEG-LS標準的解碼器,完成了從原始圖像壓縮碼流到解碼輸出顯示的全過程。分塊的壓縮碼流用C程序將碼流寫入文件,并加入相關的頭文件信息,設計采用大小為512×64,精度為10的圖像進行測試仿真,選其一幅圖像中壓縮好的一塊,將其復制成8塊,以便于數據的驗證。在ise11.1設計平臺下,對設計系統進行綜合,最大綜合頻率達到136.766 MHz,最大綜合延時僅為3.606 ns,完全滿足實時性要求。

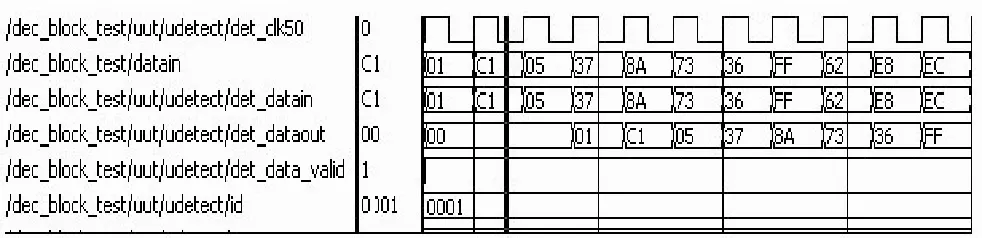

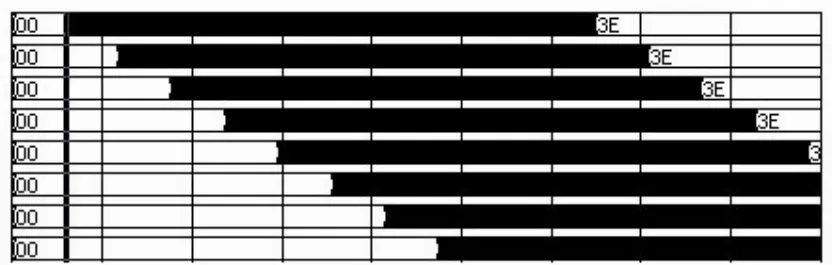

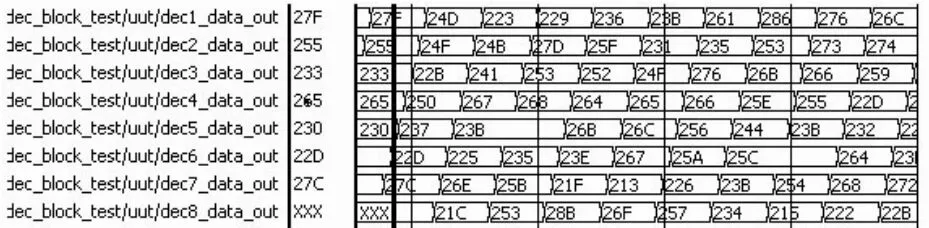

通過專業仿真工具Modelsim6.5對系統進行測試,各個模塊的仿真結果如圖5、圖6和圖7所示。

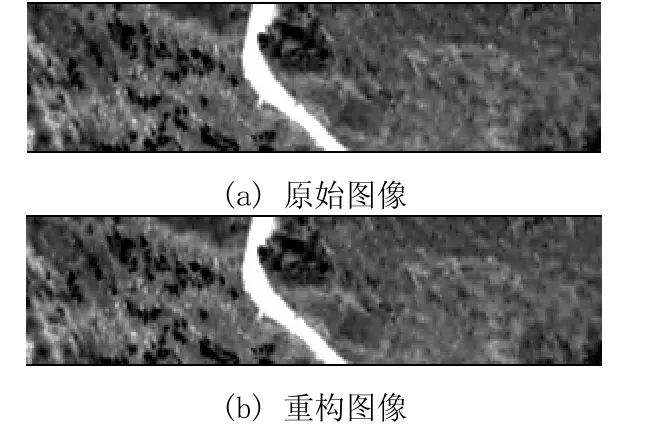

經過系統分塊并行解碼和重構,得到的結果如圖8所示。經測試,解碼后圖像與原始圖像幾乎無失真。

圖5 檢測模塊輸入和輸出碼流

圖6 FIFO緩存模塊碼流

圖7 解碼模塊8路并行解碼輸出碼流

圖8 原始和解碼重構圖像

3 結語

這里系統設計的基于FPGA的圖像分塊解碼實現方法比傳統的實現方法在處理速度方面有了很大的提高,特別是在對連續圖像、數據量非常大的衛星圖像進行處理時,效果更好。從仿真結果知,設計系統通過FPGA實現了圖像分塊的多路并行解碼,整個系統的綜合頻率達到136.766 MHz,采用多幅圖像進行測試,取得了很好的效果。仿真數據結果與通過C程序在軟件平臺上對壓縮碼流進行同樣解碼,再將C程序的解碼的碼流和這里系統解碼的碼流進行了嚴格的對比,完全一致。此硬件系統解碼速度很快,完全滿足系統的準確性和實時性。

參考文獻

[1] 王浩,劉文怡,韓志軍.多通道同步數據采集與處理系統的設計與實現[J].通信技術,2009,42(01): 297-299.

[2] 王海榮,鄧家先,易巧玲.碼流分配決策的VHDL實現及仿真[J].通信技術,2010,43(04):1002-0802.

[3] 田耘,徐文波.Xilinx FPGA 開發實用教程[M].北京:清華大學出版社,2008.

[4] Xilinx.single-Port Block Memory core v6.2 Data Sheet [EB/OL].(2005-04-28)[2010-08-22].http://www.xilinx.com.2005.

[5] WEINBERGER M J, SEROUSSI G, SAPIRO G.The LOCO-I:Lossless Image Compression Algorithm:Principles and Standardization into JPEG-LS[J].IEEE Trans.Image Processing,2000,9(08):1309-1324.

[6] ISO/IEC 14495-2:2003.Information Technology-lossless and Near-lossless Compression of Continuous-tone Still Imagesbaseline[S].

[7] 田心宇,張小林,姚英.一種可重構的高速流水線乘法器[J].電路與系統學報,2007,6(03):1007-0249.

[8] 支亞軍,蔣林,劉意先.基于FPGA的傳真譯碼電路設計與實現[J].通信技術,2010,43(04):1002-0802.