賽靈思靜態隨機存儲器型FPGA單粒子翻轉檢測

呂 達 吳 飛 陸 華

(航天恒星科技有限公司,北京 100086)

1 引言

太空環境下,賽靈思(XILINX)靜態隨機存儲器(S RAM)型的現場可編程門陣列(FPGA)容易受到單粒子翻轉(SEU)的影響。FPGA片內所有S RAM 都可能受到SEU 的影響,包括配置存儲單元、用戶邏輯單元、配置邏輯寄存器。配置存儲單元的內容決定著FPGA的功能,配置存儲單元發生翻轉會導致FPGA功能持續改變,直至下次重新配置完成。用戶邏輯單元包括塊RAM(BRAM)以及可編程邏輯單元(CLB)、可編程IO 單元(IOB)中的觸發器,這些存儲單元的值在FPGA運行過程中實時刷新,所以SE U 影響不大。配置控制邏輯寄存器發生翻轉屬于單粒子功能中斷(SEFI)的內容,會導致FPGA配置功能失效,但配置控制寄存器發生錯誤概率極低。據NASA測試數據顯示,每70年才可能發生一次[1]。故配置存儲單元SEU是FPGA抗SEU 設計中最重要的內容。

目前抗SEU 的措施包括通過一定厚度的材料進行輻射屏蔽、冗余設計、擦洗(Scrubbing)以及系統監控與重配置等。

冗余的方法包括采用多個完成相同功能的器件進行備份以及在同一器件中三模冗余容錯技術(TM R)[2],冗余設計的假設前提是:任何兩個存儲單元的同一位不會在同一時間發生SEU 效應[3]。采用多個完成相同功能的器件備份可以提高可靠性,但會造成體積和功耗的增加;三模冗余設計可以帶來可靠性的提高[4-5],但會使模塊的速度降低、占用資源和功耗增加。

擦洗的方法是指周期性的刷新存儲單元中的內容,可以減少受到SEU 而發生翻轉的概率,這種方法的優點是無需額外的硬件邏輯資源,實現簡單,其缺點是無法對擦洗數據進行校驗,不能判斷是否發生過SEU,而且只能恢復暫態故障[6]。同時,如果擦洗的時間間隔越大,可靠性就會降低[7]。

對配置存儲器進行回讀和重配置是一種有效的抵抗SEU 的方法,在FPGA實時運行過程中,回讀配置存儲器,并對讀出的數據進行校驗,如果發現錯誤則重新配置。目前NASA[8]、日本的智能衛星(SmartSat)[9]工作組都進行了基于這種結構的衛星信號處理平臺的研究,國內國防科技大學[10]、航天恒星科技有限公司等單位也進行了這方面的研究,并取得了一定的進展。

本文以XILINX Virtex-II FPGAXC2V3000為例,分別通過內部訪問接口(ICAP)和外部并行訪問接口(SelectMap),回讀配置數據并校驗,實現了S EU 檢測。另外,通過局部動態重構的方法,在地面環境實現了故障注入。

2 原理與方案

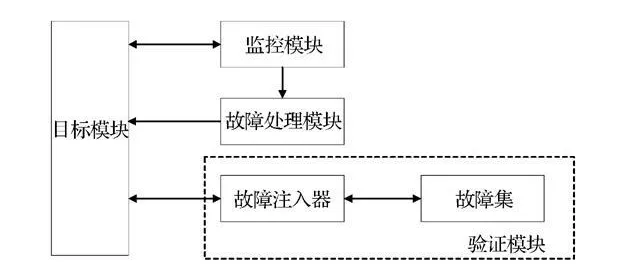

FPGA抗SEU 設計框圖如圖1所示,包括如下4個模塊。

圖1 FPGA抗SEU 設計方案Fig.1 Structure of SEU mitigation

1)目標模塊:指被檢測以及故障注入的實體。它們具備檢測以及故障注入的接口。

2)監控模塊:對被檢測目標進行監控,對情況進行判斷;在出現故障之后報告故障處理模塊。

3)故障處理模塊:檢測出目標系統故障后,根據故障類型,進行相應的處理。可以是給出報錯信息,也可能對錯誤予以糾正,也可能是既報錯又給予糾正。

4)故障注入模塊:在驗證檢測算法時使用,包括故障注入器和故障集。

故障注入器指對目標系統實施故障注入的實體。它根據故障注入模型條件,在故障注入時機到來的情況下,對目標系統進行故障注入。

故障集由實際發生在系統中的故障組成。故障集是通過對故障模型進行分析得到的集合。對于單粒子故障集來說,故障集包括了SEU、SEFI、單粒子鎖定(SEL)等,其中SEU 故障集包括CLB 故障、IOB 故障、全局時鐘(GCLK)故障以及BRAM Interconnect 故障等。

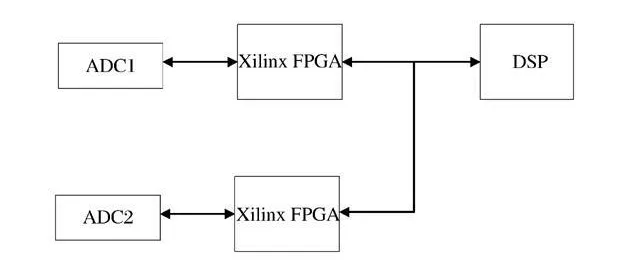

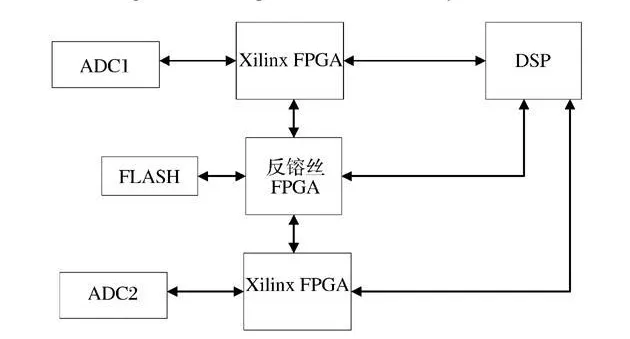

FPGA配置存儲器SEU 檢測可以通過ICAP和SelectMap 接口實現。通過ICAP 接口,FPGA可以在普通星載軟件無線電平臺實現對自身的SEU 檢測。目標模塊由兩片XILINX FPGA實現,監控模塊位于被監控FPGA內部,故障注入以及故障處理模塊由被監控FPGA和DSP 模塊完成,如圖2所示。通過SelectMap 接口實現SEU 檢測,需要在普通星載軟件無線電平臺基礎上增加監控模塊。目標模塊是兩片XILINX FPGA,監控模塊由反镕絲FPGA,反镕絲FPGA通過SelectMap 接口回讀SRAM 型FPGA的配置數據。故障注入以及故障處理模塊由反镕絲FPGA和DSP 模塊完成,如圖3所示。

圖2 通過ICAP 接口進行FPGASEU檢測的硬件框架Fig.2 Detecting SEU for FPGAby ICAP

圖3 通過SelectMap 接口進行檢測的硬件框架Fig.3 Detecting SEU for FPGAby SelectMap

2.1 檢測模塊

對FPGA配置存儲單元進行SEU 檢測的辦法是:目標FPGA在工作狀態下,對其可配置單元中的內容進行回讀(active readback),對配置數據進行校驗。為了避免破壞BRAM 中的內容,只針對其他內容進行回讀校驗。

2.1.1 回讀接口選擇

Virtex II FPGA配置訪問接口包括JTAG、SelectMap,以及ICAP 三種,其中ICAP是內部訪問接口,監控模塊在目標FPGA內部完成,通過ICAP接口訪問配置存儲器,可以實現對目標FPGA自身的檢測,電路結構最為簡單,不需要另加監控模塊,但監控模塊自身也有發生SEU 的可能,如圖2所示。JTAG 和Selectmap 都是外部訪問接口,外部設備通過這兩個接口可以實現對目標FPGA進行回讀,但Selectmap是并行接口,回讀速度快,訪問方便,如圖3所示。本設計分別選擇了ICAP 接口和SelectMap 接口進行回讀檢測。

2.1.2 檢測周期確定

根據NASA和XILINX 一起對XILINX VirtexII 器件(XC2V1000)進行輻照測試獲得的參數,見表1[11]。以XC2V1000配置存儲器的3Mbit為例,根據該數據可知,平均每天就會發生1.3bit 的位翻轉錯誤,發生 SEU 的最長時間為 18h,XC2V3000 的配置存儲器大約為9M bit,估算得發生SE U 的最長時間約為6h。SEU 檢測速率至少是故障概率的10倍,所以最長檢測時間為0.6h。

如果回讀檢測模塊工作時鐘為10M Hz,通過SelectMap 接口,對XC2V3000 配置存儲器進行回讀檢測,完成1次檢測大約需要的時間是110ms,因此最短周期就是110ms。

根據以上考慮,文章選定1s 對配置存儲器進行1次回讀檢測。

2.1.3 檢測內容確定

S EU 檢測的做法通常是對配置存儲器的所有內容進行回讀檢測,但并不是所有回讀數據都需要校驗,如BRAM 中的內容。XILINX 提供了mask文件,表明了不需要校驗的內容。但如果校驗的時候使用mask 文件,需要占用存儲空間,XC2V300器件mask 文件大約9.2M bit,對星載電子設備來說是一個很大的空間。文章將mask 文件嵌入到配置以及回讀中去,回讀數據可以直接和原始bit 文件進行校驗或者進行C RC 校驗,節省了存儲空間。

2.2 故障注入模塊

故障注入是模擬FPGA、SEU,以及單粒子功能中斷等單粒子效應的一種有效方法。對FPGA進行S EU 模擬可以采用重離子輻射的方法,NASA的噴氣推進實驗室(JPL)和單粒子效應(SEE)協會對大規模集成電路的單粒子效應進行了很多模擬試驗,利用各種模擬源(粒子加速器提供的各種重離子和質子、脈沖激光等)對FPGA進行輻照,使FPGA配置單元發生隨機錯誤。在算法調試階段,采用照射的方法會花費高額費用,另外也不利于實施。

利用Virtex II 系列FPGA可局部動態重構的特點。局部動態重構技術指對于特定的基于SRAM 結構的FPGA,在一定的控制邏輯的驅動下,對芯片的部分邏輯資源實現在系統的高速的功能變換。局部動態重構是指對重構器件或系統的一部分進行重新配置,而在此過程中,其余部分的工作狀態不受影響。

XILINX Virtex II FPGA最小訪問單元為1幀,因此對FPGA配置存儲器每幀進行動態重構即可完成單粒子模擬。這種研究方法可以在很大程度上仿真地面單粒子模擬試驗,縮短試驗周期,提高試驗的靈活性。基于FPGA配置文件的保密性要求,以及XILINX FPGA結構本身的保密性,XILINX對配置文件中每一幀具體的邏輯資源以及如何組織這部分信息是不公布的。每一幀配置數據不但包含對邏輯資源的配置,即某些位不允許故障注入,可以參考mask 文件對允許比較的位進行故障注入。

故障注入模塊由三部分組成:故障模式寄存器、控制寄存器、故障發生器。故障模式寄存器和控制寄存器可以由處理器通過特權指令訪問,可以很方便地設置故障模式,制造所期望的故障模式,并控制故障的注入。故障模式寄存器可以對FPGA的不同部位設置所期望的故障模式。如欲使CLB部分的第i 幀第j 位發生翻轉,只要設置故障模式寄存器相應的數據位即可。控制寄存器可以控制故障的插入,再非調試模式下可以禁止故障的插入,保證被監控FPGA正常運行。在調試模式下,允許故障的插入,數據在經過故障注入器后,產生類似于SEU效應的錯誤數據,寫入到配置存儲器,達到故障注入的目的。

2.3 軟件流程圖

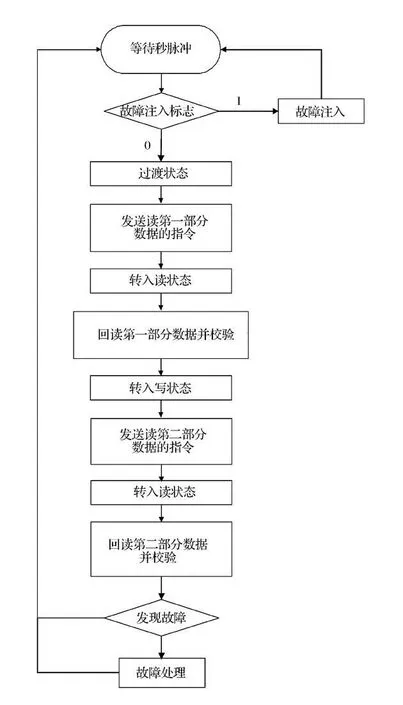

S EU 檢測試驗的軟件流程如圖4所示:秒脈沖下降沿到來時,檢測故障注入標志,如果故障注入標志為1,則進行故障注入,即對配置存儲器的一幀進行改寫,否則對配置存儲器進行檢測。

圖4 S EU 檢測試驗軟件流程圖Fig.4 SEU detection algorithm flow chart

3 試驗結果及分析

3.1 SEU檢測試驗

3.1.1 通過ICAP 實現SEU 檢測

FPGA對自身配置存儲器進行檢測結果如下:被監控FPGA實現點燈功能,未進行故障注入的時候,回讀數據的CRC值保持恒定,如圖5所示,CRC值始終是0xA2E2,檢測結果compareout 信號也始終為低電平。

對配置存儲器進行故障注入,配置存儲器的Block Interconnect 列的第一幀的第一個字節進行改寫,將最初的一個字節0×00 改為了0×07。故障注入后重新檢測,回讀數據的CRC值變為F00F,檢測結果信號compareout 也變為高電平,表明檢測到SEU 翻轉,如圖6所示。

圖5 未故障注入時候CRC值始終不變Fig.5 CRC data are fixed w hen no SEU happens

圖6 故障注入后CRC 發生變化Fig.6 CRC data are changed when SEU happens

3.1.2 通過SelectMap 接口實現SEU 檢測

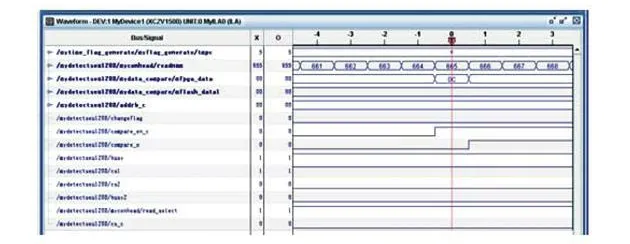

目標FPGA實現點燈功能。故障注入前始終未檢測到SEU。故障注入是通過對GCLK 前兩幀數據進行改寫實現的。對配置存儲器前兩幀數據第一個字節分別寫入0×0C,原來都是0×00;其余部分寫入0×00。故障注入后小燈停止閃爍,開啟回讀檢測模塊,檢測到SEU,如圖7所示。

圖7 故障注入后后檢測到單粒子翻轉Fig.7 S EU is detected after bug is inserted

圖7中,從上至下第8個信號compare_o表示回讀的配置數據與原始數據的比較結果,readnum表示回讀比特計數。由圖中看出當readnum=666時,compare_o為高電平,表示檢測到了SEU。

3.2 資源使用情況

3.2.1 通過ICAP 實現SEU 檢測

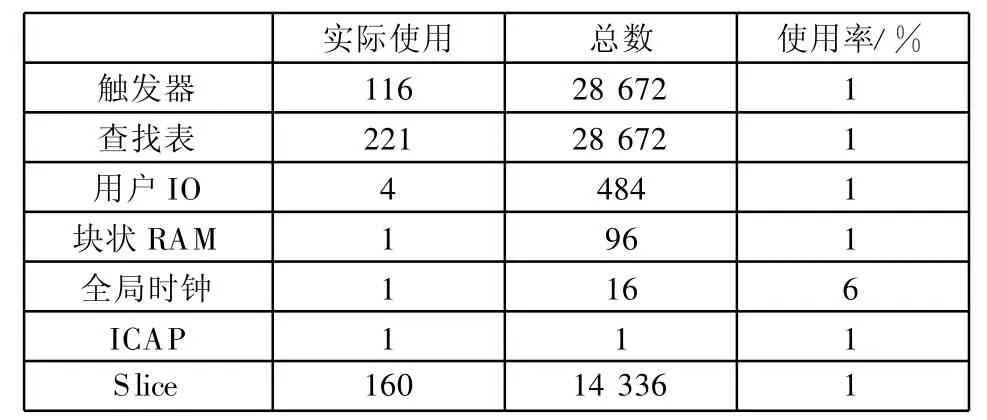

FPGA中實現的功能是通過ICAP 對自身配置存儲器進行回讀,并對讀出的數據進行CRC 校驗,所使用的資源如表2所示。

由表2可見,本文的FPGA抗SEU 設計占用資源少。本設計在星載GPS 接收機FPGA模塊中進行了試驗,FPGA設計在增加抗SEU 的功能的同時,不會造成資源的顯著增加。

表2 FPGA通過ICAP 對自身配置存儲器SEU 檢測資源使用情況Table2 Resource using condition when detecting SEU in FPGAconfiguration memory through ICAP by itself

3.2.2 通過SelectMap 接口SE U 檢測

本設計中選用Virtex II xc2v1500 代替反镕絲器件,對S RAM 型FPGA進行檢測。監控FPGA內部實現監控模塊、判決等功能,使用資源見表3。可見,通過SelectMap 接口實現SEU 檢測占用資源很少。

表3 通過SelectMap 回讀檢測SEU 資源占用情況Table3 Resource using condition when detecting SEU in FPGAconfiguration memory through Seletcmap

4 結論及展望

文章分析了S RAM 型FPGASEU 的特點,以及FPGA抗SEU 方法,并通過對配置數據進行回讀校驗的方法實現了SEU 檢測。

FPGA通過ICAP可以實現自身SE U 檢測,但由于檢測模塊運行于FPGA內部,也可能發生SEU,可以通過對檢測模塊進行三模冗余設計提高可靠性,另外可以采用片外反镕絲器件通過Select-Map 接口對FPGA配置存儲器進行回讀,實施SEU 檢測是更加可靠的辦法。

References)

[1]Roosta R.AComparison of radiation-hard and radiation-tolerant FPGAs for space applications[R].NAS A,DEC,2004

[2]Carmichael C.Triple module redundancy design techniques for Virtex series FPGA[EB/OL].(2006-07-06).[2009-07-30]http://www.XILINX.com/hvdoes/apnotes/xapp197.pdf

[3]賀朝會,陳曉華,李國政.高能質子單粒子翻轉效應的模擬計算[J].計算物理,2002,19(4):367-371

[4]Samudrala P K,Ramos J,Katkoori S.Selective triple modular redundancy (STMR)based single-event upset(S EU)tolerant synthesis for FPGAs[J].IEEE Transactions on Nuclear Science,2004,51(5)

[5]Fuller E,Caffrey M ,Salazar A,et al.Radiation testing update,SE U mitigation,and availability analysis of the Virtex FPGAfor space reconfigurable com puting[C]//4thAnnual Conference on Military and Aerospace Programmable Logic Devices(MAPLD).Washington DC:NASAOffice of Logic Design,September 2000

[6]Carmichael C,Fuller E,Blain E A.SEU mitigation techniques for Virtex FPGAs in space applications[C]// Proceeding of the Military and Aerospace Programmable Logic Devices and Technology Conference,1999

[7]Shubhendu S M,Emer J,Fossum T,et al.Cache scrubbing in microprocessors:mythor necessity [C]//PRDC' 04:10thIEEE Pacific Rim International Symposium on Dependable Computing.Tahiti,French Polynesia,2004

[8]Robert F,H odson1,Somervill K,et al.An architecture for reconfigurable computing in space[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference (MAPLD),Washington DC:NASAOffice of Logic Design,Sepetmber 2005

[9]Nishinaga N,Takeuchi M,Suzuki R.Reconfigurable communication equipment on smartSat-1[C].Military and Aerospace Applications of Programmable Devices and Technologies Conference (MAPLD),Washington DC:NASAOffice of Logic Design,September 2004

[10]邢克飛,楊俊,王躍科,等.XILINX SRAM 型FPGA抗輻射技術研究[J].宇航學報,2007,28(1)

[11]Yui C,Swif t G,Carmichael C.Single event upset susceptibility testing of the XILINX Virtex II FPGA[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference(MAPLD).Washington DC:NAS AOffice of Logic Design,September 2002