基于FPGA的SOPC設計

王 培元

(襄樊學院 物理與電子工程學院,湖北 襄樊 441053)

基于FPGA的SOPC設計

王 培元

(襄樊學院 物理與電子工程學院,湖北 襄樊 441053)

本SOPC系統在Altera 公司Cyclone 系列芯片EP1C6Q240中移植Nios II嵌入式處理器,作為核心控制電路;利用FPGA豐富的可編程邏輯資源和IP軟核構成嵌入式處理器的接口模塊,實現對SDRAM存儲器、FLASH存儲器、LCD液晶顯示器、獨立鍵盤、LED等硬件的控制;軟件設計采用開源的uC/OS-II嵌入式實時操作系統,完成一個嵌入式系統硬件設計. 經調試運行,在該系統上成功進行了推箱子游戲,驗證了基于FPGA硬件設計的可行性,實現嵌入式實時多任務軟件的開發.

FPGA;SOPC;Nios II;uC/OS-II

SOPC(System-on-a-Programmable-Chip),全稱是可編程片上系統. 首先它是片上系統(SOC),即由單個芯片完成整個系統的主要邏輯功能;其次,它是可編程系統,具有靈活的設計方式,可裁減、可擴充、可升級,并具備軟硬件在系統可編程的功能[1]. 隨著FPGA芯片的發展,SOPC技術的得到了飛速發展,利用FPGA設計SOPC,為現在越來越復雜的產品所帶來的競爭壓力提供了高效的解決方案,在高速等高端產品中應用越來越廣泛.

SOPC設計是nios系統+硬實時部分+邏輯電路的一個組合體. 其中硬實時部分和邏輯電路在FPGA芯片內可以完美的得到實現. 本設計采用ALTERA公司的Nios II軟核和FPGA芯片EP1C6Q240實現了一個SOPC的設計.

1 系統總體設計

本 SOPC系統主要實現推箱子游戲,系統由一個 32bit NiosII軟核處理器、液晶顯示器、SDRAM、FLASH、鍵盤等組成。設計的關鍵是定制Nios II軟核處理器以及處理器與外圍器件的接口電路.

1.1 系統總體結構

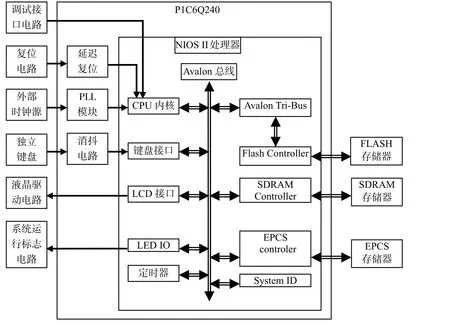

系統總體硬件結構如圖1所示. 整個系統由FPGA的片上系統和片外硬件電路構成[5]. FPGA片外電路包括LCD液晶顯示電路、獨立鍵盤電路、系統運行指示電路、SDRAM存儲器電路、FLASH存儲器電路、EPCS存儲器、復位電路及時鐘源電路、調試接口及所需要的電源電路等. FPGA片上系統包括Nios II軟核處理器、延遲復位模塊、PLL鎖相環模塊、鍵盤消抖模塊等[2-4].

1.2 Nios II軟核處理器的定制

系統中的 Nios II軟核處理器作為核心控制器件,連接了鍵盤和液晶屏等輸入輸出設備及 FLASH、SDRAM、EPCS等存儲器,控制著整個系統. Nios II軟核處理器的定制是通過ALTERA公司的SOPC Builder系統綜合軟件來完成的. 在定制中要注意處理器的時鐘頻率,外部RAM總線(Avalon三態橋)、外部RAM接口、外部Flash接口、鍵盤PIO、LCD數據線及控制信號線、LED PIO、定時器、System ID的參數設置.

1.3 液晶顯示器接口

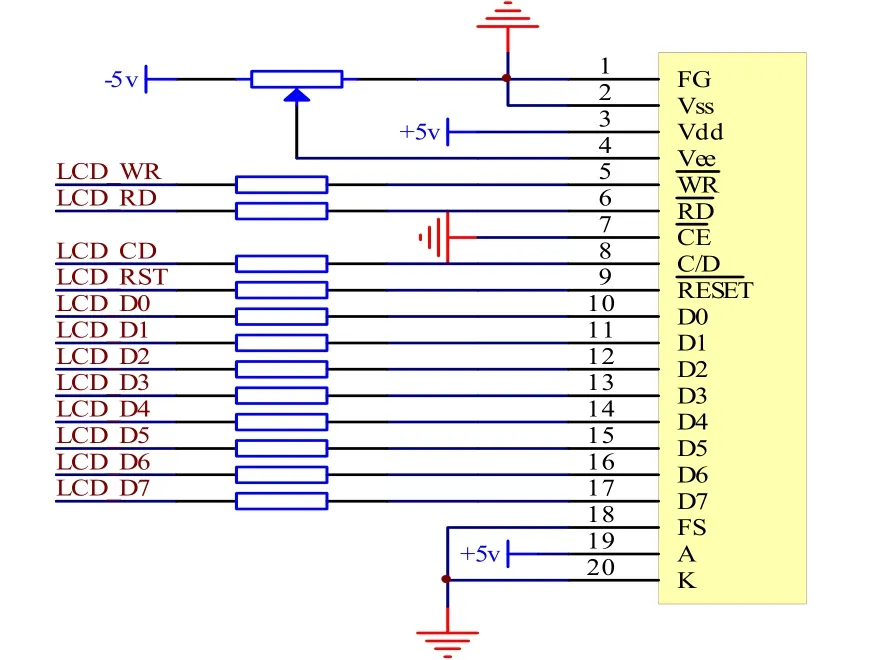

液晶顯示器以其低功耗、體積小、顯示內容豐富、模塊化和接口電路簡單等優點在各個領域得到廣泛的應用. 本系統液晶顯示規格為320*240,接口如圖2所示,LCD_WR、LCD_RD、LCD_CD、LCD_RST分別為液晶顯示器的寫、讀、命令/數據選擇和復位等端口,LCD_D0~ LCD_D7為8bit數據端口,這些端口都與FPGA連接. FPGA與液晶之間通過電阻實現3v與5v電平匹配.

1.4 SDRAM存儲器

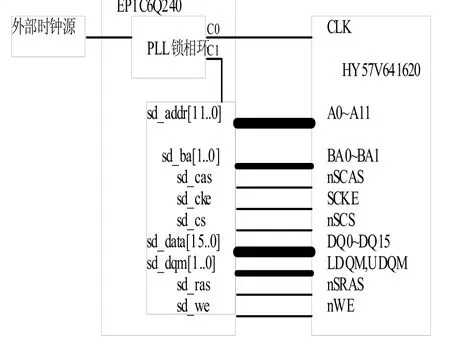

系統使用的SDRAM是HYNIX公司的HY57V641620,這是一款具有64Mbit容量16位寬的SDRAM,最高工作時鐘可達200M. 設計中建立了一個SDRAM與Avalon總線的結合體,對Avalon端的地址、數據線操作,Avalon總線便會完成對SDRAM的讀寫. FPGA與SDRAM連接圖如圖3所示.

圖1 系統總體結構

圖 2 液晶顯示電路

圖3 SDRAM與FPGA連接圖

1.5 FLASH存儲器

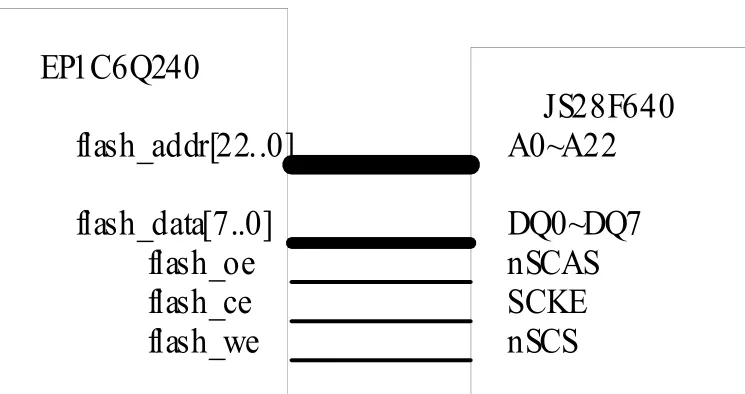

本設計中采用的FLASH是Intel公司的JS28F640,具有8MByte容量,其數據線可以8bit或16bit方式連接到處理器上,兼容32MByte. 系統中用一個Avalon三態橋和FLASH控制器實現Nios II處理器與FPGA片外的FLASH讀寫操作. FPGA與FLASH連接圖如圖4所示.

圖4 FLASH與FPGA連接圖

2 軟件設計與實現

Nios II系統支持uC/OS-II、uCLinux、eCOS等嵌入式實時操作系統,其中Altera提供對uC/OS-II的完整支持. uC/OS-II是一個完整的、可移植、固化和裁減的占先式實時多任務內核.

2.1 任務劃分

按照系統所要求實現的功能,將整個系統劃分為幾個并行存在的任務,系統創建了4個任務. 分別實現系統初始化任務、鍵盤處理、系統運行標志處理等.

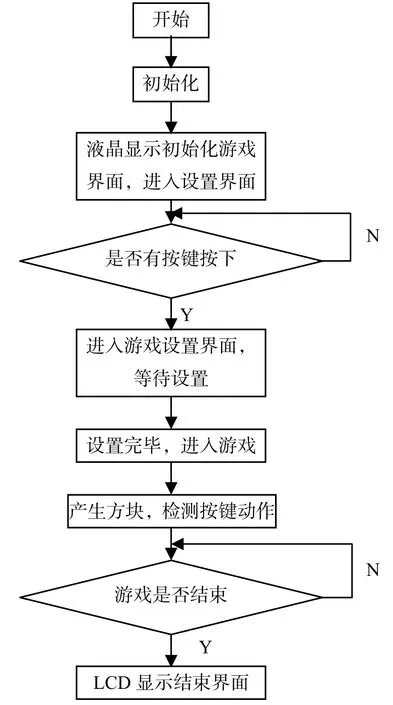

系統初始化任務主要用來對系統中所使用的I/O端口、LCD液晶、外部按鍵中斷、任務創建的進行初始化設置;鍵盤處理任務是根據外部鍵盤中斷產生的按鍵值,以信號量的方式發送出去,實現簡單的通信;系統運行標志處理任務,主要標志uC/OS-II時刻都在運行著. 系統軟件設計流程圖如圖5所示.

2.2 推箱子游戲的實現

LCD液晶顯示器分成2部分,左半邊64×64點作為游戲圖形界面的顯示,右半邊作為游戲信息等漢字顯示區域. 左半邊需要顯示8×8的模擬圖形,以左上角為原點,以橫向為x軸,以縱向為y軸,建立一個橫向坐標范圍0~7,縱向坐標范圍0~7的游戲界面區域. 右半邊可以隨意顯示任何信息,包括游戲的等級數、設計者等. 在推箱子游戲中使用了5個模擬圖形,依次為人物、磚頭、箱子、目標、成功. 這些圖形由8×8點陣形式顯示.

在構建完成游戲界面后,可以通過向上、向下、向左、向右的按鍵控制人物去尋找箱子,并將箱子推到目的地. 系統中游戲設置了8個等級,操作者可以一關一關的進行游戲,也可以通過選關按鍵選擇游戲的等級.

圖5 系統軟件設計流程圖

3 結語

系統完成基于FPGA的嵌入式系統設計后,通過調試完成各項功能. 不僅體現了FPGA在硬件環節中設計的方便性,在軟件環節中更是完整地支持了開源的uC/OS-II.

雖然系統功能已經基本實現,但是仍然存在不足之處,還需要改進. 鍵盤消抖電路使用計數延時的方法處理鍵盤抖動,但實際仍出現一定的誤差,有待改進. 系統使用變壓器電源,可將電源改進后采用小型電源供電,系統就可成為便攜式設備.

[1] 周立功. SOPC嵌入式系統實驗教程(一)[M]. 北京: 北京航空航天大學出版社, 2007.

[2] 怯肇乾. FPGA-SOPC軟硬件協同設計縱橫談[J]. 單片機與嵌入式系統應用. 2008(9): 8-11.

[3] 楊志坤, 曾 博, 湯國文. 基于FPGA的嵌入式系統USB接口設計[J]. 電子設計工程, 2010(01): 30-34.

[4] 利劍清, 宋 躍, 林明仁, 等. 基于FPGA/SOPC-Nios II的頻率計數器設計[J]. 東莞理工學院學報, 2008, 15(3): 53-57.

[5] Altera Corporation. Nios II Hardware Development Tutorial[M/OL]. Version 6.0. [S.l.]: [s.n.], 2006[2010-05-05]. http://www. Docin/p-35566317. html.

Design for Embedded System Based on FPGA

WANG Pei-yuan

(School of Physics and Electronic Engineering, Xiangfan University, Xiangfan 441053, China)

In the system of SOPC, Nios II embedded processor as the controlling core is embedded into a EP1C6Q240 of Altera Cyclone series. And the abundant programmable logical resources and IP core make up of the processor of peripheral interface controlling circuit, which provide SDRAM controlling, FLASH controlling, LCD display controlling, keyboard controlling, LED controlling, and so on. The system of the hardware design is realized and validated successfully by the result of testing that the game can play in the system and the software design of embedded multi-tasking operating system is realized, too.

FPGA;Embedded;Nois II;IP core;uC/ OS-II

TN47

A

1009-2854(2010)08-0042-03

2010-06-18;

2010-08-08

王培元(1973— ), 男, 湖北宜城人, 襄樊學院物理與電子工程學院講師.

饒 超)