DFT頻譜分析系統(tǒng)的FPGA設(shè)計(jì)與實(shí)現(xiàn)

陳至坤,李 勝,陳 韜,王福斌,孫曉磊

(1.河北理工大學(xué)計(jì)算機(jī)與自動控制學(xué)院,河北 唐山063009;2.天津市德力電子儀器有限公司,天津300113;3.東北大學(xué)機(jī)械工程與自動化學(xué)院,遼寧 沈陽110004;4.天津大學(xué)電信學(xué)院,天津300072)

0 引言

有限長序列離散傅里葉變換(discrete Fourier transform,DFT)和快速傅里葉變換(FFT)是數(shù)字信號頻譜分析的基本算法。一般來說,F(xiàn)FT算法由于利用了DFT的一些固有特性,減少了DFT運(yùn)算量,是計(jì)算信號頻譜的常用方法,但是在某些實(shí)際應(yīng)用場合,應(yīng)用DFT完成系統(tǒng)設(shè)計(jì)與FFT相比更有優(yōu)勢[1]。數(shù)字信號處理系統(tǒng)過去常采用高速的ASIC器件來實(shí)現(xiàn)。然而,隨著半導(dǎo)體器件技術(shù)的發(fā)展,這些專用器件已經(jīng)逐漸由現(xiàn)場可編程(邏輯)門陣列(field programmable gate arrays,F(xiàn)PGA)代替。FPGA具有高速度、高集成度和高可靠性,而且具有用戶可編程特性,能降低設(shè)計(jì)風(fēng)險(xiǎn)。基于FPGA的DFT頻譜分析系統(tǒng),

可以用硬件實(shí)現(xiàn)軟件算法,大大提高了運(yùn)算速度,解決了DFT運(yùn)算量大、消耗時(shí)間長、實(shí)時(shí)性不好等實(shí)際應(yīng)用的問題。另外,在用FPGA計(jì)算頻譜時(shí),速度已不是頻譜計(jì)算的瓶頸,更重要的是資源的合理應(yīng)用[2]。本文將詳細(xì)介紹DFT頻譜分析算法的FPGA設(shè)計(jì)與實(shí)現(xiàn)。

1 DFT頻譜分析系統(tǒng)總體設(shè)計(jì)

DFT頻譜分析算法的數(shù)學(xué)公式為

式中 x(n)為時(shí)域信號,X(k)為頻域信號。根據(jù)DFT算法的數(shù)學(xué)公式,DFT頻譜分析系統(tǒng)總體設(shè)計(jì)如圖1所示。系統(tǒng)以二分頻高速A/D的轉(zhuǎn)換頻率為時(shí)鐘。經(jīng)過高速A/D轉(zhuǎn)換后的數(shù)字化實(shí)信號,先由雙端口RAM采集。然后,在時(shí)鐘的控制作用下,依次進(jìn)行數(shù)據(jù)加窗、數(shù)字下變頻、累加、平方、求和、開方運(yùn)算,最終將處理結(jié)果存儲。圖1所示所有的工作全部在FPGA中完成。同時(shí),整個(gè)頻譜分析系統(tǒng)需要外部MCU(單片機(jī)或DSP)發(fā)送重置、開始、停止等控制命令字并對處理完成的數(shù)據(jù)進(jìn)一步傳輸和顯示。

圖1 系統(tǒng)總體框圖Fig 1 Overall block diagram of the system

2 主要功能模塊的設(shè)計(jì)

2.1 信號采集存儲模塊

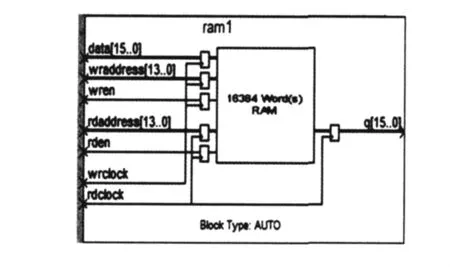

數(shù)字信號采集存儲模塊的設(shè)計(jì),既要求能準(zhǔn)確采集所需點(diǎn)數(shù)的數(shù)據(jù),同時(shí)也要為后續(xù)數(shù)據(jù)處理做準(zhǔn)備。雙口RAM具有兩套完全獨(dú)立的數(shù)據(jù)線、地址線和讀寫控制線,并允許2個(gè)獨(dú)立的系統(tǒng)同時(shí)對該存儲器進(jìn)行隨機(jī)性的訪問。使用雙端口RAM提高了RAM的吞吐率,不會造成大數(shù)據(jù)量情況下數(shù)據(jù)堵塞的現(xiàn)象,適用于實(shí)時(shí)的數(shù)據(jù)緩存。設(shè)計(jì)中采用了雙端口RAM作為信號采集存儲模塊。圖2所示為雙端口RAM的邏輯結(jié)構(gòu)圖。

圖2 雙端口RAM邏輯結(jié)構(gòu)Fig 2 Logic structure of dual-port RAM

在圖2中,data為A/D輸入數(shù)據(jù);wraddress為14位寬寫入端的地址,可以尋址16384個(gè)單元,滿足每一次操作存儲采樣數(shù)據(jù)的要求;wren為寫入端的寫使能信號;inclock為寫入端的時(shí)鐘,因?yàn)樵O(shè)計(jì)采用是時(shí)序電路,所以,電路中的任何動作都要在時(shí)鐘的驅(qū)動下進(jìn)行。q,rdaddress,rden,outclock分別為雙口RAM讀出端數(shù)據(jù)線,地址線,讀使能以及該端的時(shí)鐘。數(shù)據(jù)的寫入時(shí)鐘是A/D的轉(zhuǎn)換時(shí)鐘166.4 MHz,后續(xù)系統(tǒng)的讀取時(shí)鐘為83.2 MHz。讀取時(shí)鐘遠(yuǎn)比寫入的速度慢,保證了數(shù)據(jù)的準(zhǔn)確性和穩(wěn)定性。

2.2 窗函數(shù)選擇與存儲模塊

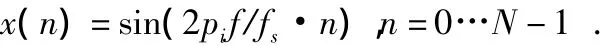

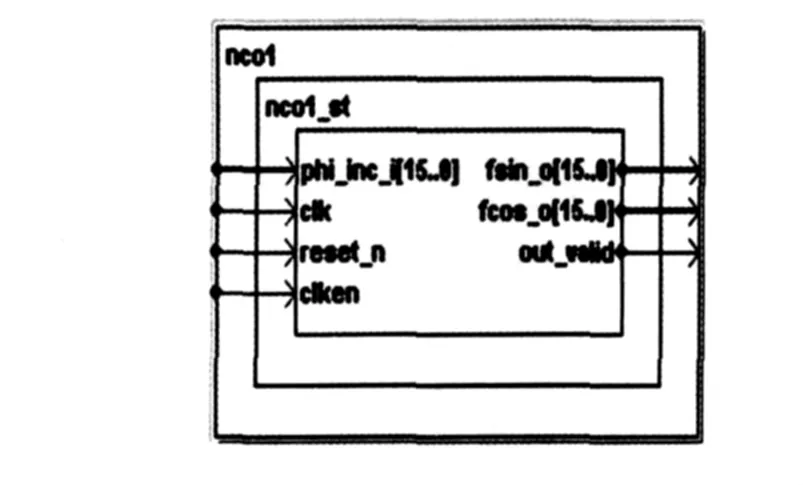

由于矩形窗對信號進(jìn)行截取會造成“頻譜泄漏”,所以,需要改用其他窗函數(shù)對信號進(jìn)行截取。常用的窗函數(shù)有漢寧窗、海明窗、布萊克曼窗、布萊克曼—哈里斯窗等,通過對幾個(gè)窗函數(shù)參數(shù)的比較,設(shè)計(jì)中選用布萊克曼窗作為窗函數(shù)。由于各個(gè)窗函數(shù)的頻譜是不同的,所以,同樣的RBW在不同的窗函數(shù)下對應(yīng)的處理數(shù)據(jù)點(diǎn)數(shù)也是不同的。一個(gè)N點(diǎn)正弦采樣信號

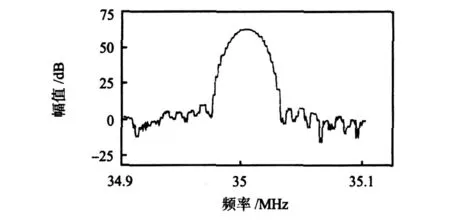

其DTFT模的波形在分貝圖上看,3dB處寬度對應(yīng)著的模擬的頻率就應(yīng)該為RBW。有限長度正弦數(shù)字信號加上布萊克曼窗后的取分貝的頻譜圖如圖3所示,從圖中可以看出:3 dB帶寬對應(yīng)的角頻率差為1.65×2π/N,對應(yīng)的模擬頻率為1.65 fs/N,所以,需要采樣數(shù)據(jù)點(diǎn)數(shù)N=1.65fs/RBW。

圖3 有限長正弦數(shù)字信號加布萊克曼窗后取分貝的頻譜圖Fig 3 Spectrum of finite sinusoidal digital signal multiply Blackman window

通過Matlab軟件,生成所需點(diǎn)數(shù)窗的值,存入FPGA創(chuàng)建的ROM模塊之中,按照時(shí)鐘的時(shí)序?qū)OM中存儲的窗函數(shù)值依次與A/D轉(zhuǎn)換后的數(shù)據(jù)相乘,從而實(shí)現(xiàn)數(shù)據(jù)加窗的操作過程。因?yàn)榇昂瘮?shù)具有對稱性,所以,在設(shè)計(jì)中只需要存入對稱的一半窗函數(shù)的值即可,這樣可以減少存儲器資源,節(jié)約硬件成本。

2.3 NCO IP Core模塊

為了縮短開發(fā)設(shè)計(jì)周期,減少設(shè)計(jì)風(fēng)險(xiǎn)和資金投入,同時(shí)提高性能和可靠性,本設(shè)計(jì)采用Altera公司NCO模塊IP核實(shí)現(xiàn)數(shù)字下變頻[3]。

IP核(intellectual property core)是FPGA廠商和第三方預(yù)先設(shè)計(jì)好各種通用單元并根據(jù)各種FPGA芯片的結(jié)構(gòu)對布局和布線進(jìn)行優(yōu)化,從而構(gòu)成具有自主知識產(chǎn)權(quán)的功能模塊。IP核具有重用性,適用于不同的系統(tǒng)。IP模塊可分為硬件(Hard IP)模塊、軟件(Soft IP)模塊和固件(Firm IP)模塊 3 種[4]。

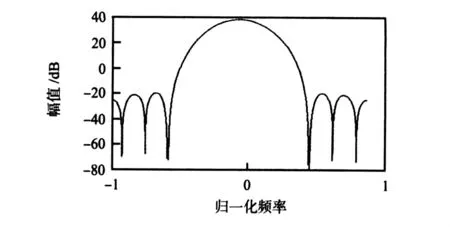

在本設(shè)計(jì)中數(shù)控振蕩器(numerically controlled oscillator,NCO)用來產(chǎn)生頻率可變的正余弦樣本。NCO V 7.2是Altera公司2007年發(fā)布的 NCO IP core,支持該公司的Cyclone,Stratix等系列FPGA器件。該NCOIPcore提供Small ROM,Large Rom,CORDIC,Multiplier-Based 4種結(jié)構(gòu)的 NCO設(shè)計(jì)。本設(shè)計(jì)采用CORDIC算法實(shí)現(xiàn)。采用CORDIC算法實(shí)時(shí)計(jì)算正余弦樣本,避免了采用Small ROM,Large Rom查找表結(jié)構(gòu)耗費(fèi)大量ROM資源和使用Multiplier-Based乘法器結(jié)構(gòu)需要DSP模塊,對FPGA的要求高的缺點(diǎn)[5]。

在QuartusII 7.2中,選擇 tools->Mega Wizard Plug-In Manager,然后,選擇 DSP->Signal Generation->NCO V 7.2創(chuàng)建NCO模塊。NCO模塊邏輯結(jié)構(gòu)如圖4所示。

圖4 NCO模塊邏輯結(jié)構(gòu)圖Fig 4 Logic structure diagram of NCO module

NCO模塊共有4個(gè)輸入量,分別為時(shí)鐘信號,時(shí)鐘使能,相位增量和復(fù)位。在對時(shí)鐘信號,時(shí)鐘使能,相位增量設(shè)置完初值后,當(dāng)復(fù)位信號由低置為高后,NCO產(chǎn)生相應(yīng)的正弦和余弦輸出。

3 NCO模塊對系統(tǒng)的精度影響分析

NCO能否準(zhǔn)確地產(chǎn)生所需頻率正交的正弦和余弦樣本,將會影響頻譜分析系統(tǒng)的精度。

影響數(shù)字下變頻性能的主要因素有2個(gè):一是表示數(shù)字本振、輸入信號以及混頻乘法運(yùn)算的樣本數(shù)值的有限字長所引起的誤差;二是數(shù)字本振相位的分辨率不夠而引起數(shù)字本振樣本數(shù)值的近似取值。也就是說,如果數(shù)字混頻器和數(shù)字本振的數(shù)據(jù)位數(shù)不夠?qū)挘痛嬖谥矓?shù)截?cái)嗟那闆r,數(shù)字本振相位的樣本值存在近似的情況,則根據(jù)截?cái)嗪徒频某潭龋瑫蚨嗷蛏俚赜绊慛CO的性能[7]。

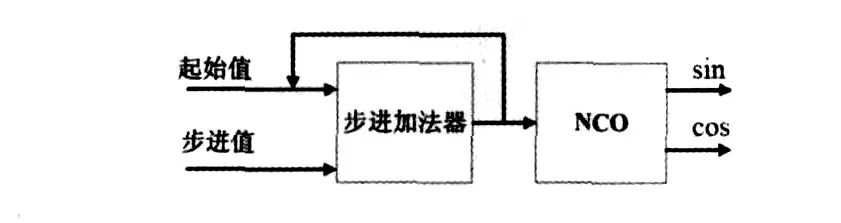

設(shè)計(jì)中每計(jì)算一個(gè)頻域點(diǎn)值,就需要相應(yīng)頻率的正余弦樣本,因?yàn)橄噜忣l域點(diǎn)值的頻率差值是固定的,所以,生成的正余弦樣本值的頻率差值也是固定的,設(shè)計(jì)中在NCO模塊輸入前加入一個(gè)加法器,加法器的2個(gè)加數(shù)分別稱起始值和步長值,初值由第1個(gè)頻點(diǎn)值確定,步長值由相鄰頻點(diǎn)的頻率差值確定。步長值和初值數(shù)值的確定參照NCO IP core說明文檔中具體公式。圖5所示為NCO模塊前的加法器模塊。

圖5 NCO模塊輸入部分結(jié)構(gòu)圖Fig 5 Input part structure diagram of NCO module

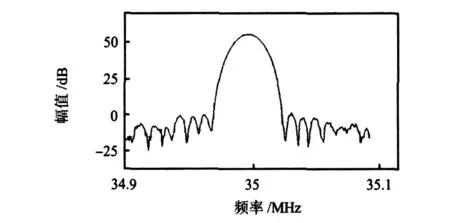

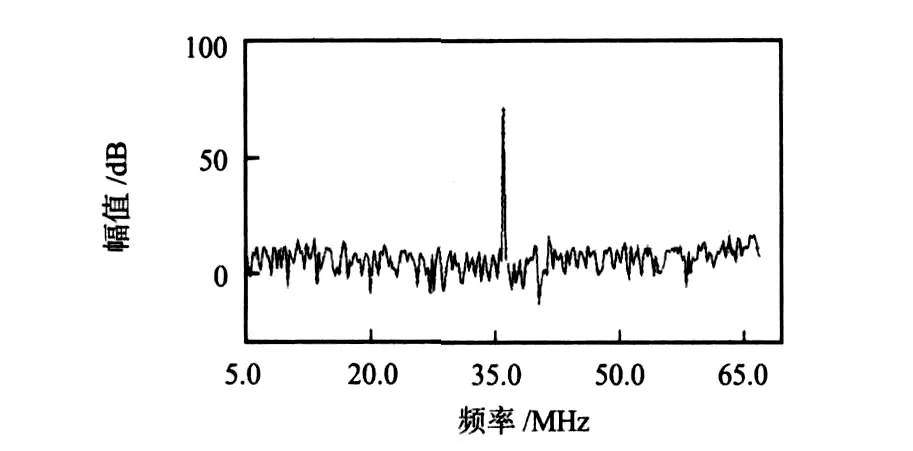

實(shí)驗(yàn)中發(fā)現(xiàn),當(dāng)NCO輸入精度為16位,有步進(jìn)值加入時(shí),輸出正余弦樣本的頻率并沒有發(fā)生變化,仍然保持未加步進(jìn)時(shí)的值。當(dāng)NCO輸入精度為32位,有步進(jìn)值加入時(shí),輸出正余弦樣本能夠比較準(zhǔn)確地輸出相應(yīng)的頻率。因此,正余弦樣本能否正確的產(chǎn)生取決于NCO模塊輸入的數(shù)字本振相位的分辨率精度。NCO模塊輸入數(shù)字本振相位的分辨率精度不夠的時(shí)候,輸入值有較小變化的時(shí)候,輸出不變,從而造成輸出正余弦樣本不準(zhǔn)確。圖6所示為NCO在16位精度輸入在200 kHz的span下的頻譜圖,從圖中可以看到頻譜圖有明顯的“階梯狀”。圖7所示為NCO在32位精度輸入在200kHz下的頻譜圖。在32位精度輸入下信號頻譜更加精細(xì)。

圖6 16位精度輸入200 k Hz span頻譜分析結(jié)果圖Fig 6 Spectrum analysis result diagram of 16-bit precision input with 200 kHz span

圖7 32位精度輸入200 k Hz span頻譜分析結(jié)果圖Fig 7 Spectrum analysis result diagram of 32-bit precision input with 200 kHz span

4 DFT頻譜分析系統(tǒng)的實(shí)現(xiàn)與性能分析

本設(shè)計(jì)采用Altera公司的Cyclone III系列的EP3C25E144C8芯片,在QuartusII 7.2版本開發(fā)平臺上實(shí)現(xiàn)。Cyclone III是Altera公司2007年生產(chǎn)的系列器件,采用了交叉I/O環(huán),寬列低成本包裝,支持低成本閃存。CycloneIII器件是低功耗的65 nm的FPGA,未使用的I/O塊被置為低電平。Cyclone III增加了系統(tǒng)的集成度,密度高達(dá)119088個(gè)邏輯單元,存儲器高達(dá)3.8 Mbits,其內(nèi)部有4個(gè)鎖相環(huán),提供了強(qiáng)大的時(shí)鐘控制,可綜合器件時(shí)鐘、外部時(shí)鐘和I/O接口,可以支持高達(dá)400 Mbps的外部高速存儲器。

在具體的實(shí)現(xiàn)過程中,為了加快DFT頻譜分析系統(tǒng)的速度,采用了兩條相同的DFT處理結(jié)構(gòu),并行處理,并將處理結(jié)果依次存儲。從而使整個(gè)DFT處理的時(shí)間減半。實(shí)驗(yàn)驗(yàn)證過程中,在5~65MHz范圍內(nèi)輸入35MHz單一信號,將處理完成的數(shù)據(jù)輸入到DSP處理芯片中,結(jié)合Visual DSP++調(diào)試工具,得到圖8所示的仿真結(jié)果。驗(yàn)證過程中還分別對不同中心頻率,不同的span下的情況下進(jìn)行了仿真,仿真結(jié)果驗(yàn)證了DFT頻譜分析系統(tǒng)的正確性。

圖8 32位精度輸入60MHz span下35MHz信號頻譜分析結(jié)果圖Fig 8 35 MHz signal spectrum analysis result diagram of 32-bit precision input with 60 MHz span

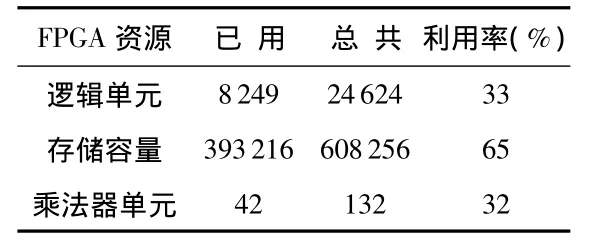

表1所示為系統(tǒng)采樣16 384數(shù)據(jù)點(diǎn)值,采用二路并行處理下的FPGA的資源消耗,系統(tǒng)工作頻率為83.2MHz,每場數(shù)據(jù)處理時(shí)間為22 ms。

表1 并行處理結(jié)構(gòu)下頻譜分析系統(tǒng)資源消耗量Tab 1 Resource consumption of the system

在相同的條件下,采用Altera公司的FFT IP core V 7.2設(shè)計(jì)的FFT頻譜分析系統(tǒng),占用的存儲單元容量為1060160。遠(yuǎn)遠(yuǎn)超過了選用FPGA芯片的存儲容量,造成成本的增加。

5 結(jié)束語

本文設(shè)計(jì)與實(shí)現(xiàn)了一種適合FPGA實(shí)現(xiàn)的DFT頻譜分析系統(tǒng),本系統(tǒng)全部由VHDL語言實(shí)現(xiàn)。實(shí)驗(yàn)結(jié)果表明:該設(shè)計(jì)采用NCOIPcore實(shí)時(shí)計(jì)算需要的正余弦樣本,能夠比較合理地利用FPGA資源。對于本系統(tǒng)需要處理16 384采樣點(diǎn)數(shù)據(jù)的要求,采用DFT頻譜分析算法雖然比FFT算法消耗時(shí)間長,但可以節(jié)省大量的芯片資源,同時(shí)由于FPGA器件處理速度的快速性,整個(gè)系統(tǒng)22 ms處理一場數(shù)據(jù)滿足應(yīng)用要求。此外,該系統(tǒng)還具有功耗低、接口簡單、系統(tǒng)外部只需要一些簡單的控制信號便于移植到其他系統(tǒng)中去的優(yōu)點(diǎn),具有很強(qiáng)的應(yīng)用價(jià)值。

[1]邱寬民,趙勝凱.DFT與FFT在實(shí)際應(yīng)用時(shí)的性能比較[J].北方交通大學(xué)學(xué)報(bào),2000(10):60-62.

[2]陳永東.一種基于FPGA的DFT算法實(shí)現(xiàn)的研究[J],遙測遙控,2005(7):53-69.

[3]劉祖深.頻譜分析儀全數(shù)字中頻設(shè)計(jì)研究與實(shí)現(xiàn)[J],電子測量與儀器學(xué)報(bào),2009(2):39-49.

[4]竇秀梅,趙振綱.基于IP核的FPGA FFT算法模塊的設(shè)計(jì)與實(shí)現(xiàn)[J].無線電工程,2008(8):29-31.

[5]陳紹寬,李 明.NCO的研究及其FPGA實(shí)現(xiàn)[J].儀表技術(shù),2006(5):30-32.

[6]NCOMega Core Function User Guide[EB/OL].[2007—10—01].http://www.altera.com.

[7]何水艷.淺析數(shù)字下變頻中的NCO[J].高等函授學(xué)報(bào):自然科學(xué)版,2004(2):53-56.