多功能數據采集處理系統實現

趙 磊

引言

數據采集與處理系統的設計是現代信號處理系統的基礎,被廣泛應用于雷達、通信、圖像處理等領域。近年來,隨著信息科學的高速發展,人們面臨的信號處理任務越來越繁重,對實時信號數據采集處理系統的要求也越來越高。所用系統要求具有處理大量高速數據的能力,這就要求系統硬件達到很高的運算速度,并且軟件處理程序也盡可能優化,以保證系統的實時性。同時,伴隨著電子產品應用的多樣化,電路設計的通用性也受到了大家的重視。

器件選型

A/D采樣芯片

凌力爾特(Linear)的LTC2260是一種14 bit ADC,它具有105 Msps的采樣率,功耗僅為106m,顯著減少了用于高速數據采集的功率預算,同時集成有高性能采樣保持電路,提供CMOS兼容的輸出,輸入信號和采樣時鐘均支持差分模式。LTC2260具有以下特點:信噪比73.4dB,無雜散動態范圍85dB,單1.8V電源,滿功率帶寬800MHz,CMOS、DDR CMOS或DDR LVDS輸出,可選輸入范圍1VP-P至2VP-P。

FPGA

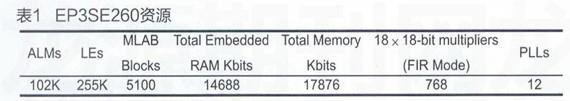

在FPGA的選型中,通過對算法所需資源的估算和充分考慮器件的適用性,選用Altera公司StratixⅢ系列的EP3SE260。

StratixⅢ擁有功能強大的DSP模塊,速度高達550MHz,具有896個18×18的乘法器,支持可變位寬,支持基本乘法器、求和、累加、級聯、取整、飽和以及桶形移位寄存器等功能。EP3SE260資源如表1所示。

DSP

本設計中DSP選用ADI公司的新一代ADSP TS201s數字信號處理器,兼有FPGA和ASlC信號處理性能和指令集處理器的高度可編程性,適用于大存儲量、高性能、高速度的信號處理領域。ADSP TS201S采用超級哈佛結構,靜態超標量操作適合多處理器模式運算,可直接構成分布式并行系統和共享存儲式系統,專為大的信號處理任務和通信結構優化。

硬件電路設計

本系統中設計了四路A/D,采樣后的數字信號送到FPGA進行預處理,FPGA同時為系統提供時鐘、對A/D和D/A進行控制、與DSP進行數據交換、還要為CPCI接口的實現提供時序邏輯和通信接口,DSP做相應的算法處理,四路D/A可提供測試信號和自檢信號,系統結構框圖如圖1所示。

A/D電路

高速A/D芯片的輸入端通常采用差分輸入,這種方式有以下優點:差分特性對來自電源和其他電路的外部共模噪聲源具有抑制作用;能夠抵消偶次諧波;每個差分輸入所需電壓擺幅僅為單端輸入時的50%。可以降低對電源的要求。

本設計中運放采用的是ADI公司的AD8138,體積非常小巧,使得A/D芯片與信號輸入點的距離可以很近,大大減少了外界噪聲的影響,是理想的驅動芯片。單端轉差分器件選用Mini-Circuits公司的寬帶變壓器ADT1-1WT,其工作頻帶為0.4~800MHz,配合簡單的電阻網絡及濾波電容就可以完成設計任務了。

LTC2260的工作時鐘由FPGA提供,輸出1.8V的并行數據到FPGA進行處理,FPGA采用2.5V的I/O電壓。

FPGA和DSP的設計

本系統采用松耦合結構設計,FPGA和DSP都有其各自獨立的存儲器,DSP和FPGA之間通過LINK進行互連,DSP與FPGA之間通信通過編寫FPGA仿TS201 Lib/K邏輯完成,DSP還可通過LINK與外部交換數據,系統結構框圖如圖2所示。這種連接方式的優點在于:

(1)DSP和EIFPGA片間數據交換數據率更高,最高可達4GB/s;

(2)DSP和FGPA可以同時訪問各自的外部存儲器,系統總的存儲帶寬較大;

(3)DSP和FPGA訪問外部存儲器的同時可以通過LINK鏈路進行數傳通信;

(4)系統硬件連線相對獨立,易實現。

FPGA接口設計

FPGA主要提供3個邏輯接口,分別為與DSP的LINK接口、外部存儲器sDRAM的接口以及系統的輸入輸出接口。與DSP的LINK接口采用IP核設計實現,接口能夠穩定工作在500MHz速度上,為FPGA和DDSP之間提供4GB/s的數據傳輸能力。

FPGA到SDRAM接口邏輯自行設計,與DSP外部存儲器相同采用4片K4SS11632M構成64bit的256MB存儲空間。接口工作在80MHz時鐘頻率,數據率為640MB/s。

FPGA的輸入輸出接口連接到系統外,因此采用LVDS協議來保證信號的穩定、準確傳輸,雙向備提供32bit數據寬度,采用250MHz的板間傳輸頻率,可以提供2GB/s的傳輸能力。

DSP總線接口設計

ADSP TS201外部總線支持多種不同的協議,并且可以通過編程進行配置。外部總線接口支持流水線協議,SDRAM協議和慢速設備協議。TS201可以采用流水線協議訪問存儲系統。另外TS201有片上的SDRAM控制器,支持與sDRAM的無縫連接。本設計中總線上的外設分別為SDRAM以及DSP加載程序的FLASH存儲器。

TS201處理器的sDRAM接口,支持1024、512、256字的頁面長度,通過對sDRCON寄存器的編程可實現頁面長度的選擇。同時sDRAM占用TS201的外部存儲空間地址,通過/MSSD3~0來確定SDRAM的地址空間范圍。本設計選用的sDRAM型號為K4S511632M,頁面長度為s12字,將四片SDRAM拼接成64位的總線寬度,實現與TS201的無縫接口的2S6MB存儲空間。

DSP進行運算除了其外部存儲器外,還需要對其自身進行程序加載的BOOT FLASH。本設計中使用AT49BV321,設計中FLAsH的cE信號需要使用DSP的BMS和MSO相與后給入,這樣才能保證可以通過DSP的外總線給FLASH進行在線編程。

系統應用

本文設計的高速數據采集與處理系統,借助上面介紹的硬件平臺,可以完成通用的數據采集與處理,其中關鍵的問題就是后續的處理系統設計,即后續的信號處理系統完成的算法與功能。針對輸入信號的不同以及高速數據采集與處理系統的用途,后續的信號處理算法也具有多樣性。

數字下變頻

對于接收通道送來的中頻信號,由于本系統采用了10SMsps的采樣率,故可以直接采樣后進行下變頻處理,如圖3所示。數字下變頻器的組成包括數字混頻器、數字控制振蕩器和低通

濾波器,全部可以在FPGA中實現,醫為通過軟件進行運算,乘法器和低通濾波器可以做到完全一致,解決了I、Q通道幅度不平衡的問題,數字下變頻器的控制和修改也更加容易。

脈壓

在雷達回波信號處理中,通常利用線性調頻信號脈沖壓縮技術來獲得高的距離分辨率,它可以在保證雷達作用距離的情況下提高雷達的距離分辨率。數字脈沖壓縮就是利用數字信號處理的方法來實現雷達信號的脈沖壓縮,分為時域和頻域兩種實現方式。一般而言,對于小時寬帶寬積信號,用時域脈壓較好,可以用專用的FIR濾波器或FPGA設計實現;但對于大時寬帶寬積信號,用頻域脈壓較好,一般采用FFT方法在頻域實現。由于DSP芯片具有很強的數據處理能力,完全能夠滿足雷達脈沖壓縮信號處理實時性的需求。

動目標檢測(MTD)

MTD是根據最佳濾波器理論發展起來的一種雷達信號處理技術。MTD濾波器是一組相鄰且部分重疊的窄帶濾波器組,覆蓋整個重復頻率的范圍。由于固定雜波和運動目標回波的多譜勒頻移不相同,利用多譜勒濾波器濾去固定雜波而取出運動目標的回波,就可以大大改善在雜波背景下檢測運動目標的能力。采用加權法的每個濾波器具有較低的副瓣,可以抑制運動雜波,還有在零頻附近的深凹口抑制固定雜波,具有較好的雜波抑制性能。MTD利用DSP內部的FFT運算實現相參積累,不但提高了系統輸出的信噪比,還增強了雷達在各種雜波以及干擾條件下的目標檢測能力。

上面舉了一些應用方面的例子,諸如MTI、CFAR、積累、求模以及目標錄取之類的應用,在本系統中也可以輕松地實現。

結語

本文提出了一種基于FPGA和DSP的高速數據采集處理系統設計方案。該設計具有一定的通用性和可擴展性,FPGA可完成高速數據的存儲與相應的數據預處理,為DSP分擔部分信號處理工作,且硬件實現速度快于DSP的數據處理;采用浮點DSP進行后續處理,提高了數據處理精度。該高速數據采集處理系統可以通過修改FPGA內部程序來實現其它功能擴展,并利用后續DsP的強大實時處理能力,完成更為復雜的數字信號處理,因此在工程應用上具有較強的通用性。

Tota IPON解決方案,適應多標準、多規范的電信市場應用

近日在北京舉辦的中國光網絡研討會上,PMC-Sierra&司帶來的TotalPON產品是為電信領域提供的一種完整解決方案。TotalPON是一款單芯片產品,只需一顆芯片、一款軟件,就可實現不同的PON標準,即目前市場上存在的兩套標準GPON和EPON,以及PON的下一代標準10GEPON和XGPON。因為這些標準實際上存在很多共性,不論是標準層面還是物理層上,以及相應的一些應用。同時在實施層面上,單就線卡而言,GPON和EPON也有很多相似的地方,如都有相應的處理器、交換器,不同的只是PON在光模塊這方面的差別,而這方面比較容易解決,因為都是可插拔的,這樣就誕生了TotalPON。