ProASIC3

隨著工藝的不斷進步,FPGA在邏輯密度、性能和功能上有了極大的提高,同時器件的成本也大幅下降,使得電子工程師逐漸傾向于在越來越多的產品中采用可編程邏輯器件。在突破了低功耗、低成本以及先進工藝的瓶頸后,FPGA不斷以其可編程和靈活性向更多領域滲透,而眾多廠商的加入更使得FPGA市場群星璀璨,FPGA的應用市場越來越廣泛、應用的價值也越來越大。

FPGA的發展令人矚目,從原來的晶體管、集成電路,再發展到簡單的PLD,例如GLA、GAL等,接著出現了CPLD和FPGA,整個過程漫長而又曲折。從1985第一顆FPGA的誕生到現在的20多年間,FPGA技術的發展讓人難以想象,速度、資源、集成度都超越了人們的想象,以至于各行各業都開始關注和了解FPGA。目前從工藝上大致可以分為3類FPGA:Flash工藝、SRAM工藝、Flash+SRAM工藝,每種工藝都有其優缺點,適應一定的場合。

本文主要介紹Flash工藝FPGA的內部架構,這是一種全新的技術,有助于讀者了解FPGA內部結構、資源和功能等,也為讀者對比現有的SRAM技術的FPGA提供參考依據。

1.ProASIC3的特點

ProASIC3是Actel第三代Flash架構FPGA中的第一個器件,是當前應用最廣泛的Flash FPGA,它主要面向消費、汽車及其它成本敏感的應用領域。由于它的特點非常突出,因此越來越多的工程師轉向使用ProASIC3,它具有如下特點:

·基于Flash架構,無須昂貴的配置芯片,單芯片解決方案;

·1.5萬到300萬個系統門,分類齊全,供用戶自主選擇;

·最大504kbit的雙端口RAM和Ikbit的用戶FlashROM存儲器;

·最大616個用戶可用I/O;

·最高350MHz的性能;

·具有128位的Flash Lock和128位的AES加密,保護設計不被盜取;

·具有很好的系統成本。

正因為上述的特點,Actel完全可以替換現有的CPLD和部分SRAM的FPGA,而且使產品更具特點,例如安全性更高、可靠性更強、更小的體積和更低的成本等。關于ProASIC3更詳細的優勢介紹已經在《Actel基于Flash架構的FPGA講座(1)》中描述,下面將介紹組成FPGA的部件有哪些?它們之間的關系又將是怎樣的?

2.先進的Flash開關

FPGA與ASIC最大的不同點是具有可編程的特點,從而使得FPGA非常靈活,可以實現多種不同用途的ASIC。所以FPGA被看作是一種通用的ASIC,我們可以通過編寫不同的代碼來改變其功能,但是FPGA內部并不是所有的部件都可以讓用戶修改的,只有那些連線之間的開關可以通過程序來改變,最終的程序代碼也是轉換成對這些開關的控制。開關的性能決定了FPGA的性能,ProASIC3采用了Flash開關,因此帶來的優點也是顯而易見的。下面我們來對比2種不同的開關結構,如圖1所示。

Flash開關采用一種稱為懸浮柵的技術來保存開關的狀態,將2個MOS管的柵極連接在一起,其中一個MOS管通過位選擇信號Bitl和Bit2來控制懸浮柵上的電子,從而實現編程、擦除、校驗等功能;另外一個MOS管用于互聯其它的部件。當懸浮柵上被充電時該MOS管導通,當懸浮柵的電子被移除時該MOS管被關閉。Flash的開關只用了2個MOS管,因此功耗和面積更小,更多的空間用于布線,而且這種結構具有非易性的特點。

SRAM的開關使用4個MOS管來實現一個開關結構,而且2個上拉電阻往往也用MOS管來代替,所以一般需要6個MOS管,這樣的結構功耗大,而且掉電后狀態無法保存。

3.精細顆粒的邏輯單元

Actel所有Flash架構的FPGA都采用了精細顆粒的邏輯單元,這是FPGA最基本的物理邏輯單元,每個FPGA廠家都會不同,但也各具優勢,有些廠家的邏輯單元為LE,而Actel的邏輯單元為Tile。Actel采用了精細顆粒的邏輯單元使得它的結構更加靈活,每個邏輯單元可以自由地轉換成觸發器或者查找表。觸發器可以實現時序邏輯,查找表可以實現組合邏輯,如圖2所示,其中邏輯單元內部除了一些門電路以外,還有許多可控的Flash開關,這些開關使得邏輯單元變得非常靈活,所以Actel的FPGA資源利用率可以在不影響性能的前提下接近100%。

而一般SRAM結構FPGA的邏輯單元,其內部結構都是固定的,無法靈活變動,內部由一個觸發器和一個LUT組成,這就是所謂的粗顆粒結構的邏輯單元,其最小的單元都至少由一個觸發器和一個LUT組成。當設計中只用到LUT時,另一半觸發器的資源就浪費了。

4.更優的布線資源

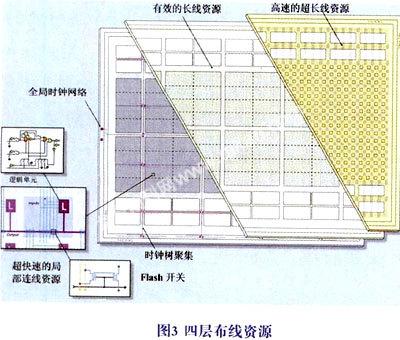

除了上述的2個資源外,FPGA很重要的一個組成部分就是布線資源,它直接影響設計的性能,足夠多的全局網絡可以讓更多高扇出的信號以最短的延時、最小的抖動到達每個觸發器,自然性能也將是最優的。ProASIC3具有7層金屬層,其中4層用于布線,分別為:超快速的局部連線資源、有效的長線資源、高速的超長線資源和高性能全局時鐘網絡,類似于PCB的多層板,如圖3所示。每種布線資源長短不一,根據實際情況供用戶選擇。

ProASIC3最多有18條全局網絡:6條片上全局網絡和12條象限全局網絡。在一般的設計中這些全局網絡已經足夠用,全局網絡可以走一些扇出特別大的信號,例如時鐘、復位等信號,而這些信號的路徑往往對一個系統性能起到了關鍵行性的作用。片上全局網絡與每個邏輯單元相連,而象限全局網絡與該象限內的邏輯單元相連,使得到達每個邏輯單元的時間最短,并且大致都相等。全局網絡也可以分段利用,這樣就會使得更多的信號上到全局網絡,提高系統的性能。

5.ProASIC3的片內外設

開關、邏輯單元、布線資源可謂是FPGA的內核構成,現在FPGA的集成度越來越高,很多的外設都集成在FPGA內部,例如PLL、RAM、ROM等,ProASIC3也不例外。

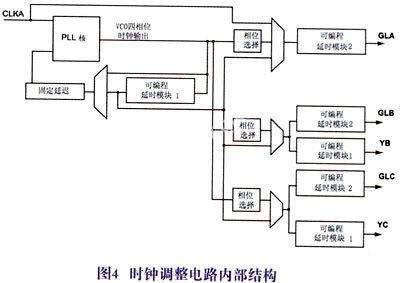

ProASIC3最多可以提供6個模擬的鎖相環PLL,每個PLL位于CCC(時鐘調整電路)中,其輸入頻率為1.5~350MHz,輸出頻率為0.75N350MHz,具有6個可編程的延時模塊,3個相位選擇和最多3個不同頻率信號輸出,如圖4所示。

ProASIC3內部最多具有504kbit的SRAM,可以實現真正的雙端口RAM(2個端口可以同時進行讀寫)和2個端口的RAM,同時這些RAM塊帶有FIFO控制器,可以實現先進先出隊列的FIFO,RAM和FIFO速度可達350MHz。

ProASIC3內部具有1kbit的Flash ROM可供用戶使用,類似于普通的ROM操作,通過上位機軟件將數據固化在FPGA內部的FROM,FPGA在運行的過程中只能進行讀操作,可以用于存放密鑰、序列號、版本號等信息。

ProASIC3還具有超強的加密功能,內部不僅具有128位Flash Lock的加密,而且還有128位的AES加密。FlashLock主要對芯片進行加密,而AES是對編程文件進行加密,ProASIC3內部具有AES的解密引擎,用于對AES加密的文件進行解密。(待續)