基于SIP 技術的固態硬盤電路設計

楊楚瑋,張梅娟,沈 慶

(中國電子科技集團公司第五十八研究所,江蘇 無錫 214035)

0 引言

隨著固態硬盤(Solid State Disk,SSD)小型化、高性能、高穩定性的要求越來越高,在確保安全穩定的前提下,提高集成度有利于存儲系統體積的縮小和功耗的降低。然而,傳統SSD 設計采用分離式設計方式,在PCB板級上多個芯片進行組合,各類元器件使得PCB 板卡面積龐大,且存在較嚴重的功耗和散熱問題[1-3]。

SiP 技術可將SSD 控制單元、NAND 顆粒、電源管理等器件集成在一顆芯片上,達到降低存儲系統體積的目的[4-6]。芯片間走線長度的減少能夠降低高速讀寫信號的傳輸延遲和寄生效應[7],提高存儲系統的傳輸性能及穩定性[8]。在產品應用方面,由于各類芯片管腳數和占用面積的降低,大幅降低了硬件設計的難度和風險。

針對傳統SSD 分離式設計方式需要改善的問題,本文通過SiP 封裝技術將SSD 控制單元、NAND 顆粒、SPI Flash 顆粒、電源管理等關鍵元器件集成在同一顆芯片內部的方式,實現和優化了存儲系統。通過系統驗證保證了設計的可靠性和正確性[9]。同時,通過SiP 存儲系統和分離式存儲系統的對比實現,獲取了SiP 存儲系統的相對小型化和性能優勢。

1 系統總體設計

1.1 電路功能概述

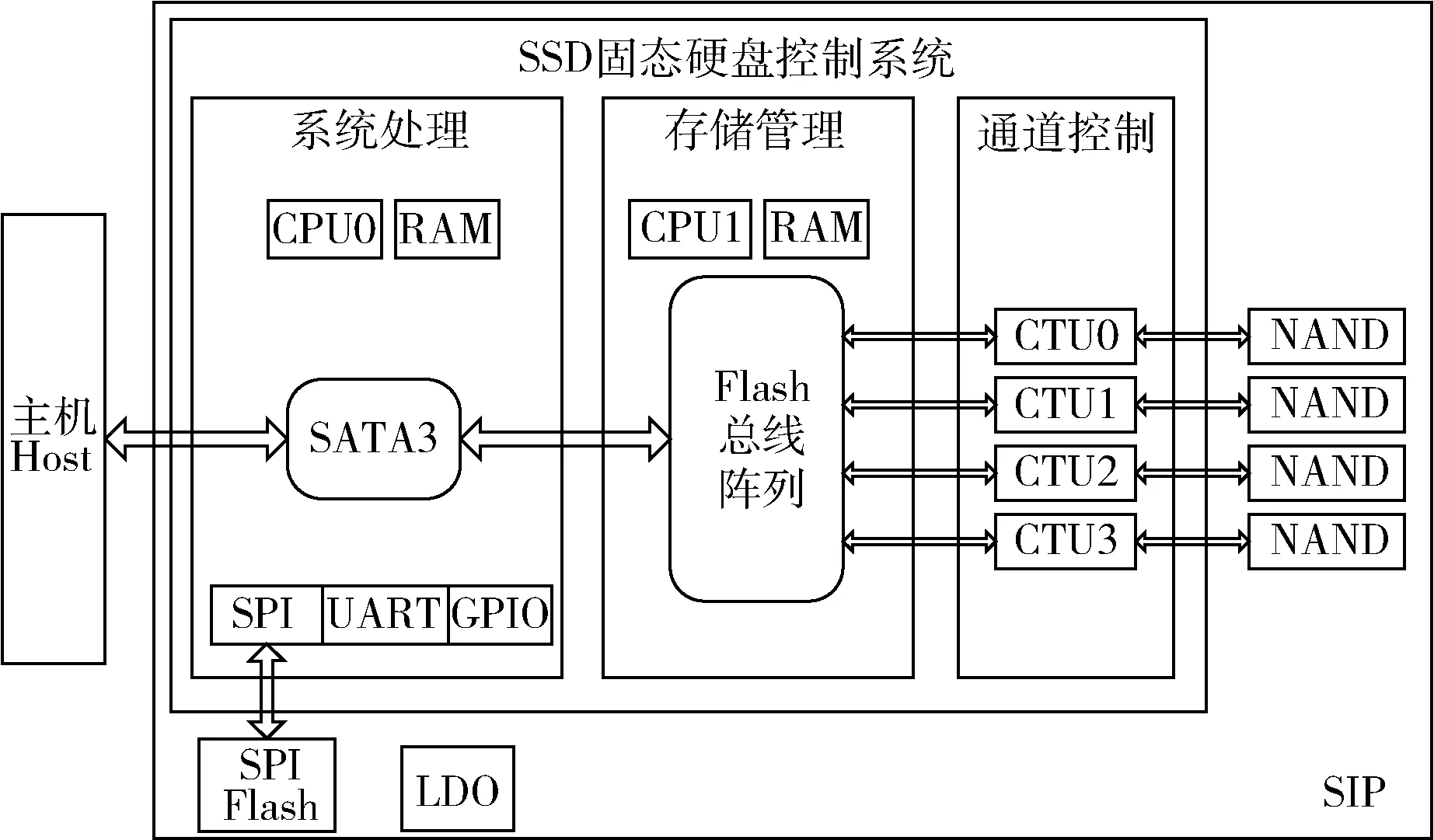

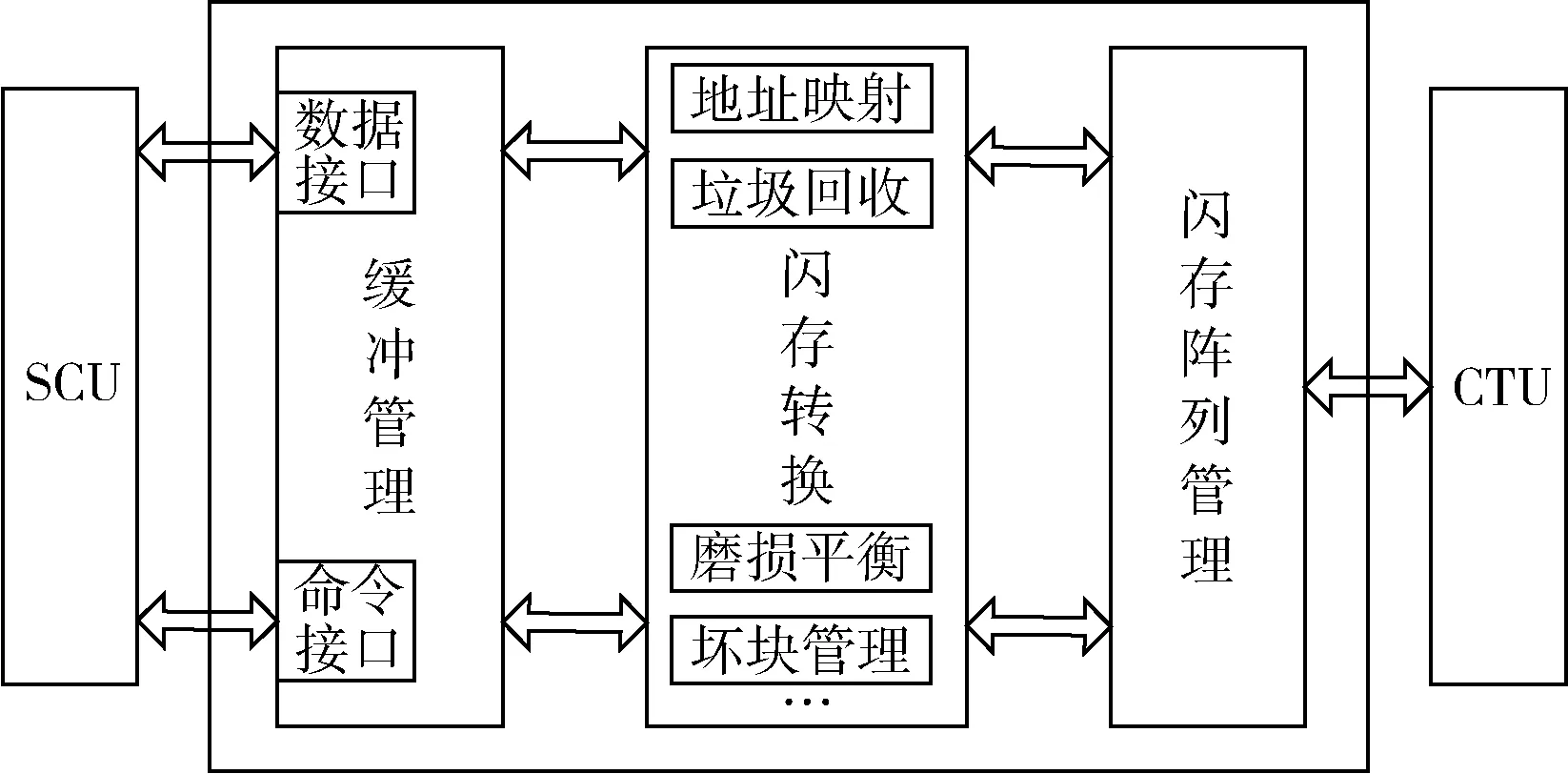

SiP 封裝的固態硬盤電路功能框圖如圖1 所示。該SSD 控制系統的核心由系統控制單元SCU(System Control Unit)、系統存儲單元SSU(System Storage Unit)、通道傳輸單元CTU(Channel Control Unit)三部分組成,其中SCU 負責系統啟動和外設交互,SSU 負責固件算法運行和邏輯存儲管理,CTU 負責執行SSU 對NAND 顆粒的物理操作。

圖1 電路功能框圖

其他主要外設接口包括:SATA 接口集成在SCU 內部,與外部主機Host 的SATA 接口進行交互;NAND 顆粒通過CTU 與SSD 控制模塊相連,用于數據存儲;外部SPI Flash 顆粒通過SPI 接口與SCU 相連,用于固件的存儲。

1.2 系統控制單元

系統控制單元采用Cortex-M3 處理器作為主控,內部包括32 KB 的ROM 空間用于存儲啟動程序,1 MB的SRAM 空間用于運行SCU 固件處理程序及數據緩存。另外包含JTAG、SATA、SPI、UART、GPIO 等外設。

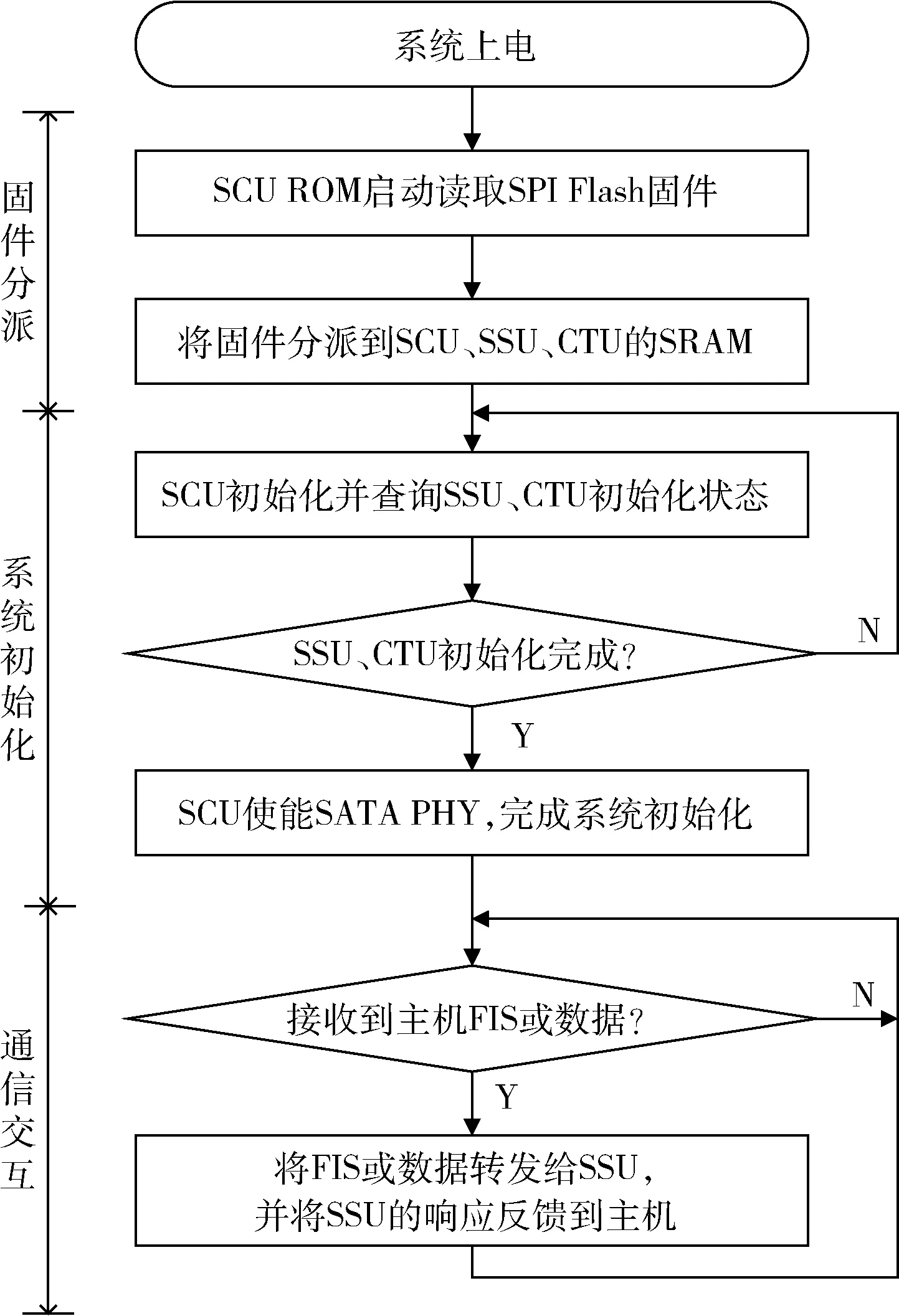

SCU 作為系統主控的基石,主要有固件分派、系統初始化、通信交互等功能。其中,固件分派是指系統上電后,SCU 的ROM Code 運行,通過SPI 接口加載SPI Flash 中的固件程序,并將固件程序進行分包派發到SCU、SSU、CTU 的SRAM 中;系統初始化指SCU 需要對SATA 接口以及其他外設進行初始化,并根據SSU、CTU 初始化完成情況決定整個系統初始化完成情況;通信交互指SCU 通過SATA 接口與主機進行各類幀信息結構FIS(Frame Information Structure)和數據的交互,并通過命令傳輸通道及DMA 數據傳輸通道與SSU 進行命令和數據傳輸。SCU 的工作流程如圖2所示。

圖2 SCU 工作流程圖

1.3 系統存儲單元

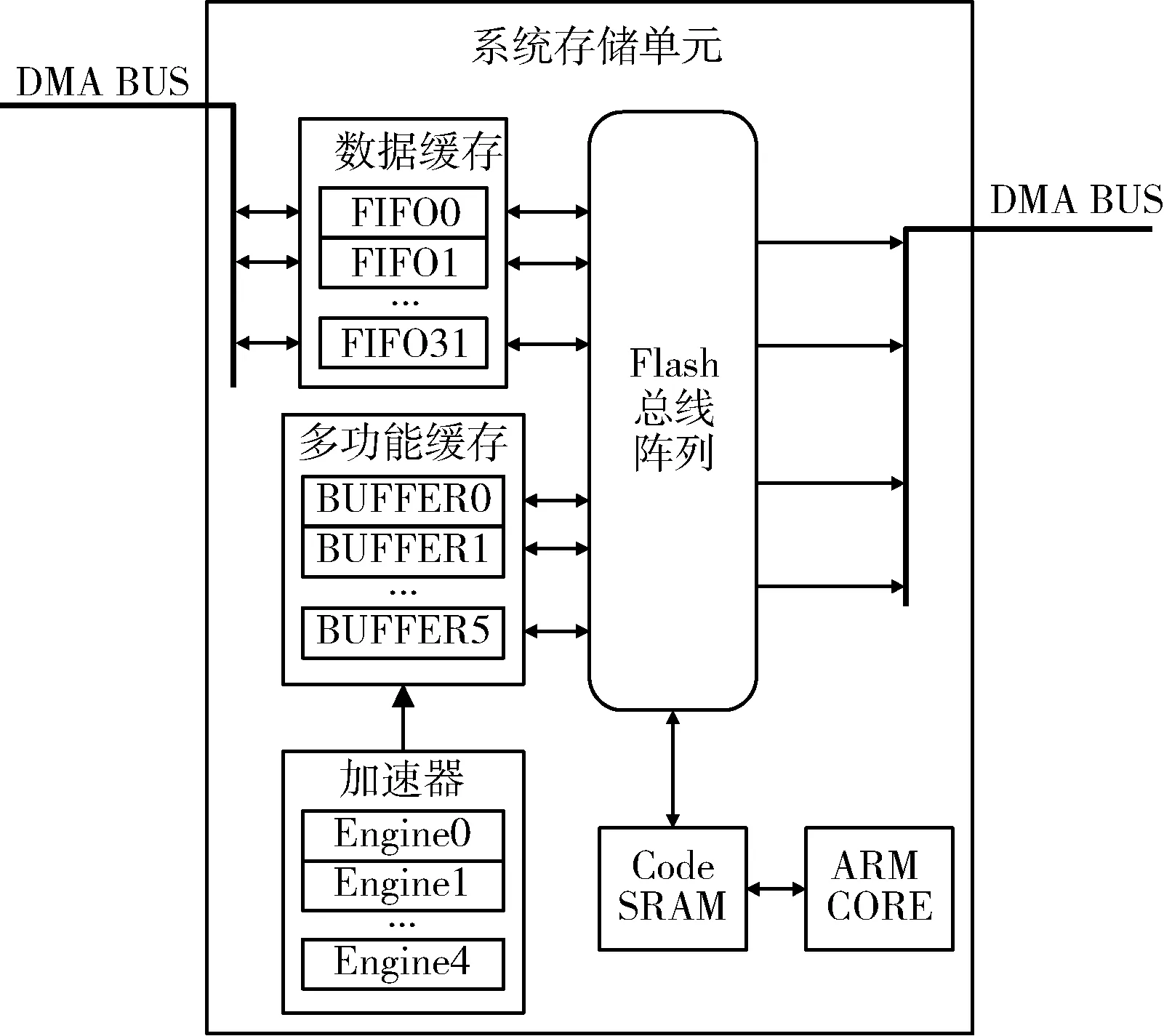

系統存儲單元采用Cortex-M3 處理器作為主控,內部SRAM 由兩部分組成,64 KB 的Code SRAM 空間用于運行SSU 固件處理程序;2 MB 的Data SRAM 空間劃分成32 個16 KB 的FIFO 及6 個256 KB 的BUFFER,其中FIFO 用于緩存SCU 或者CTU 的命令及數據包,BUFFER 則用于NAND 映射表和壞塊表的緩存。除此之外,SSU 內部還有5 個硬件加速引擎模塊,用于龐大的映射表查找以及緩存復制,加速SSD 控制模塊對命令的響應。SSU 內部硬件模塊如圖3 所示。

圖3 SSU 內部硬件模塊圖

SSU 作為管理存儲的核心部件,和存儲傳輸層FTL(Flash Translation Layer)算法一起[10],對SSD 的存儲性能、數據可靠性、使用壽命等方面具有決定性意義。SSU 的主要功能包括:處理與SCU 交互的命令和數據;處理與CTU 交互的NAND 操作命令;管理映射表、壞塊表,實現FTL 算法,完成邏輯地址到物理地址的映射[11]。SSU 功能及與各控制單元的交互如圖4所示。

圖4 SSU 功能框圖

1.4 通道傳輸單元

通道傳輸單元采用8-bit 的單片機PIC16 系列作為主控,內部包括:AES、SM4 硬件加密模塊,對存取數據進行硬件加解密操作;擾碼解碼器,對存取數據進行硬件擾碼解碼操作;ECC 數據校驗模塊,對壞塊或異常造成的少量數據異常進行糾錯,糾錯能力達到72 bit/KB。

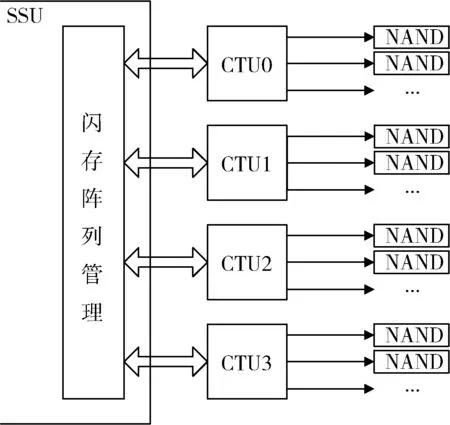

本SiP 電路共集成4 個CTU 模塊,每個CTU 模塊包含8 個CS 片選信號,最多可接32 個NAND 裸片,這種陣列式管理方式,為SSD 的高速度和大容量存儲提供了可能。多CTU 模塊同時對NAND 進行訪問,通過提高數據訪問的并行程度,達到加速訪問的目的。通過多片選,CTU 采用流水線方式對裸片進行管理,不同時刻對不同裸片進行訪問,提高了總線的利用效率,對SSD 的容量擴展和讀寫速率均大有裨益。CTU 陣列式管理如圖5 所示。

圖5 CTU 陣列式管理示意圖

2 SiP 電路實現

2.1 電路設計

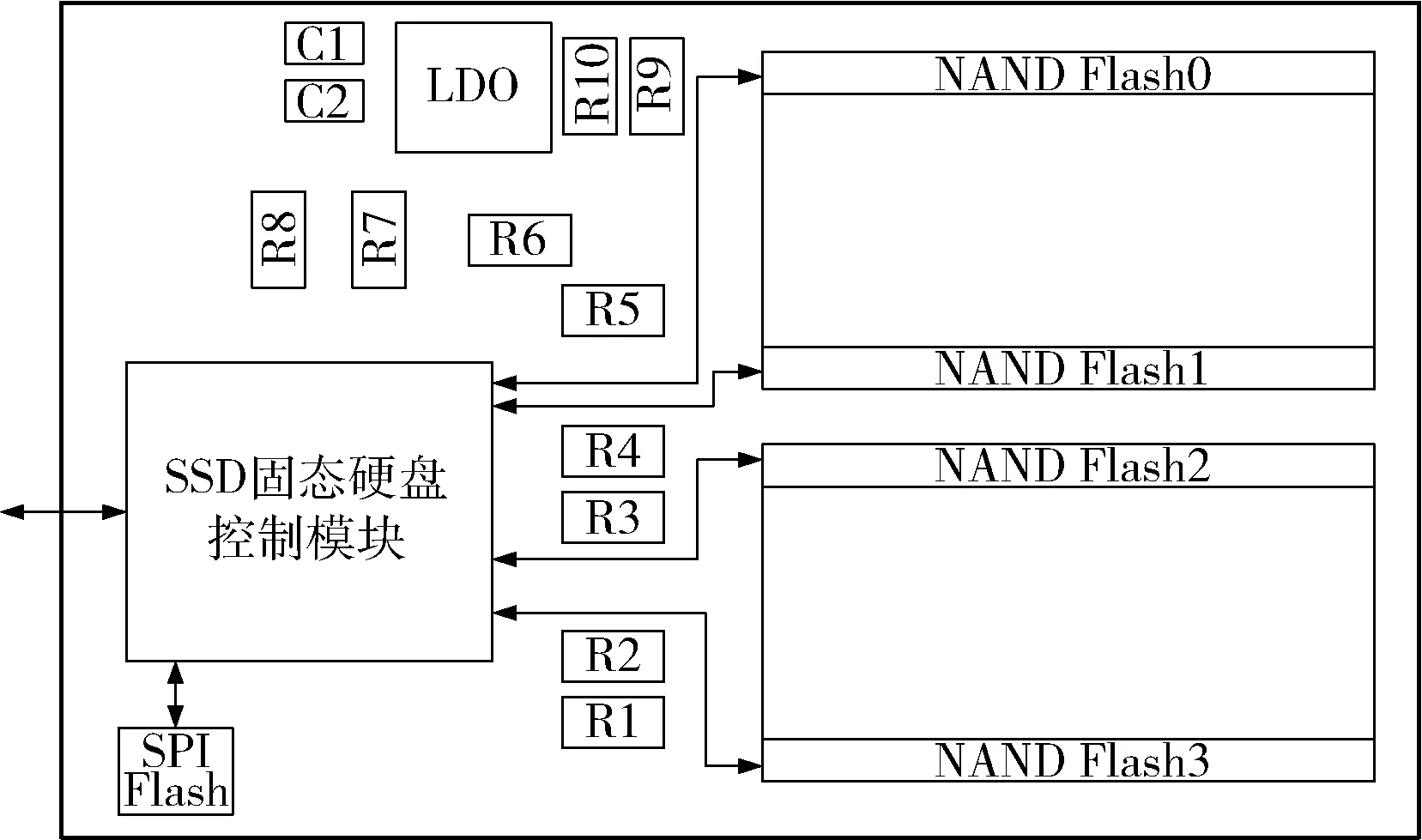

固態硬盤電路通過SiP 封裝將SSD 控制模塊芯片、NAND 顆粒、電源控制芯片LDO、SPI Flash 顆粒、貼片電阻、貼片電容等器件集成在同一電路腔體中,其腔內器件的位置如圖6 所示。

圖6 SiP 系統封裝示意圖

NAND 顆粒作為SSD 主存儲空間,存儲單元架構采用單層單元SLC(Single-Level Cell)模式,相比其他多層單元存儲具備更長的使用壽命,存儲容量為單片8 GB,共使用了4 只裸片,在SiP 腔內采用了兩兩堆疊的結構存放,有效降低了芯片面積[12]。SPI Flash顆粒存儲容量為單片256 KB,其作用在于為控制單元的固件和配置信息提供存儲空間,其位置緊鄰SCU,通過SCU 的SPI 接口進行訪問。電源控制芯片LDO 單元的輸入電壓范圍為1.1 V~5.5 V,輸出電壓范圍為0.8 V~3.6 V,其作用為將3.3 V 轉換為1.8 V給系統供電。

2.2 封裝結構設計

SSD 固態硬盤控制單元采用65 nm 工藝,SiP 電路面積為24.49 mm×14.24 mm。封裝形式BGA145,裝片采用導電膠粘接工藝,鍵合采用銅絲球焊工藝,塑封料模封,標記采用激光打印工藝。本電路的基板布局結構如圖7 所示。

圖7 基板布局圖

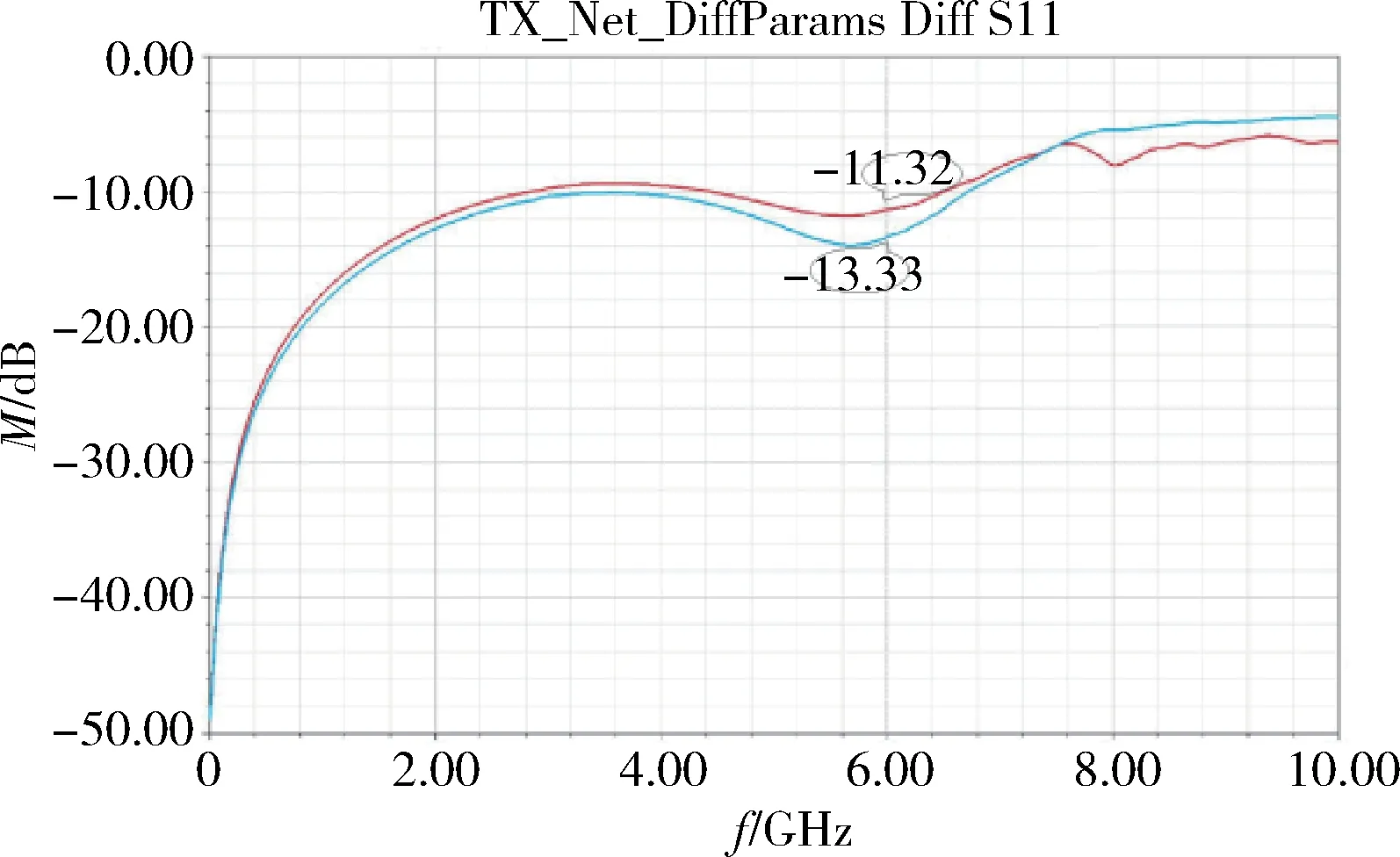

2.3 信號完整性設計與仿真

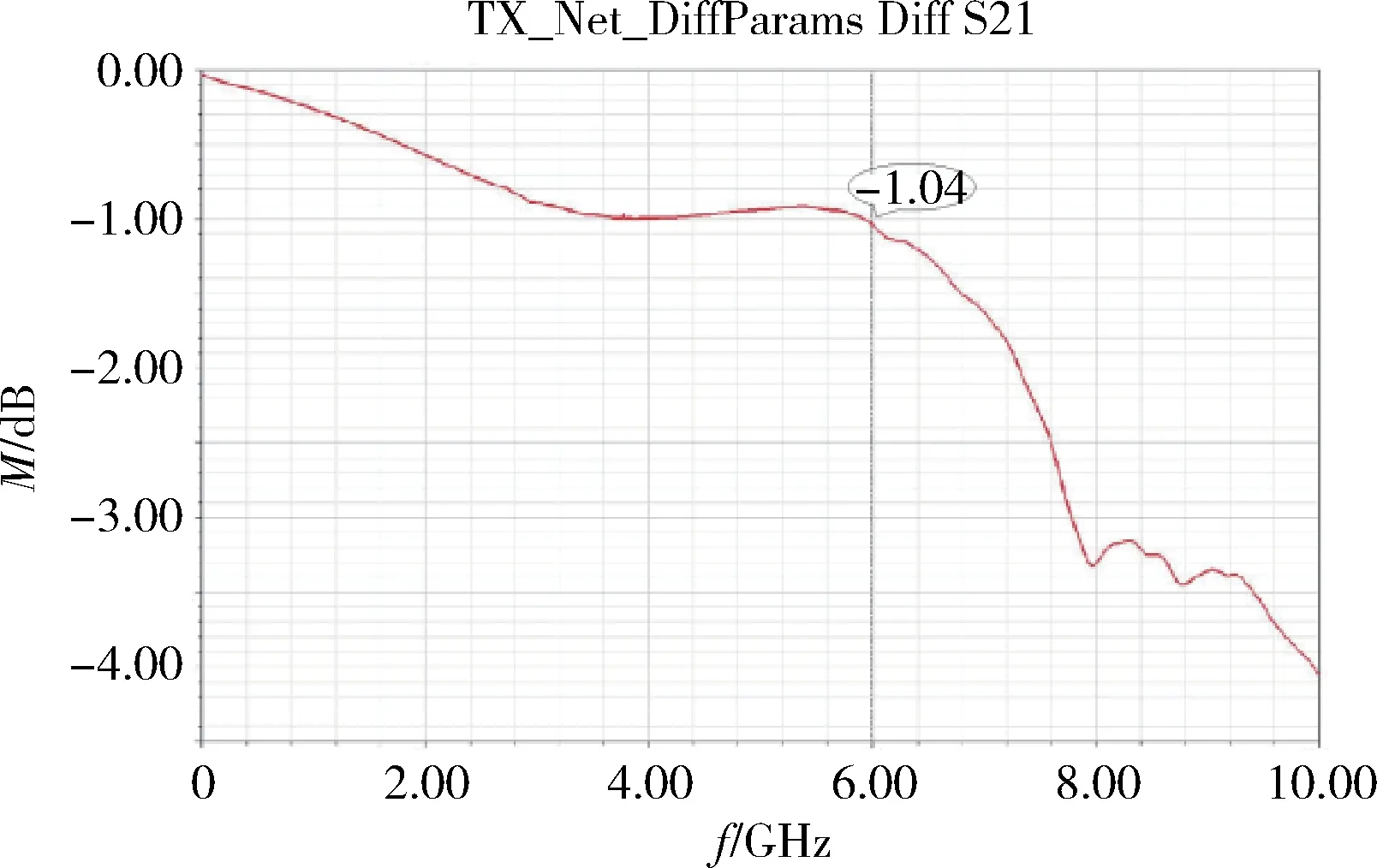

本設計中SATA 接口采用SATA3.0 協議,工作頻率高達6 GHz,差分信號在傳輸線上傳播時,很容易因為阻抗的變化發生信號反射現象。為了消除信號反射,要在兩條信號線末端跨接端接匹配電阻,此處在電路RX 設計時內部帶匹配電阻,并外部留有電阻校準接口。此外,在設計中需要將驅動器間錯位和兩線的不對稱做到最小化,最大程度降低共模干擾導致的差分信號失真。圖8 為SATA TX 信號的插入損耗仿真圖,在6 GHz 工作頻率處插入損耗較小,信號衰減較小。圖9 為SATA TX 差分信號回波損耗仿真圖,在6 GHz 工作頻率處差分信號的回波損耗均保持在較大水平,回波較小。仿真結果顯示TX 信號在工作頻率處傳輸性能較好。

圖8 插入損耗仿真波形圖

圖9 回波損耗仿真波形圖

3 系統驗證

3.1 軟硬件環境

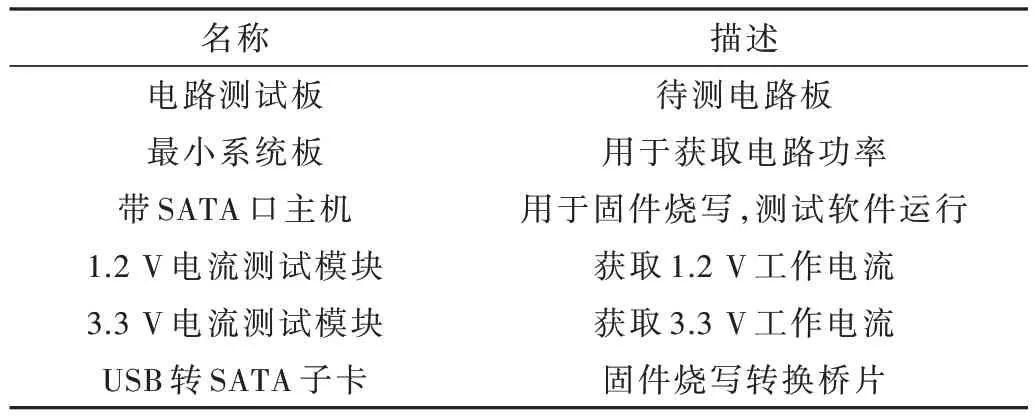

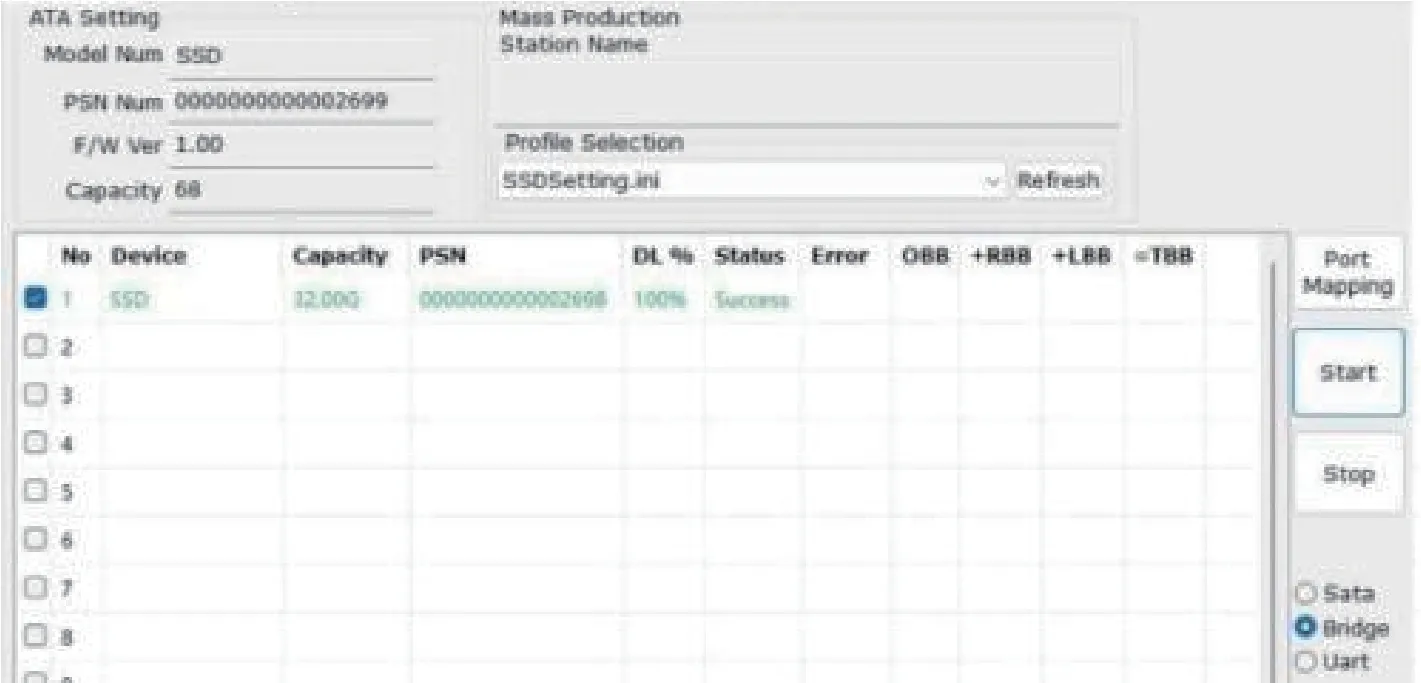

系統驗證的硬件環境包括:電路測試板、最小系統板、帶SATA 口主機、1.2 V 電流測試模塊、3.3 V 電流測試模塊及USB 轉SATA 子卡。詳細功能如表1 所示。硬件環境搭建框圖如圖10 所示。

表1 硬件資源

圖10 硬件環境框圖

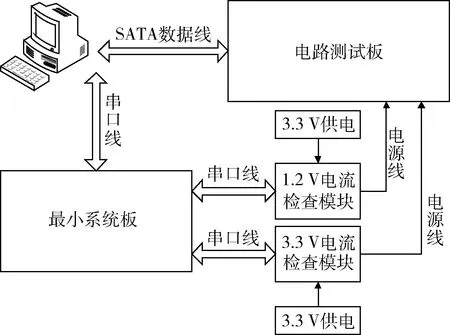

系統驗證的軟件環境包括:控制單元固件燒寫軟件MPTool,如圖11 所示;ATA 基礎命令測試軟件Bus Hound;SSD 性能測試軟件TxBENCH。

圖11 固件燒寫軟件圖

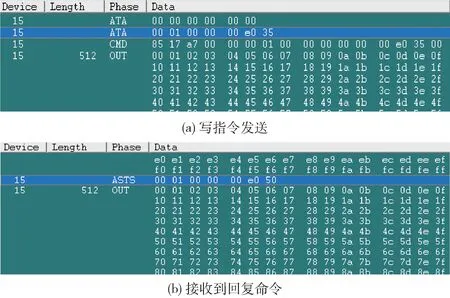

3.2 ATA 命令測試

寫入命令測試:使用Bus Hound 軟件,選擇要檢測的SSD;打開Bus Commander 窗口,選擇ATA 指令;選擇Load,打開待測試文檔(test.db)導入數據;選擇發送WRITE DMA EXT 35 指令,數據長度為512。通過Capture 窗口可確認WRITE DMA EXT 35 寫指令命令發送成功,如圖12(a)所示,并接收到ASTS 回復命令,顯示傳輸OK,如圖12(b)所示。

圖12 數據寫入命令交互截圖

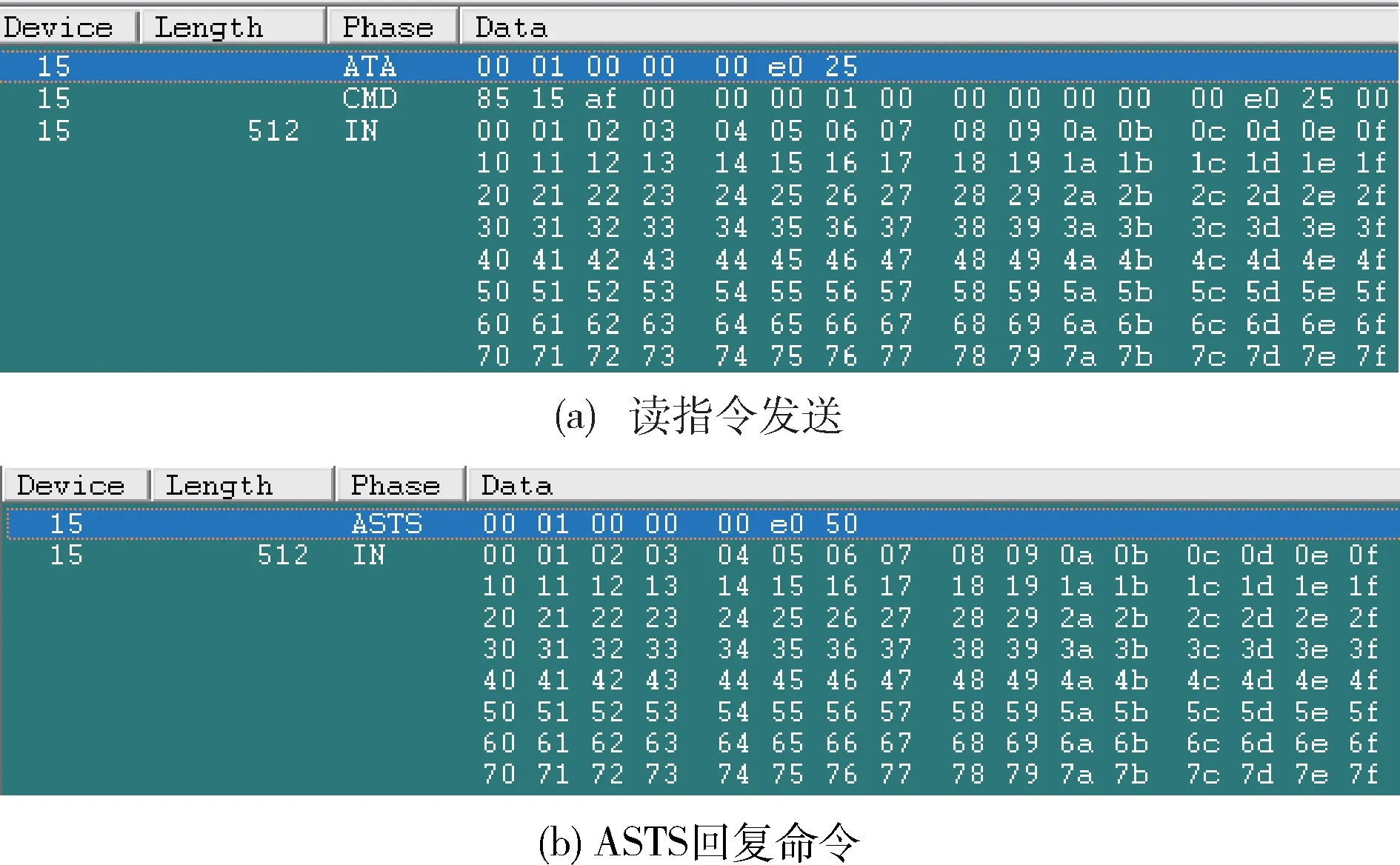

讀取命令測試:打開Bus Commander 窗口,選擇ATA 指令;選擇發送READ DMA EXT 25 指令,數據長度為512。通過Capture 窗口可確認READ DMA EXT 25讀指令命令發送成功,如圖13(a)所示,并接收到ASTS回復命令,顯示傳輸OK,如圖13(b)所示。

圖13 數據讀取命令交互截圖

根據圖12 和圖13 交互命令顯示寫入數據和讀取數據保持一致,ATA 命令對SSD 讀寫功能正常。

3.3 性能測試

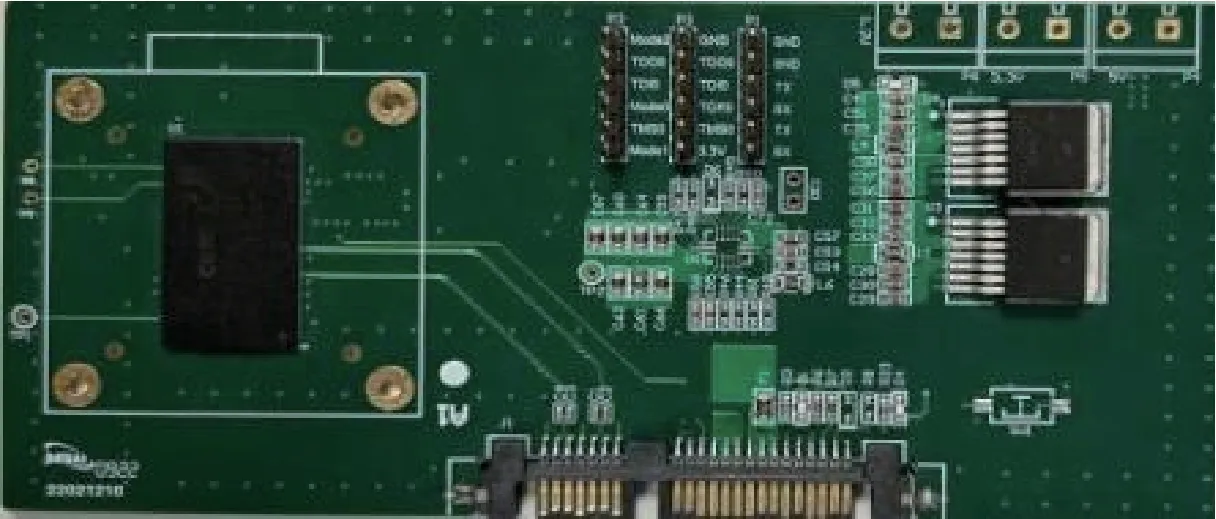

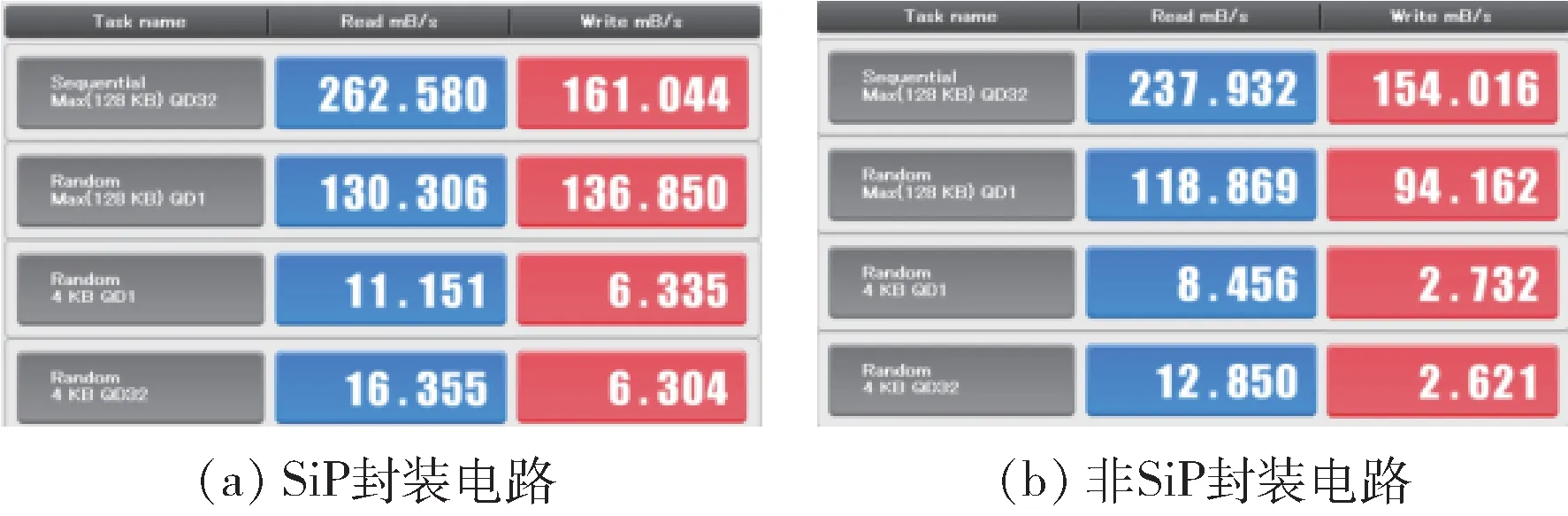

性能測試首先對使用SiP 封裝電路的測試板進行測試,如圖14 所示,然后對使用相同元器件獨立封裝的電路測試板進行測試,如圖15 所示,最后對兩組測試結果進行對比分析。

圖14 SiP 封裝測試板

圖15 非SiP 封裝測試板

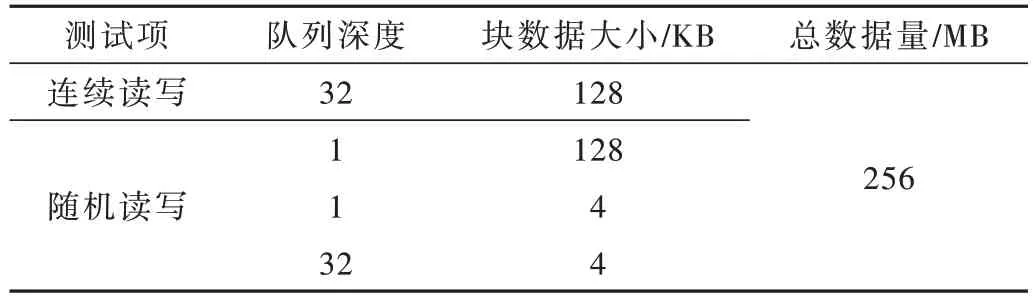

性能測試使用TxBENCH 軟件,進行連續讀寫和隨機讀寫兩種類型的測試[13],總數據塊大小為256 MB。此外,隨機讀寫的數據塊分為最大數據128 KB 和實際使用頻率最高的4 KB 兩種情況;隊列深度參數分為QD1 和QD32 兩種情況,該參數用于反映SSD 在多線程并發環境下的性能。具體測試項如表2 所示。

表2 性能測試項

性能測試結果如圖16 所示,圖16(a)為SiP 封裝電路結果,圖16(b)為非SiP 封裝電路的性能測試結果。結果分析可知SiP 封裝電路比非SiP 封裝電路在4 個測試項上均有不同幅度的提升。連續讀寫性能有一定的提升,但是提升幅度較小。隨機讀寫的性能提升較大,尤其是數據塊大小為4 KB 時的寫數據性能提升一倍多,究其原因,寫操作相對而言速度較慢,且隨機小數據塊寫需要高頻次主機和設備交互,這些特點凸顯了SiP封裝大幅縮短SSD 控制模塊到NAND 顆粒距離的優勢,寫操作速率和穩定性均大幅提升[14-15]。

圖16 性能測試結果

4 結論

隨著SiP 集成技術的日趨成熟和存儲系統小型化、高性能的需求,設計一款基于SiP 封裝的存儲系統電路能夠實現存儲系統各類電路高度集成以及芯片間走線的大幅減少,達到小型化、高性能需求。

本文基于SiP 技術和全國產化器件實現了一種固態硬盤存儲電路的設計。與傳統分離式電路的SSD 產品相比,將SiP 技術應用在國產SSD 上給存儲系統帶來了高性能、低功耗、小型化、高穩定性、高安全性等諸多優勢。通過驗證,證實了SiP 技術應用于存儲系統的可行性,并對SSD 的隨機讀寫性能帶來了大幅提高,為后續SiP 封裝存儲系統的實現提供了設計思路和驗證方法[16]。