基于負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO 設(shè)計(jì)*

朱 琪,黃登華

(中國電子科技集團(tuán)公司第五十八研究所,江蘇 無錫 214072)

0 引言

隨著5G 通信和大數(shù)據(jù)計(jì)算的迅速發(fā)展,大規(guī)模集成電路(如CPU,DSP)工作電流可達(dá)安培級(jí)別[1]。當(dāng)采用LDO 為CPU/DSP 供電時(shí),芯片內(nèi)各個(gè)模塊的通斷將導(dǎo)致LDO 負(fù)載電流發(fā)生突變,從而使LDO 的輸出電壓產(chǎn)生毛刺,最終引起CPU/DSP 整體功能異常,因此如何設(shè)計(jì)具有大電流輸出能力和良好瞬態(tài)性能的LDO 具有重要研究意義[2-4]。

大的電流輸出能力要求LDO 具有較大面積功率管,功率管柵端寄生電容將導(dǎo)致LDO 環(huán)路帶寬減小[5],其與提升瞬態(tài)性能需實(shí)現(xiàn)大帶寬的要求相矛盾。目前,國內(nèi)外研究者提出了在輸出功率管前級(jí)插入電壓緩沖器以提高功率管柵端電壓擺率[6-8]和采用多環(huán)路架構(gòu)[9-10]以降低靜態(tài)功耗等方法來同時(shí)滿足大電流LDO 對(duì)帶載能力和瞬態(tài)響應(yīng)性能的要求,但其存在導(dǎo)致電路效率降低[11]和設(shè)計(jì)結(jié)構(gòu)變復(fù)雜等問題。

為了克服上述問題,本文通過對(duì)LDO 小信號(hào)模型的分析,基于TSMC 0.18 μm BCD 工藝和負(fù)載追蹤補(bǔ)償方式提出了一種大電流LDO 的設(shè)計(jì)技術(shù),其可在最大6 A負(fù)載范圍內(nèi)確保電路具有良好的瞬態(tài)響應(yīng)特性,且所設(shè)計(jì)電路在維持環(huán)路低頻增益不變的情況下可抑制高頻下環(huán)路節(jié)點(diǎn)阻抗從而降低環(huán)路補(bǔ)償難度,最終實(shí)現(xiàn)對(duì)輸出電流能力和瞬態(tài)響應(yīng)性能的良好折中。

1 傳統(tǒng)大電流LDO 架構(gòu)

圖1 所示為傳統(tǒng)大電流LDO 典型架構(gòu)。圖1(a)中增益級(jí)數(shù)較少,單級(jí)增益較大,高增益級(jí)所引入的低頻極點(diǎn)將提升米勒補(bǔ)償?shù)膹?fù)雜度。此時(shí)還需采用大電流BUFFER 對(duì)輸出功率管進(jìn)行驅(qū)動(dòng),電路靜態(tài)功耗較大。圖1(b)中通過提升增益級(jí)數(shù)從而降低單級(jí)增益方式,實(shí)現(xiàn)將環(huán)路中極點(diǎn)挪至帶寬以外的目的,最終確保電路無穩(wěn)定性風(fēng)險(xiǎn),但較多的增益級(jí)將導(dǎo)致電路在失調(diào)和噪聲性能方面的弱化。

圖1 傳統(tǒng)大電流LDO 典型架構(gòu)

2 負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO 小信號(hào)模型

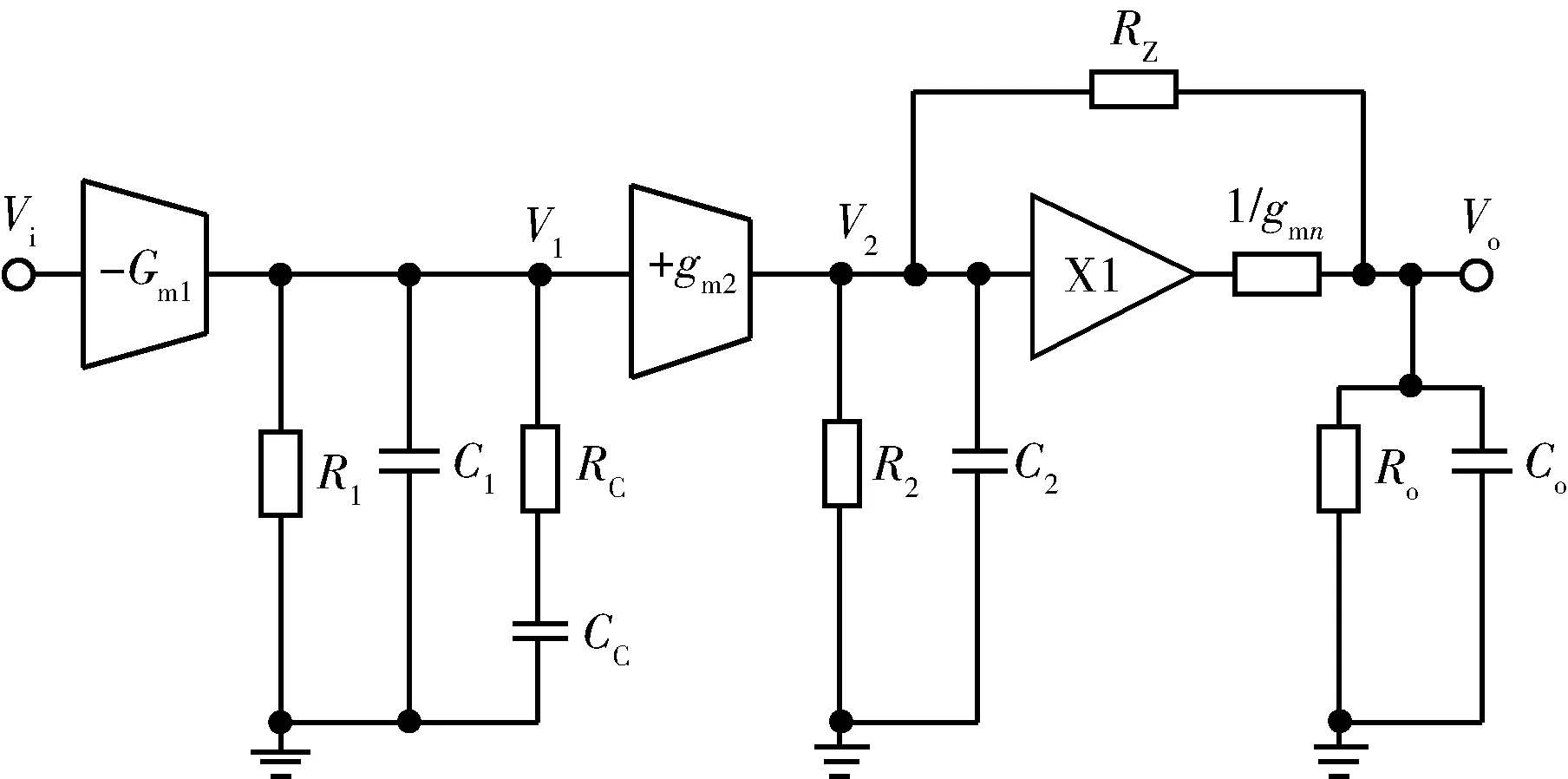

本文所設(shè)計(jì)負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO 小信號(hào)模型如圖2 所示。圖2 中g(shù)m1和gm2代表LDO 中運(yùn)放第一級(jí)和第二級(jí)跨導(dǎo),R1和C1代表運(yùn)放第一增益級(jí)等效輸出電阻和寄生電容,R2和C2代表運(yùn)放第二增益級(jí)等效輸出電阻和寄生電容。本設(shè)計(jì)中輸出功率管由N 型MOS 構(gòu)成,其被等效為單位增益電壓緩沖器X1 和電阻1/gmn串聯(lián)的結(jié)構(gòu)。Ro和Co代表負(fù)載電阻和輸出電容。RC和CC用于實(shí)現(xiàn)運(yùn)放第一增益級(jí)的負(fù)載追蹤補(bǔ)償[12-13],RZ用于實(shí)現(xiàn)運(yùn)放第二增益級(jí)的負(fù)載追蹤補(bǔ)償。

圖2 負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO 小信號(hào)模型

圖2 中LDO 由兩個(gè)高增益級(jí)和一個(gè)電壓緩沖器組成,可輕易實(shí)現(xiàn)高環(huán)路增益以滿足穩(wěn)態(tài)時(shí)對(duì)電路輸出精度的要求。如未采取負(fù)載追蹤補(bǔ)償則環(huán)路中在V1處將存在低頻極點(diǎn)1/R1C1,在V2處將存在低頻極點(diǎn)1/R2C2,這兩個(gè)低頻極點(diǎn)將影響高頻下電路穩(wěn)定性。本文將分別從定性和定量角度出發(fā),分析負(fù)載追蹤補(bǔ)償如何在不影響環(huán)路低頻阻抗從而維持環(huán)路低頻增益不變的同時(shí),對(duì)環(huán)路高頻阻抗進(jìn)行抑制從而將V1和V2處極點(diǎn)推向高頻,最終電路在保持穩(wěn)態(tài)輸出精度的同時(shí)具有良好的瞬態(tài)性能。

從定性角度出發(fā),節(jié)點(diǎn)V1處負(fù)載追蹤補(bǔ)償由電阻RC和電容CC的串聯(lián)網(wǎng)絡(luò)實(shí)現(xiàn),隨著工作頻率的升高,RC和CC的等效串聯(lián)阻抗開始降低,在高頻段V1處等效對(duì)地阻抗為R1//RC。由于RC被設(shè)置為遠(yuǎn)小于R1,高頻段V1處等效對(duì)地阻抗約為RC,此時(shí)V1處極點(diǎn)由低頻1/R1C1被推向高頻1/RCC1處,因此RC和CC在不改變運(yùn)放第一級(jí)增益為gm1R1的前提下實(shí)現(xiàn)了提升高頻段V1處極點(diǎn)頻率的目的。節(jié)點(diǎn)V2處負(fù)載追蹤補(bǔ)償由前饋電阻RZ實(shí)現(xiàn),在低頻段X1 增益為1,流過RZ電流為零,因此低頻時(shí)第二級(jí)增益可保持為gm2R2。隨著工作頻率上升,受輸出端極點(diǎn)影響X1 增益開始下降,RZ兩端壓差不再為零,高頻時(shí)V2處節(jié)點(diǎn)阻抗為R2//RZ≈RZ,此時(shí)V2處極點(diǎn)由低頻1/R2C2被推向高頻1/RZC2處,因此RZ在不改變運(yùn)放第二級(jí)增益的前提下實(shí)現(xiàn)了提升高頻段V2處極點(diǎn)頻率的目的。此外RC和RZ均被設(shè)計(jì)為與輸出負(fù)載相關(guān)的可變電阻,以減小負(fù)載變化對(duì)環(huán)路帶寬和相位裕度的影響。

為定量分析圖2 中電路補(bǔ)償效果,式(1)~式(4)首先給出電路整體傳輸函數(shù)及各節(jié)點(diǎn)零極點(diǎn)分布表達(dá)式。

電路整體傳輸函數(shù):

V1處零極點(diǎn)分布:

V2處零極點(diǎn)分布:

VO處零極點(diǎn)分布:

從式(2)及式(3)可知,V1和V2處均包含一個(gè)低頻零極點(diǎn)對(duì)和一個(gè)高頻極點(diǎn),因此環(huán)路帶寬由高頻極點(diǎn)p1_hf和p2_hf決定,不再受低頻極點(diǎn)p1和p2限制。

圖3 所示為理想情況下,圖2 中電路經(jīng)補(bǔ)償后各增益級(jí)傳輸曲線特性。經(jīng)補(bǔ)償后中頻段V1和V2處存在低阻區(qū)域,且由于零點(diǎn)z1和z2的存在寄生的高頻極點(diǎn)被推至環(huán)路帶寬以外,最終相位裕度由輸出極點(diǎn)po、p1_hf和p2_hf決定。

圖3 理想情況下LDO 各增益級(jí)傳輸特性

3 負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO 電路實(shí)現(xiàn)

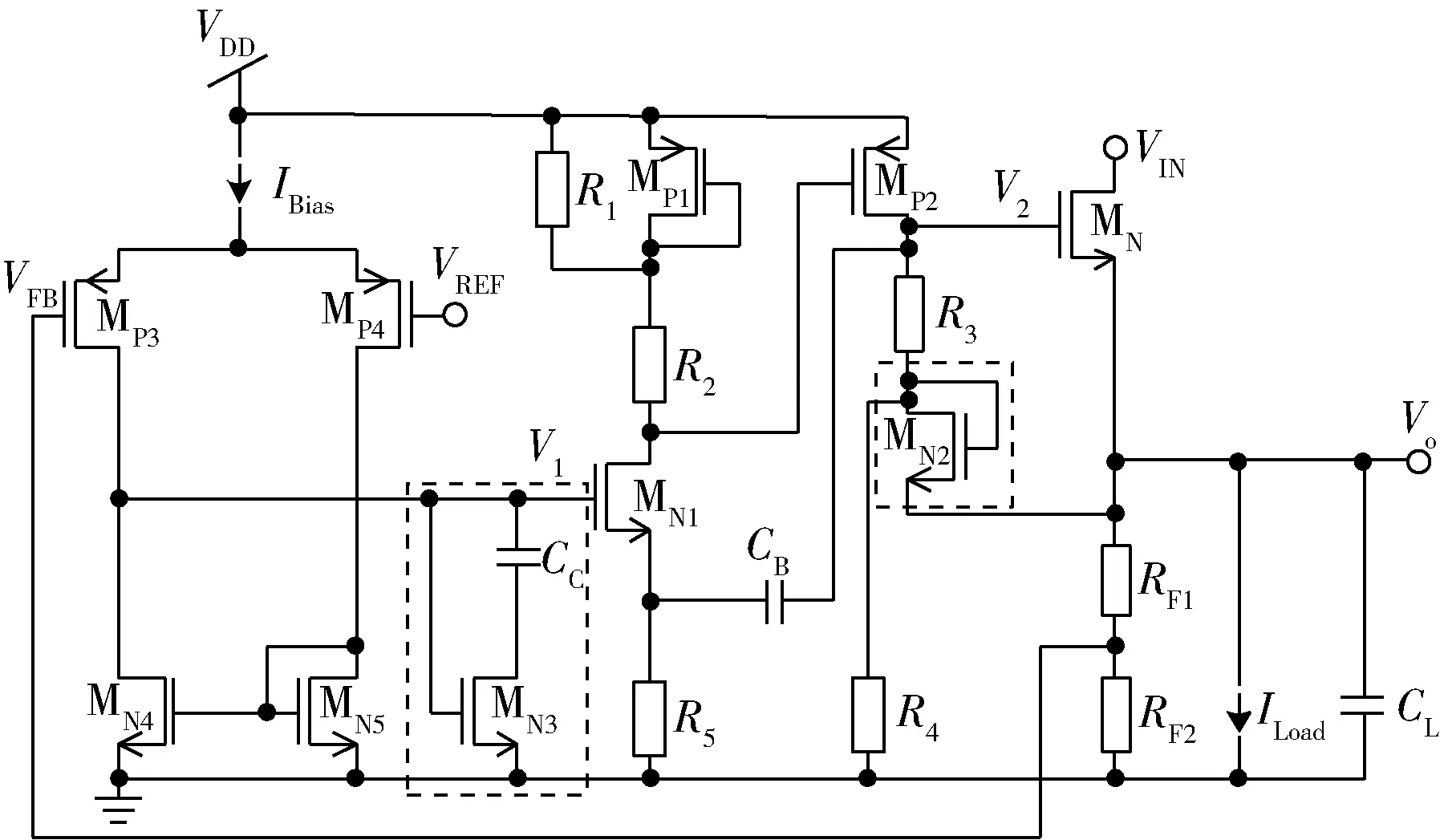

圖4 為本文所提出基于負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO具體電路實(shí)現(xiàn),其第一增益級(jí)為5 管運(yùn)放,第二增益級(jí)為電流鏡型運(yùn)放,輸出功率級(jí)為N 型MOS 管。電阻R2和R3用于降低電路靜態(tài)功耗。電阻R1和R4用于平衡空載時(shí)電路中各節(jié)點(diǎn)靜態(tài)工作點(diǎn)。電容CB在MP2漏端與柵端之間引入一條高頻負(fù)反饋支路,用于提升電路在高頻段的PSRR。圖4 中虛線框內(nèi)器件為負(fù)載追蹤補(bǔ)償網(wǎng)絡(luò)具體實(shí)現(xiàn),MN3代表可變電阻RC,MN2代表可變電阻RZ,負(fù)載電流信息由電流鏡MN2-MN和MP1-MP2進(jìn)行采樣,流過MN1和MN2的電流與負(fù)載相關(guān),合理設(shè)置MN3和MN2尺寸即可獲得所需可變電阻RC和RZ。本設(shè)計(jì)中用于補(bǔ)償?shù)呢?fù)載追蹤可變電阻由電流鏡鏡像方式獲得,電路魯棒性較強(qiáng),受工藝參數(shù)變動(dòng)影響較小,此外MN2中電流最終流向負(fù)載,因此該補(bǔ)償方式不會(huì)導(dǎo)致電路功耗增加。

圖4 負(fù)載追蹤補(bǔ)償?shù)拇箅娏鱈DO 結(jié)構(gòu)

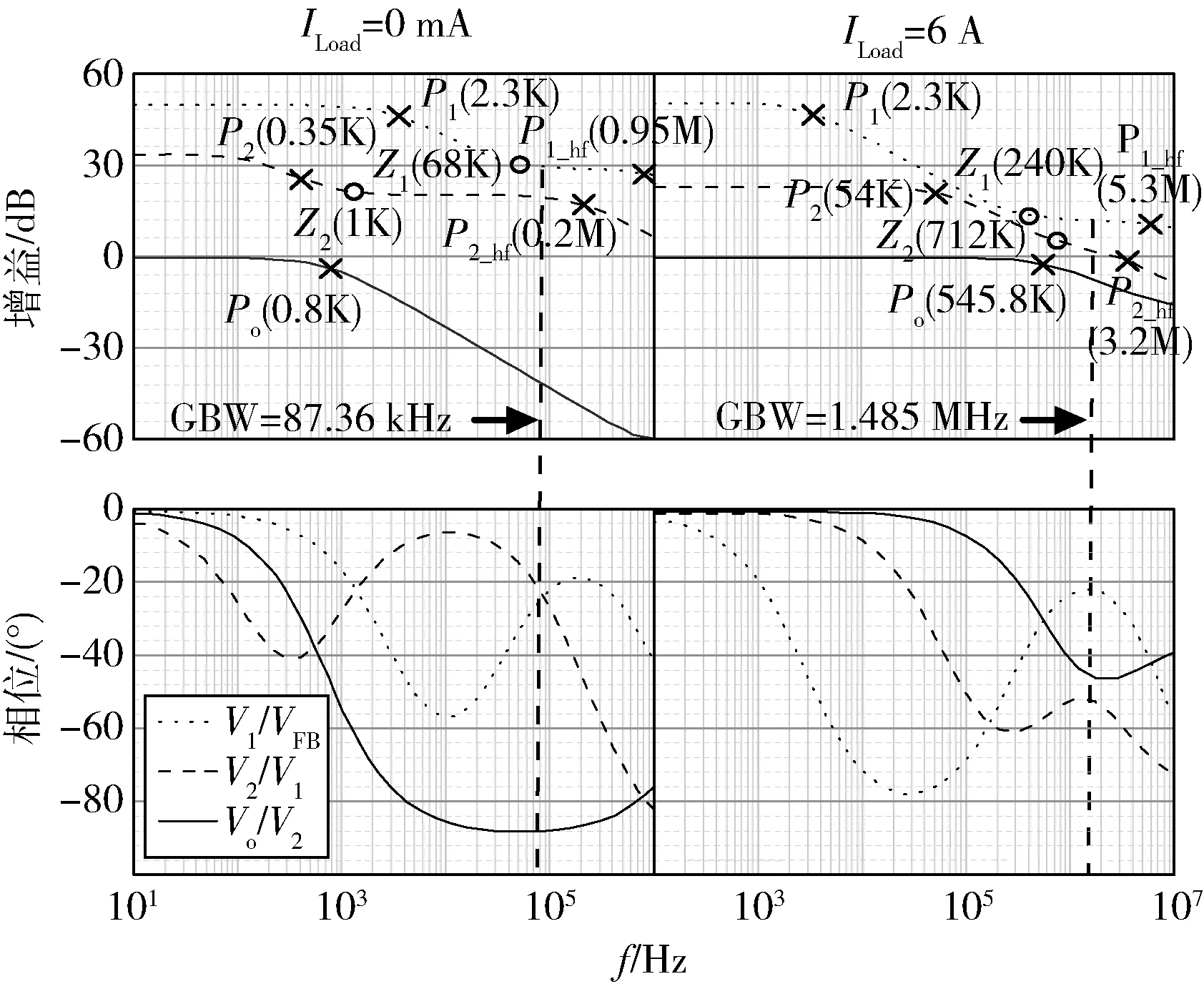

圖5 為輕重載下LDO 各增益級(jí)頻率響應(yīng)曲線及其零極點(diǎn)分布仿真結(jié)果。隨著負(fù)載電流的增大,輸出極點(diǎn)po向高頻移動(dòng),同時(shí)用于環(huán)路補(bǔ)償跟隨負(fù)載變化的零點(diǎn)z1和z2也相應(yīng)向高頻移動(dòng),從而達(dá)到提升帶寬目的且避免了po變化對(duì)環(huán)路相位裕度的影響。

圖5 輕重載下LDO 各增益級(jí)零極點(diǎn)分布

4 仿真與結(jié)果分析

基于TSMC 0.18 μm BCD 工藝,對(duì)本文所設(shè)計(jì)LDO進(jìn)行了仿真驗(yàn)證,給出了整體環(huán)路AC 特性曲線、負(fù)載調(diào)整率、線性調(diào)整率、電源抑制比和負(fù)載瞬態(tài)響應(yīng)仿真結(jié)果。

圖6中LDO環(huán)路AC特性仿真結(jié)果表明,負(fù)載為2.2 mA時(shí),環(huán)路相位裕度為45°,帶寬為87.37 kHz。當(dāng)負(fù)載增大至6 A 時(shí),環(huán)路相位裕度為59.4°,帶寬為1.48 MHz。LDO 環(huán)路具有較大帶寬,且相位裕度受負(fù)載變化影響較小,電路在全負(fù)載范圍內(nèi)可保持穩(wěn)定。

圖6 LDO 環(huán)路AC 特性曲線

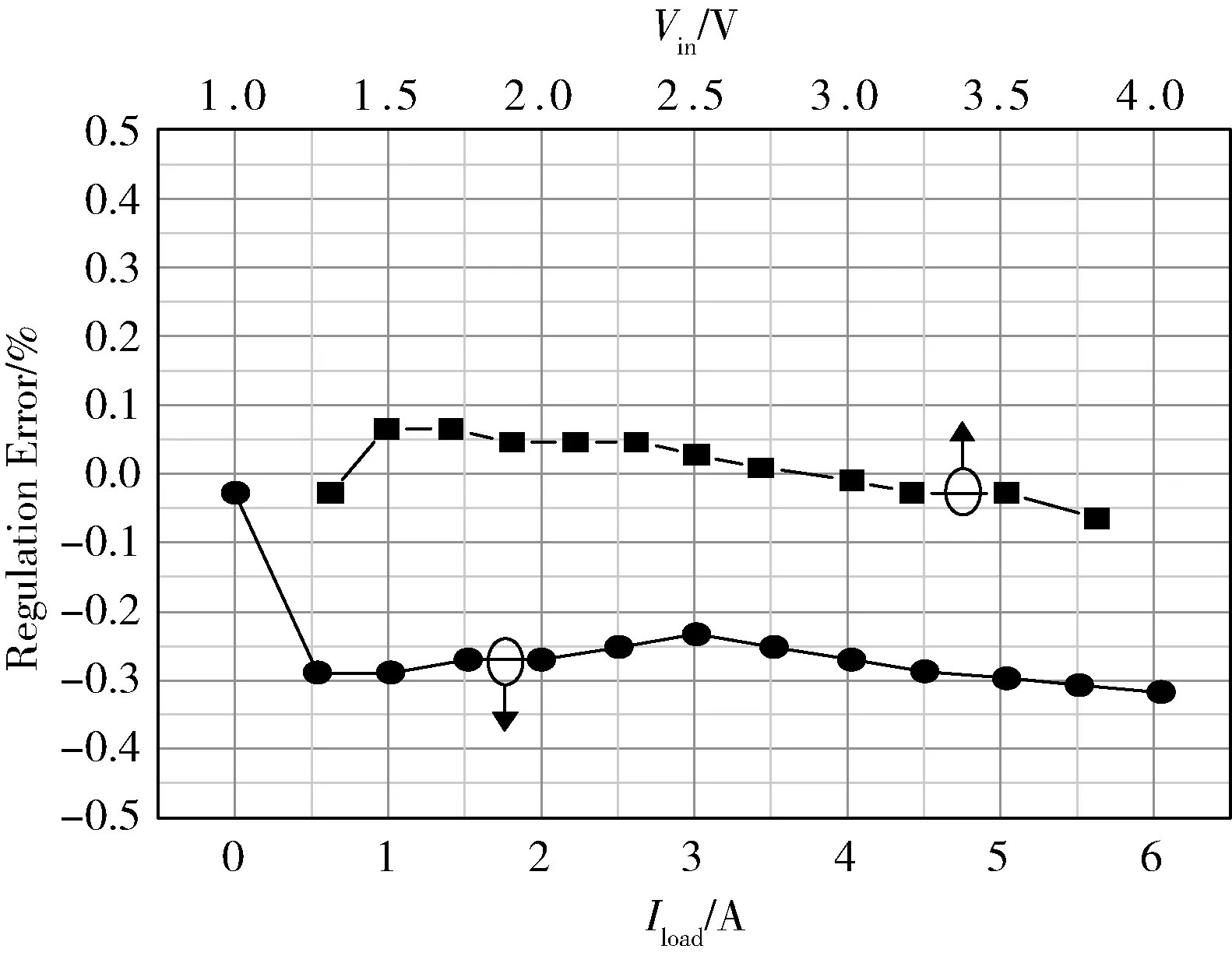

圖7 所示為1 V 輸出條件下,電路負(fù)載調(diào)整率和線性調(diào)整率仿真結(jié)果。受益于本文所提出負(fù)載追蹤補(bǔ)償方式并未降低LDO 環(huán)路低頻增益,因此負(fù)載調(diào)整率小于0.51 mV/A,線性調(diào)整率小于0.25 mV/V,電路穩(wěn)態(tài)精度較高。

圖7 負(fù)載調(diào)整率和線性調(diào)整率曲線

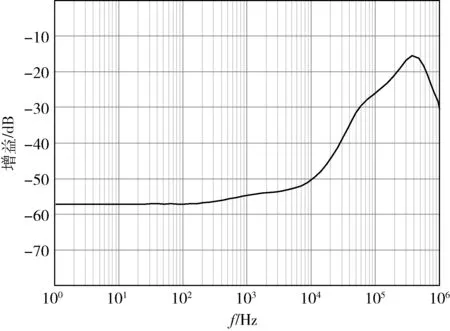

圖8 為電路電源抑制比仿真曲線,可以看出電路對(duì)電源噪聲具有良好的抑制特性。在10 kHz 和1 MHz 頻率時(shí)PSRR 分別為-51 dB 和-30 dB,且由于環(huán)路大帶寬和圖3 中CB所引入高頻負(fù)反饋支路的存在,全頻率范圍下電路PSRR 小于-15 dB。

圖8 電源抑制比曲線

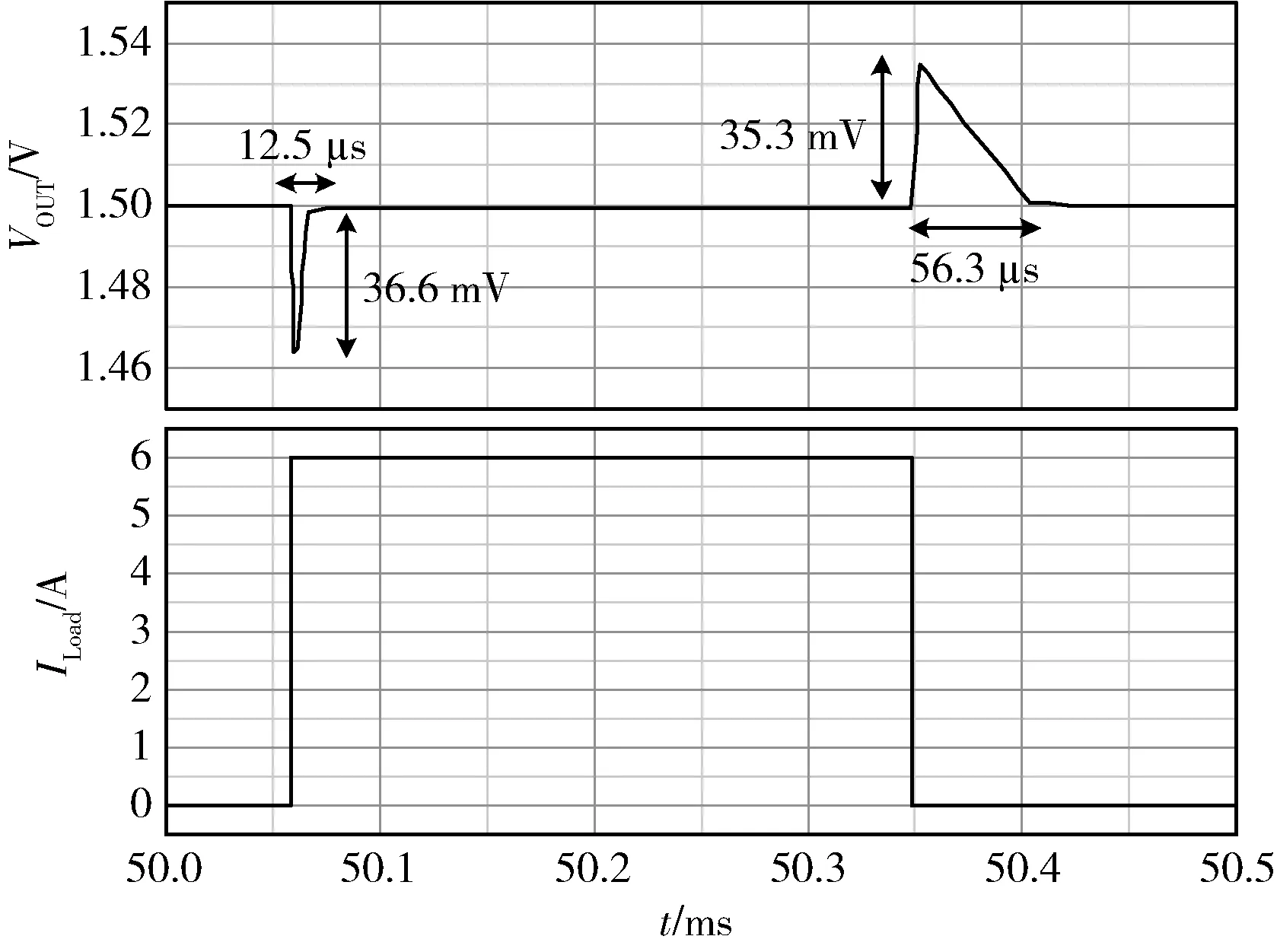

圖9 表明面對(duì)0~6 A,斜率為1 A/μs 的負(fù)載電流突變,輸出電壓下沖為36.6 mV,恢復(fù)時(shí)間為12.5 μs。輸出電壓過沖為35.3 mV,恢復(fù)時(shí)間為56.3 μs。電路瞬態(tài)精度較高,瞬態(tài)誤差小于2.4%。

圖9 LDO 負(fù)載瞬態(tài)響應(yīng)曲線

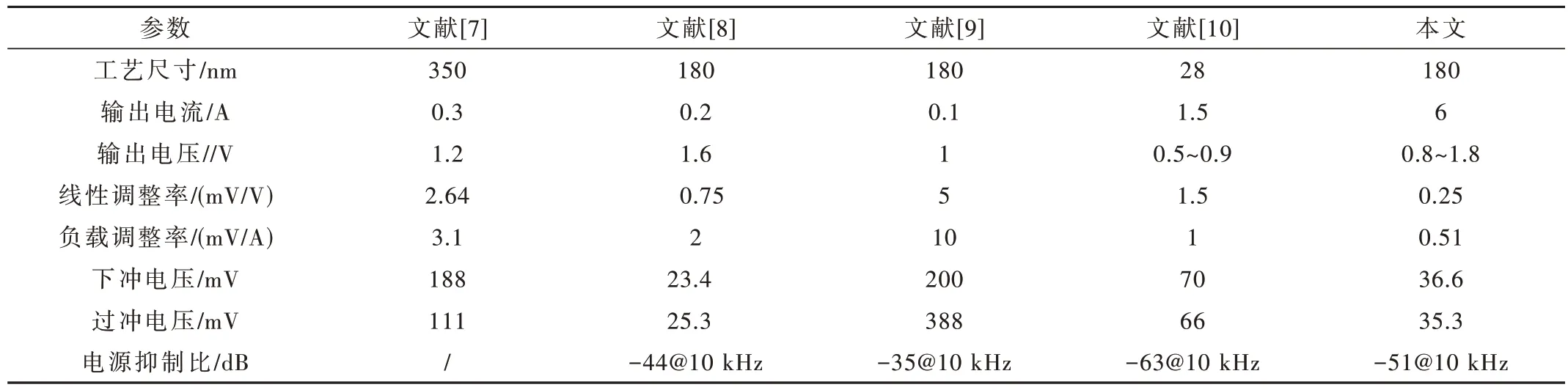

表1 為本文與其他參考文獻(xiàn)中LDO 性能對(duì)比,可知本文所設(shè)計(jì)LDO 綜合性能良好,在最大輸出電流能力、輸出精度和電源抑制比方面均具有顯著優(yōu)勢(shì)。

表1 本文與其他文獻(xiàn)中LDO 性能對(duì)比

5 結(jié)論

本文提出了一種用于大電流LDO 的負(fù)載追蹤補(bǔ)償技術(shù),其采用負(fù)載追蹤補(bǔ)償方式消除了電路輸出端極點(diǎn)隨負(fù)載變化時(shí)對(duì)環(huán)路穩(wěn)定性的影響,實(shí)現(xiàn)了電路面對(duì)大負(fù)載電流突變時(shí)具有良好的瞬態(tài)性能,同時(shí)大的環(huán)路增益提升了電路穩(wěn)態(tài)輸出精度。仿真結(jié)果表明,電路可在6 A 負(fù)載范圍內(nèi)保持輸出穩(wěn)定,瞬態(tài)誤差小于2.4%,負(fù)載調(diào)整率小于0.51 mV/A,線性調(diào)整率小于0.25 mV/V。