基于新型BIST 的LUT 測試方法研究

林曉會(huì),解維坤,宋國棟

(中國電子科技集團(tuán)公司第五十八研究所,江蘇 無錫 214035)

現(xiàn)場可編程門陣列(Field Programmable Gate Array,FPGA)被廣泛應(yīng)用于汽車電子、人工智能、網(wǎng)絡(luò)通信等諸多領(lǐng)域,其復(fù)雜的可編程特性幾乎成為“萬能”芯片[1?3]。由于FPGA 內(nèi)部可編程資源復(fù)雜,僅僅依靠可測性設(shè)計(jì)手段難以實(shí)現(xiàn)100%資源覆蓋測試,因此,還需結(jié)合與應(yīng)用無關(guān)的功能測試保證覆蓋率[4?6]。

查找表(Look Up Table,LUT)作為FPGA 最重要的資源,能夠?qū)崿F(xiàn)極其復(fù)雜的存儲(chǔ)和邏輯功能。針對(duì)LUT的覆蓋率測試,文獻(xiàn)[7]提出了以劃分陣列的方式實(shí)現(xiàn)LUT 測試,需要4 次即可完成100%覆蓋率測試,但劃分和約束過程較為復(fù)雜繁瑣;文獻(xiàn)[8]提出一種基于異或門級(jí)聯(lián)的LUT 測試方法,并通過窮舉LUT 的輸入完成覆蓋率測試,但需要較多配置次數(shù)和復(fù)雜的窮舉輸入。文獻(xiàn)[9?11]巧妙地提出一種基于內(nèi)建自測試(Built?In?Self?Test,BIST)的資源覆蓋測試方法,通過在FPGA 內(nèi)部構(gòu)建BIST 電路實(shí)現(xiàn)被測模塊的覆蓋測試,但未深入研究基于BIST 的LUT 測試方法,且其提出的BIST 測試方案有待進(jìn)一步完善和改進(jìn)。因此,本文重點(diǎn)研究基于BIST 的LUT 測試方法。

1 BIST 的LUT 測試方案

1.1 典型BIST 結(jié)構(gòu)

典型的BIST[12?15]結(jié)構(gòu)由測試圖形生成器(Test Pattern Generation,TPG)、被測模塊(Block Under Test,BUT)和輸出響應(yīng)分析器(Output Response Analyzer,ORA)三部分組成,如圖1 所示。其中:TPG 用于產(chǎn)生測試向量,為BUT 提供測試圖形輸入,如計(jì)數(shù)器、線性移位寄存器等均能提供順序或偽隨機(jī)的測試圖形;ORA用于分析比較BUT 的輸出是否正常,如多輸入移位寄存器、奇偶校驗(yàn)器等。

圖1 典型的BIST 測試結(jié)構(gòu)

1.2 可配置邏輯塊中的查找表

以AMD 公司的Ultrascale+系列FPGA XCKU5 PFFVB676I 為例,每個(gè)可配置邏輯塊(CLB)內(nèi)包含8 個(gè)查找表(LUT),該型號(hào)FPGA 全部資源共含有216 960 個(gè)LUT,每個(gè)LUT 包含6 個(gè)輸入、2 個(gè)輸出的邏輯函數(shù)發(fā)生器,可實(shí)現(xiàn)任意1~6 變量輸入、1~2 輸出的邏輯表達(dá)式。基于FPGA 實(shí)現(xiàn)的眾多功能中,幾乎沒有不涉及使用LUT 模塊的,因此,為保證用戶在使用FPGA 內(nèi)部LUT資源時(shí)的高穩(wěn)定性和高可靠性,針對(duì)FPGA 中LUT 的覆蓋率測試至關(guān)重要。Ultrascale+系列FPGA 內(nèi)部LUT 結(jié)構(gòu)如圖2 所示。

圖2 Ultrascale+系列FPGA內(nèi)部LUT 結(jié)構(gòu)

1.3 新型BIST 結(jié)構(gòu)

本文提出一種新型BIST 結(jié)構(gòu),用于測試FPGA 內(nèi)部的LUT 資源覆蓋率。該結(jié)構(gòu)主要由測試圖形生成器、被測模塊、黃金模塊(Golden Block,GB)、比較模塊(Comparator Block,CB)四個(gè)部分組成,測試結(jié)構(gòu)如圖3所示。其中,黃金模塊與被測模塊同結(jié)構(gòu)、同功能,其測試原理為:通過TPG 產(chǎn)生測試向量,同時(shí)輸出到被測模塊和黃金模塊,利用比較模塊對(duì)比BUT 和GB 的輸出,如果兩者輸出一致,則證明被測模塊功能正常,反之功能異常。

圖3 新型BIST 測試結(jié)構(gòu)

1.4 新型BIST 的LUT 測試方案

新型BIST 的結(jié)構(gòu)在用于LUT 覆蓋率測試時(shí),TPG為改進(jìn)的線性反饋移位寄存器(Linear Feedback Shift Register,LFSR),用于全地址的偽隨機(jī)測試向量生成,作為BUT 和GB 的輸入;BUT 為6 輸入、1 輸出異或功能的LUT,GB 同樣為6 輸入、1 輸出異或功能的LUT;CB 為2 輸入、1 輸出的比較器,用于比較BUT 和CB 的LUT 輸出,如果兩者的異或功能輸出結(jié)果一致,則判定被測的LUT 模塊功能正常,否則功能異常。LUT 測試結(jié)構(gòu)如圖4 所示。

圖4 新型BIST 的LUT 測試結(jié)構(gòu)

在實(shí)際測試時(shí),利用pBlock 功能,將FPGA 內(nèi)部的LUT 資源分為上下兩部分。第一次測試設(shè)計(jì)時(shí),其中一部分用于TPG、GB 和CB 模塊資源的例化,另一部分用于BUT 資源例化;第二次測試設(shè)計(jì)將兩部分位置調(diào)換。這樣,通過兩次測試配置,即可完成所有LUT 的覆蓋測試。經(jīng)pBlock 約束后,一次布局布線后的LUT 測試圖形如圖5 所示。

圖5 布局布線后的LUT 測試圖形

2 測試硬件設(shè)計(jì)

自動(dòng)測試設(shè)備(Automatic Test Equipment,ATE)作為LUT 覆蓋率的測試驗(yàn)證平臺(tái),具備電源供應(yīng)、任意波形發(fā)生、系統(tǒng)時(shí)鐘、精密測量單元(包括加壓測流、加流測壓等)、向量存儲(chǔ)等多種功能,因此無需外接其他測試測量設(shè)備即可完成驗(yàn)證評(píng)價(jià)和量產(chǎn)測試。測試硬件的設(shè)計(jì)主要針對(duì)ATE 的測試負(fù)載板。

XCKU5PFFVB676I 為一款億門級(jí)FPGA,具有豐富的邏輯資源和各類IP 核,支持多種配置方式,包括但不限于Slave SelectMAP、JTAG 等,同時(shí)電源的種類也較多,設(shè)計(jì)時(shí)重點(diǎn)包括測試配置通道和電源供電,如圖6所示為測試負(fù)載板設(shè)計(jì)方案。

圖6 FPGA 測試負(fù)載板設(shè)計(jì)方案

圖中:pogo pin 為ATE 與測試負(fù)載板通信連接的橋梁,為被測FPGA提供輸入信號(hào)和接收輸出信號(hào);power B為被測FPGA 的內(nèi)核電源VCCINT 提供大電流電源,保證FPGA 配置時(shí)的瞬態(tài)脈沖大電流滿足啟動(dòng)要求;power S 為被測FPGA 的其他電源供電。

JTAG 接口主要用于實(shí)裝測試時(shí)的配置比特流下載,通過TDI 一位一位地將比特?cái)?shù)據(jù)加載到FPGA 的配置存儲(chǔ)器中,下載速度較慢。在實(shí)際ATE 量產(chǎn)測試中,通過pogo pin,基于Slave SelectMAP 方式完成測試配置,這種方式將待配置的測試向量先存儲(chǔ)到ATE 的向量存儲(chǔ)模塊,測試時(shí)直接調(diào)用所需的向量名稱即可,可同時(shí)并行下載32 位比特?cái)?shù)據(jù)并加載到FPGA 內(nèi),配置速率大幅提升,適用于大規(guī)模的量產(chǎn)測試需求。

3 仿真與測試驗(yàn)證

3.1 改進(jìn)的LFSR 與仿真

傳統(tǒng)的測試向量發(fā)生器一般用LFSR 實(shí)現(xiàn),產(chǎn)生的向量具備一定的偽隨機(jī)性,但無法遍歷全0 地址。改進(jìn)的LFSR 在原有的基礎(chǔ)上進(jìn)行優(yōu)化,不僅具備偽隨機(jī),而且能夠覆蓋到全0 地址,其結(jié)構(gòu)如圖7 所示。

圖7 改進(jìn)的LFSR 結(jié)構(gòu)

經(jīng)編寫Verilog 代碼,通過Vivado 2018.3 編譯仿真環(huán)境得到改進(jìn)的LFSR 時(shí)序仿真結(jié)果,如圖8 所示。其中:clk 為輸入時(shí)鐘;rst_n 為復(fù)位信號(hào);lfsr_dout 為產(chǎn)生的全地址向量。

圖8 改進(jìn)的LSFR 仿真結(jié)果

3.2 新型BIST 的LUT 測試仿真

在BIST 電路結(jié)構(gòu)中,改進(jìn)的LFSR 產(chǎn)生全地址的偽隨機(jī)測試向量,同時(shí)輸出到被測模塊LUT 和黃金模塊LUT,通過比較兩者輸出否是一致,判斷被測LUT 是否存在故障。其中,LUT 是基于Xilinx 原理實(shí)現(xiàn)6 輸入、1 輸出的異或門。測試仿真結(jié)果如圖9 所示。圖中,error 為輸出判斷結(jié)果,除復(fù)位狀態(tài)時(shí)error 輸出為高電平外,其他狀態(tài)若輸出高電平,則判定被測LUT 存在故障;反之說明被測LUT 功能正常,無故障。

圖9 新型BIST 的LUT 測試仿真結(jié)果

3.3 測試配置與驗(yàn)證

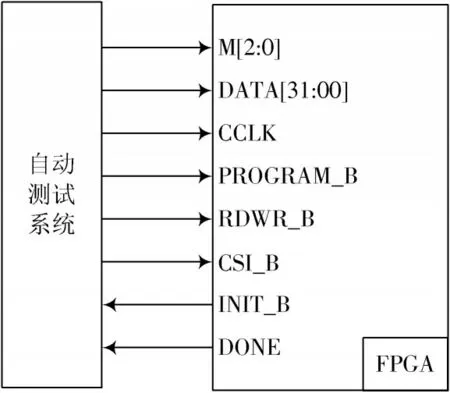

經(jīng)過Vivado 軟件編譯綜合生成比特流,利用Slave SelectMAP 模式,基于ATE 將比特流配置向量下載到FPGA 內(nèi),并施加相應(yīng)的響應(yīng)測試激勵(lì),完成FPGA 內(nèi)LUT 資源覆蓋率測試。配置通信原理如圖10 所示[16]。

圖10 基于Slave SelectMAP 配置原理

圖中:M[2:0]為模式選擇輸入,M[2:0]=3’b110 表示選擇Slave SelectMAP 模式;DATA[31:00]為比特流數(shù)據(jù),配置的比特文件通過該端口下載至FPGA;CCLK 為專用配置時(shí)鐘;PROGRAM_B 為專用配置信號(hào),拉低時(shí)表示清除配置和初始化;RDWR_B 和CSI_B 均為專用配置信號(hào),RDWR_B 拉低表示測試系統(tǒng)向FPGA 寫數(shù)據(jù),CSI_B 拉低表示激活Slave SelectMAP 模式;INIT_B 為配置過程指示信號(hào),當(dāng)PROGRAM_B 拉低清除配置時(shí),INIT_B 輸出為低,配置數(shù)據(jù)開始到結(jié)束,INIT_B 一直輸出為高;DONE 為配置完成指示信號(hào),當(dāng)配置數(shù)據(jù)全部加載完畢,等待幾個(gè)時(shí)鐘周期后,DONE 輸出高即表示配置完成。此時(shí),測試系統(tǒng)與FPGA 完成握手通信,F(xiàn)PGA 被配置成特定功能的ASIC。

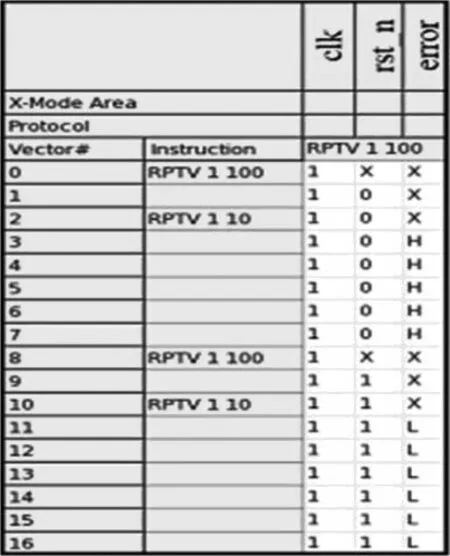

測試系統(tǒng)中,LUT 測試的比特流配置向量和功能向量如圖11 和圖12 所示。圖中,CCLK 和clk 信號(hào)為歸零碼格式,一直發(fā)送時(shí)鐘信號(hào),其他信號(hào)均為非歸零碼格式。比特流配置向量是將FPGA 配置成特定功能,功能向量是完成特定功能驗(yàn)證,測試中rst_n 只有在復(fù)位狀態(tài)時(shí),error 才輸出高電平。如圖13 所示,實(shí)際測試結(jié)果與仿真結(jié)果完全一致。

圖11 比特流配置向量

圖12 功能向量

圖13 基于BIST 的LUT 測試驗(yàn)證結(jié)果

3.4 LUT 的故障注入與診斷

為了進(jìn)一步驗(yàn)證測試方案的準(zhǔn)確性和可靠性,設(shè)計(jì)一種模擬單粒子翻轉(zhuǎn)的故障注入電路[17?18],其結(jié)構(gòu)如圖14 所示。

圖14 LUT 的故障注入電路

圖中的LFSR[5:1]為線性反饋移位寄存器的輸出,F(xiàn)IS 為故障注入使能。故障注入的原理為:通過在LUT的任意輸入,如I0 端口增加一個(gè)故障注入電路,如果使能FIS,則I0 的輸入為LFSR[0]輸出值取反,實(shí)現(xiàn)故障注入;如果不使能FIS,則I0 的輸入即為LFSR[0]正常輸出值。利用這種方式可以有效地控制故障注入的執(zhí)行與否,最后基于BIST 測試電路,驗(yàn)證測試方法的準(zhǔn)確性。

仿真及驗(yàn)證結(jié)果如圖15、圖16 所示。圖中:起始階段rst_n 復(fù)位時(shí),error 輸出高;rst_n 拉高后,生成的偽隨機(jī)測試向量輸出到被測LUT 和黃金模塊的LUT 中。從圖中可以明顯看出,當(dāng)FIS=0 時(shí),被測LUT 未注入故障,功能與黃金模塊功能一致,error 輸出為低;當(dāng)FIS=1 時(shí),被測LUT 故障注入成功,功能與黃金模塊功能不一致,error 輸出為高。同樣,經(jīng)ATE 的測試驗(yàn)證,測試結(jié)果與仿真結(jié)果一致。

圖15 LUT 故障注入及診斷仿真結(jié)果

圖16 LUT 故障注入及診斷驗(yàn)證結(jié)果

綜上所述,從仿真到驗(yàn)證,證明了所設(shè)計(jì)的新型BIST 測試電路對(duì)LUT 功能檢測的實(shí)用性和準(zhǔn)確性。

4 結(jié)論

本文應(yīng)用新型BIST 電路完成了FPGA 內(nèi)部LUT 資源的可測性設(shè)計(jì),通過2 次配置設(shè)計(jì)就能實(shí)現(xiàn)LUT 的100%覆蓋測試,并基于Xilinx 的一款億門級(jí)FPGA 完成了測試驗(yàn)證。結(jié)果表明新型BIST 電路具有良好的測試效益。本文創(chuàng)造性地提出了黃金模塊比對(duì)思想,只需構(gòu)造出與被測模塊等同的電路,對(duì)兩者輸出進(jìn)行比較判斷即可。此外,優(yōu)化改進(jìn)的LFSR 電路結(jié)構(gòu)能夠輸出全地址的偽隨機(jī)測試向量,保證了被測LUT 測試圖形的全覆蓋。相較于其他文獻(xiàn)的BIST 可測性設(shè)計(jì)思路,本文提出的測試方法具有更好的移植性和操作性,可推廣應(yīng)用于FPGA 其他資源的覆蓋率測試。