基于Verilog HDL 的簡易電子琴控制電路設計與實現

張皓祎,鄭冰,盧熾杏,鄭惠之,胡錦程

(航天工程大學 信息學院,北京,101401)

0 引言

聲音是由振動產生的,不同的振動頻率導致了不同的音調[1],目前世界通用的定律方法是十二平均律,根據十二平均律,八度的音程按波長比例被平均分成十二等份,每一等份稱為一個半音(小二度),一個大二度則是兩等份,稱為全音,每兩個半音的頻率比為4。音高八度音指的是頻率加倍,八度音的頻率分為十二等分,即分為十二個等比級數,也就是每個音的頻率為前一個音的2 的12 次方根。

音名“C,D,E,F,G,A,B”的唱名依次為“do,re,mi,fa,sol,la,si”,對應曲譜中的數字“1,2,3,4,5,6”,低音6 的頻率為440Hz,根據十二平均律可計算出低音1 至高音7 的頻率如表1 所示。

表1 音名與頻率的關系

本設計方案基于Verilog HDL 語言實現。Verilog HDL語言是一種常用的硬件描述語言,用于數字電子系統設計。Verilog HDL 語言提供了編程語言接口,通過該接口可以在模擬、驗證期間從設計外部訪問設計,包括模擬的具體控制和運行,使用Verilog 描述硬件的基本設計單元是模塊(Module),構建復雜的電子電路,主要是通過模塊的相互連接調用來實現的。Verilog HDL 語言是目前應用最廣泛的一種硬件描述語言之一。

1 系統整體設計

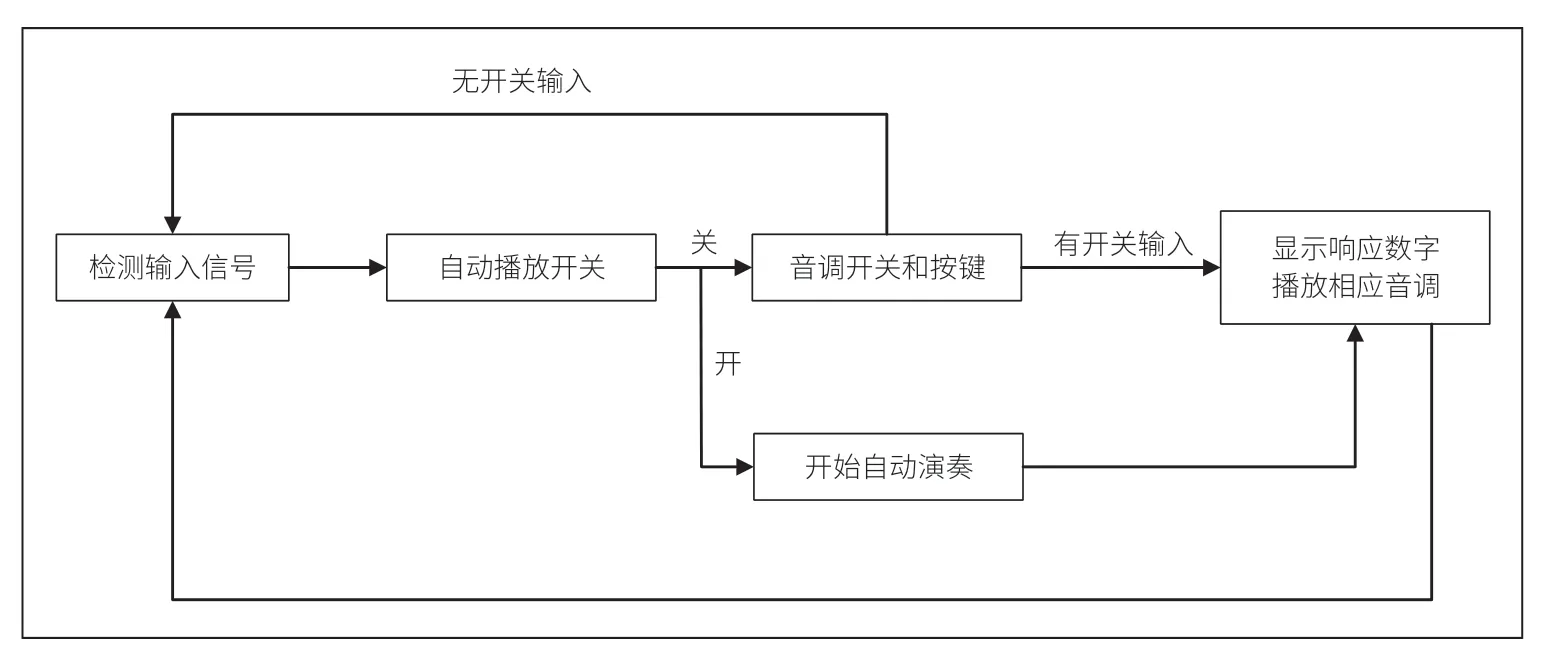

針對設計要求計劃實現的基本功能,擬將本電子系統劃分為音樂播放模塊、數碼管顯示模塊與分頻模塊。其中,音樂播放模塊為頂層模塊,在該模塊中,根據輸入信號的不同決定所播放的音調和傳遞給數碼管顯示模塊的參數,從而實現簡易電子琴的基本功能。

總體設計思路框圖如圖1 所示。

圖1 設計思路框圖

2 分塊設計

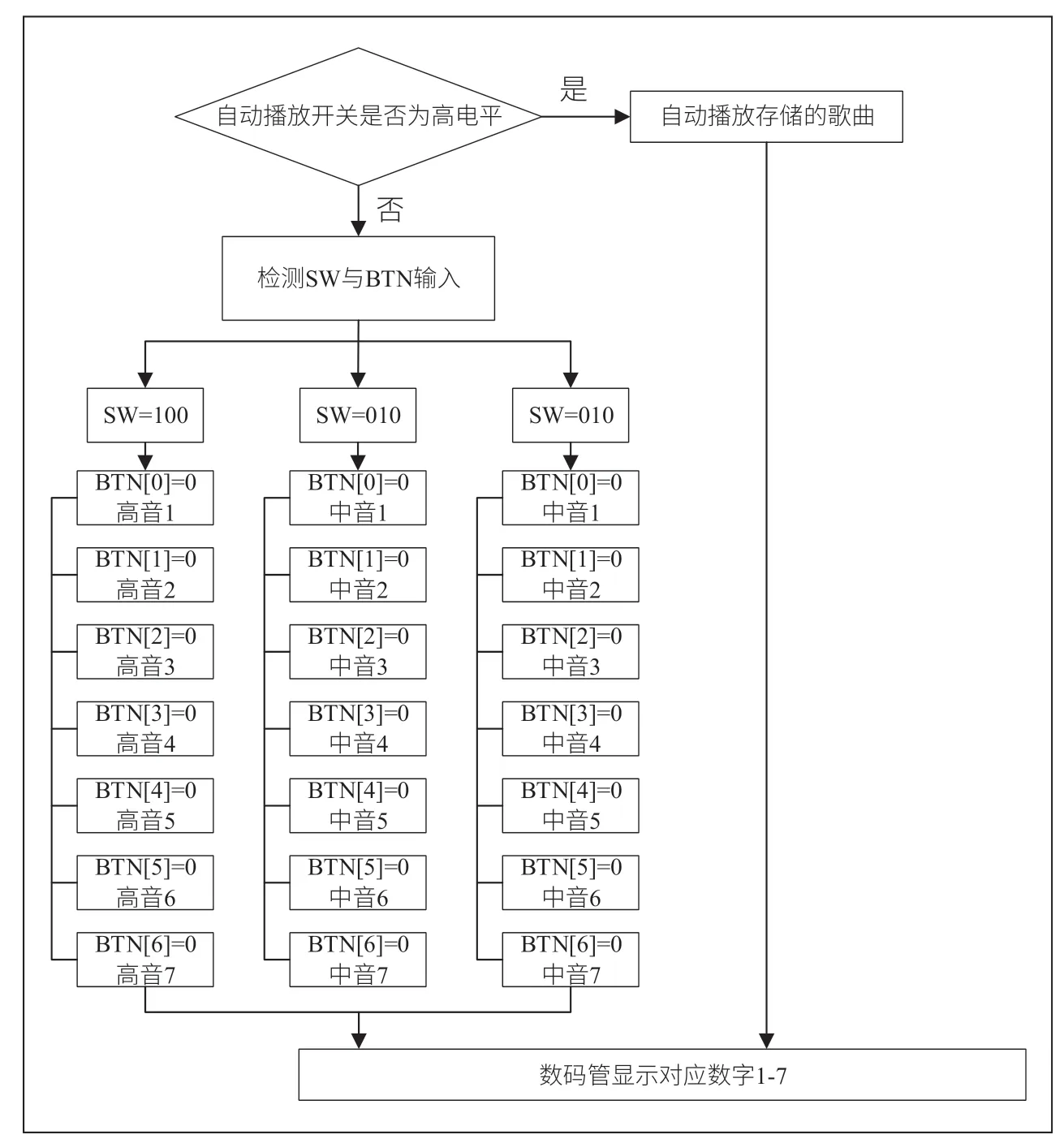

■2.1 頂層模塊

音樂播放模塊為本方案的頂層模塊,在該模塊中,通過調用分頻模塊產生低音、中音、高音三個音域共21 種不同頻率的音符,需要注意的是,除了21 個基準頻率以外,還需分出一個4Hz 的時鐘信號,這是因為大多數簡單樂曲為4/4 拍,即以四分音符為一拍,每小節包含四拍,假設一個全音音符持續時間為1s,那么四分音符的持續時間為0.25s,對應需要一個4Hz 的時鐘信號來控制信號,從而達到最佳的音樂自動播放效果。

在該模塊中,我們設計讓自動播放控制信號為高電平狀態時工作,因此當自動播放控制信號為高電平時,計算機讀取事先存儲在只讀存儲器中的音符,同時用于自動播放的計數器開始計數,通過分頻產生不同頻率的時鐘信號,時鐘信號輸出到蜂鳴器可產生對應的音調,在讀取完整首樂曲音符后,一首音樂便被完美地演奏出來,若控制自動播放控制信號始終為高電平,蜂鳴器則會循環播放預先存儲在程序中的樂曲。當自動播放控制信號為低電平時,切換為手動模式,本設計方案通過音調選擇按鈕SW 的輸入檢測低、中、高音調,通過BTN1~BTN7 七個按鍵的輸入判定所要演奏的音符,并將完成分頻的對應頻率時鐘信號賦值給輸出信號beep,并輸出到蜂鳴器,產生對應的音調;同時,根據BTN 信號的輸入結果,將所選擇的音符信息傳輸給數碼管顯示模塊,顯示音符相對應的數字。

圖2 頂層模塊執行框圖

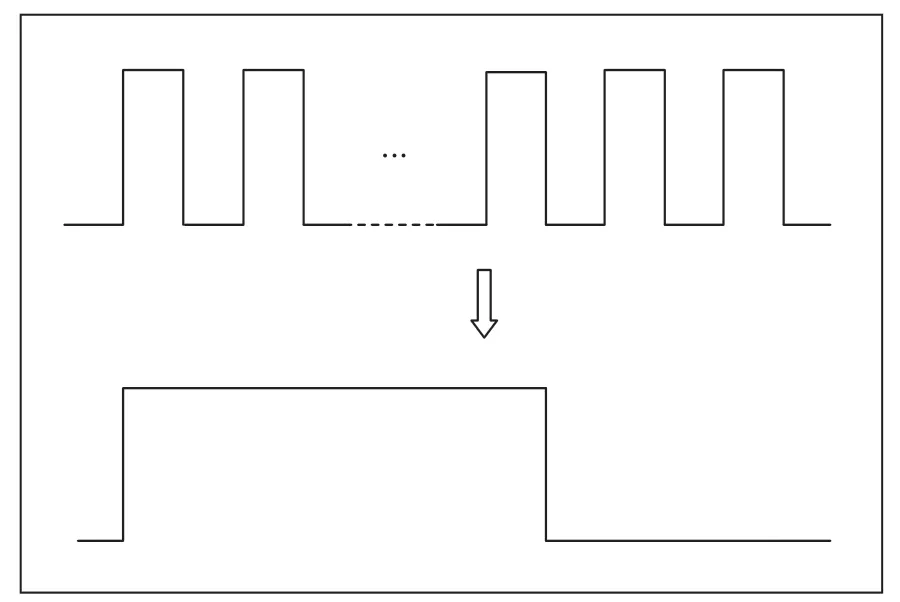

■2.2 音調控制—分頻器設計

不同的振動頻率能夠產生不同的音調,所有不同頻率的信號都能通過對一個基頻分頻得到,為避免逐個分頻導致的編譯代碼冗雜,在本設計方案中定義分頻系數為參數,這樣在每次分頻時,只需調用分頻模塊并輸入所需頻率的分頻系數即可得到所需的時鐘信號[2]。分頻原理如圖3所示。

圖3 分頻原理

分頻器輸入信號為基準時鐘信號(本方案中基準時鐘信號頻率為50MHz),規定輸出為clk_out。每經過基準時鐘信號的一個時鐘信號,分頻器中的計數加一,輸出的頻率信號周期增大一倍,根據分頻原理,計數器計數達到分頻系數時,clk_out 取反,此時即可得到需要的時鐘信號,基于此,可以得到分頻系數的計算公式為:

在實際程序運行時,公式計算出的parameter 作為分頻系數時的分頻效果實際上與以parameter 向下取整的整數作為分頻系數的分頻效果一致,在現實生活中,由于分頻系數大多非整數,本方案統一將parameter 向下取整的整數作為求取不同頻率時鐘信號的最終分頻系數。

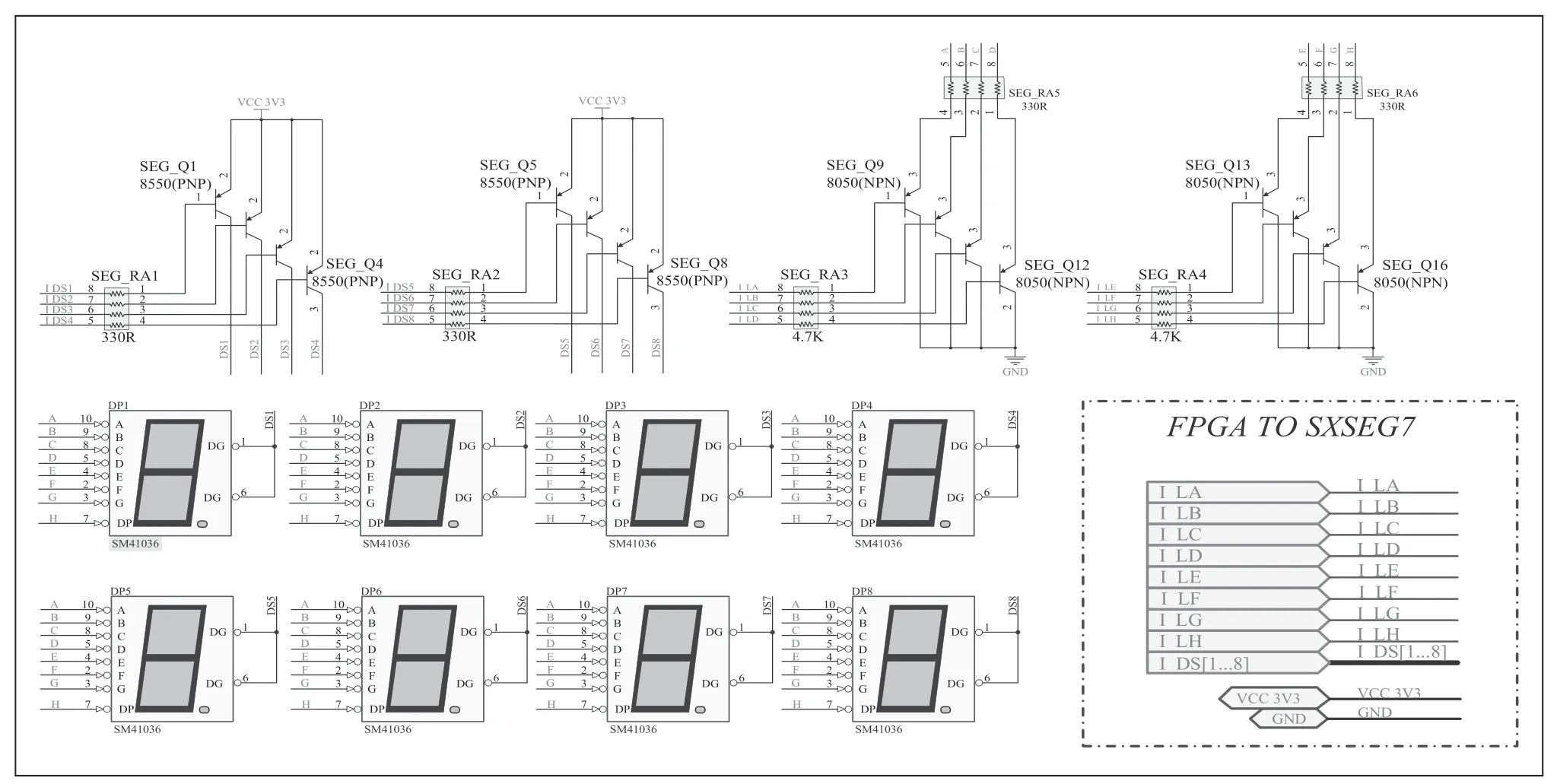

■2.3 數碼管顯示

8 個共陽極七段數碼管的 8 個段碼,共用 FPGA I/O,固定連接在實驗平臺中的FPGA_CON1 處,開發板上8 個7段數碼管的段碼輸入端并聯在一起,8 個位碼相互獨立。當相應碼段SEG 端輸入為高電平,同時需要顯示的數碼管的共陰極端 CAT 為低電平時,該數碼管相應的端就點亮。根據數碼管顯示原理點亮相應碼段,即可顯示所需要的數字。

在本方案中,輸入CAT 信號選通最右側七段數碼管,通過檢測BTN 信號的輸入,從而產生相應的SEG 信號,將SEG 信號輸出給數碼管,數碼管即可顯示輸入音符對應的數字。

3 設計的仿真分析及引腳分配

■3.1 數碼管顯示模塊

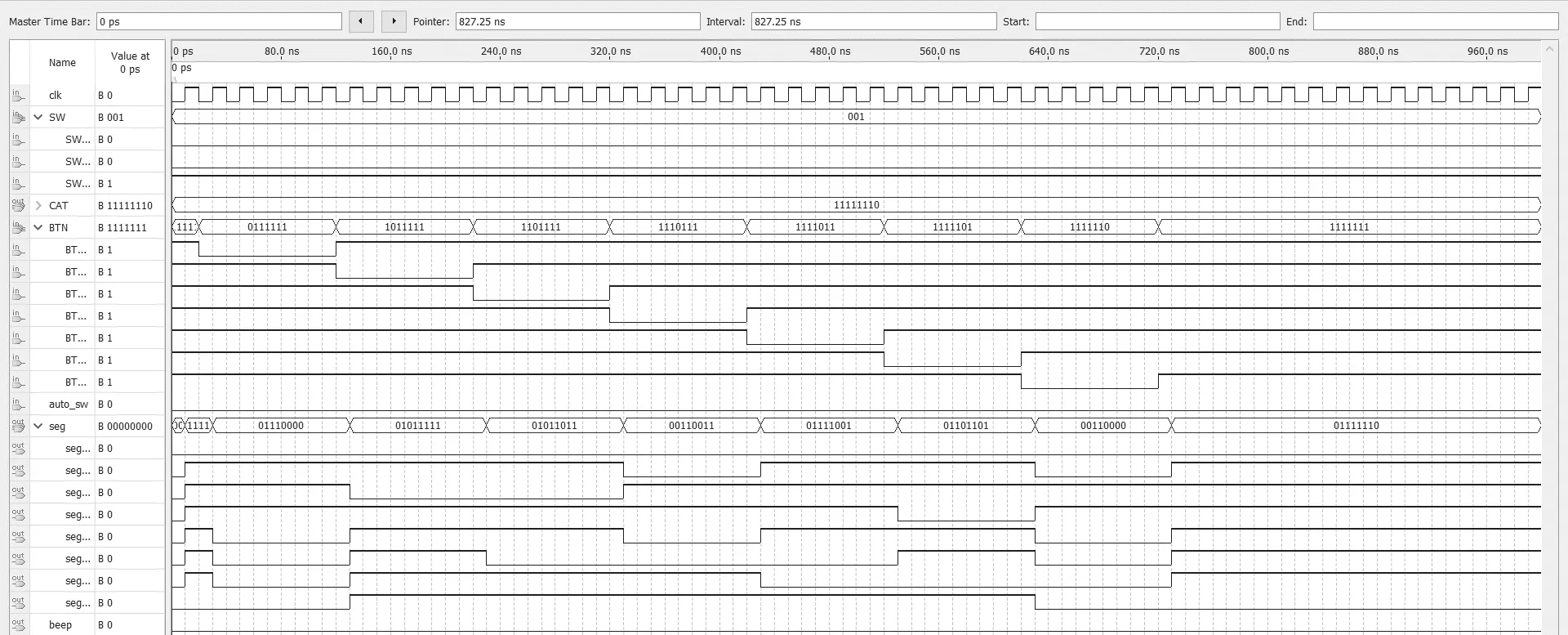

在該模塊的仿真中,通過改變不同時刻的BTN 輸入模擬實際按下按鍵時的行為。仿真波形圖如圖5 所示。

圖4 八個七段數碼管原理圖

圖5 數碼管顯示模塊波形仿真圖

從圖5 中可以看出,隨著按下按鍵的變化,數碼管的輸出信號產生了相應不同形式的變化。數碼管的輸出信號SEG[0]至SEG[7]分別對應了八段數碼管的a,b,c,d,e,f,g 七個顯示段。BTN 輸入信號接綜合實驗箱上的F1~F7 按鍵,該按鍵靜息狀態為高電平,按下時為低電平,與數碼管的結構進行對照可知,BTN[0]至BTN[6]信號分別為低電平時,數碼管上顯示的數字分別為1,2,3,4,5,6,7。

■3.2 分頻模塊

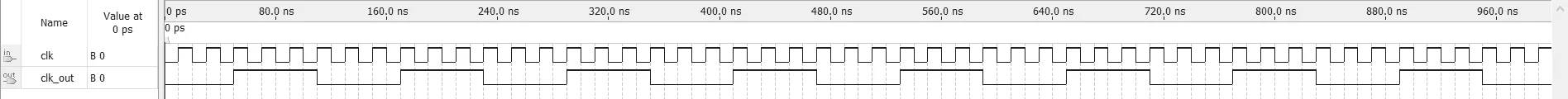

輸入clk 為50MHz 的時鐘信號,通過改變分頻系數,期望得到頻率為基準頻率六分之一的clk_out 時鐘信號。仿真波形圖如圖6 所示。

圖6 分頻模塊波形仿真圖

從圖6 可以看出,分頻后信號周期為原信號周期的六倍,故分頻模塊可以達到所需的效果。

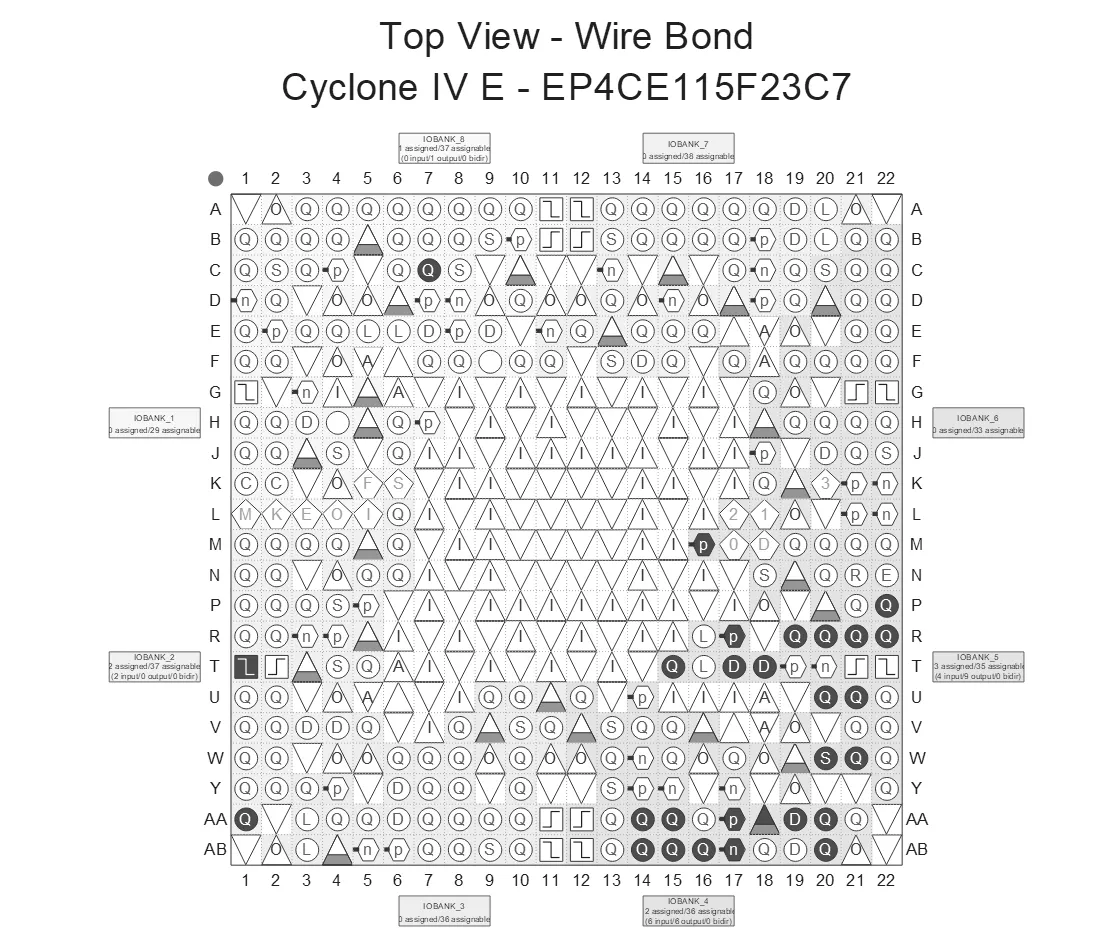

■3.3 FPGA 管腳分配

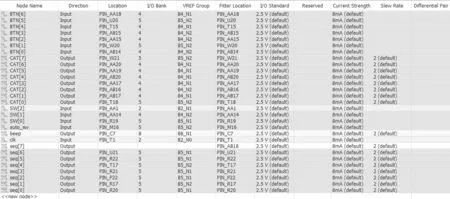

針對SOPC FPGA 平臺的可編程器件實驗板,管腳配置情況如圖7 與圖8 所示。

圖7 實驗板管腳分配圖

圖8 管腳分配圖

方案中的BTN 輸入信號(音符)由實驗板上的F1~F7按鍵控制,按下時為低電平有效信號。SW 音域輸入信號、音樂自動播放信號由實驗板上的SW 按鍵進行控制,SW 按鍵上撥時為高電平有效信號。

基準時鐘信號與實驗板上的PIN_T1 管腳相連,提供50MHz 的基準頻率。

CAT 輸入信號為控制八段數碼管的共陰極端信號,當CAT 輸入位為低電平時,對應數碼管才能工作。

SEG 信號為數碼管顯示信號,與數碼管共陽極端相連,當SEG 信號為高電平狀態時,對應的數碼管顯示段將被點亮。

Beep 為蜂鳴器控制信號,當beep 為高電平狀態時,蜂鳴器輸出對應的音調,否則蜂鳴器將不發聲。

4 小結

本文設計并實現了Verilog HDL 的簡易電子琴控制電路,主要包括音頻播放模塊、分頻模塊和數碼管顯示模塊。分頻模塊實現不同音調的生成,音頻播放模塊實現按鍵彈奏發聲與音頻自動播放,數碼管顯示模塊實現音符的數字顯示。音調準確,節拍符合音樂播放規則,演奏與播放效果較好。