一種基于LabVIEW FPGA 的運載火箭數(shù)字量接口測試方法

黃 皓,劉 靚

(北京宇航系統(tǒng)工程研究所,北京 100076)

在傳統(tǒng)方式下,運載火箭遙測系統(tǒng)綜合試驗中外系統(tǒng)接口功能測試是使用模擬量、指令、數(shù)字量單機測試臺分別模擬相應(yīng)控制系統(tǒng)信號,而該傳統(tǒng)方法中數(shù)字量測試臺中一般使用定制FPGA 板卡來實現(xiàn)脈沖量、計算機字等數(shù)字量信號,但存在以下幾點不足:

(1)每個型號的數(shù)字量測試板卡軟硬件都使用定制開發(fā)方式,會造成相似種類設(shè)備重復(fù)設(shè)計生產(chǎn),不利于狀態(tài)升級迭代和舉一反三。

(2)無論代碼更新或型號移植,需要數(shù)字量板卡重新燒錄底層FPGA 邏輯代碼,而板卡多為定制板卡,需要拆卸取出單板,進行單板加電燒寫程序后再聯(lián)調(diào),無法靈活便捷實現(xiàn)測試設(shè)備資源調(diào)試和復(fù)用。

(3)硬件底層編程和與上位機軟件在不同軟件開發(fā)工具下編譯開發(fā),因此需要開發(fā)人員具備多種軟件開發(fā)能力,編程人員調(diào)試開發(fā)時間和難度會增加。

FPGA 技術(shù)有很多優(yōu)勢,如可以自定義I/O 硬件時序邏輯、擁有較強的數(shù)字信號處理能力等,但因為配置FPGA 需要VHDL 編程的專業(yè)知識或復(fù)雜的設(shè)計工具,而這些工作通常又是由硬件設(shè)計工程師,而非測試和控制工程師所完成的,所以系統(tǒng)的終端用戶往往不愿開發(fā)自己的基于FPGA 的系統(tǒng),只能通過定制設(shè)計的硬件才能夠完成創(chuàng)建復(fù)雜精密的測量和控制系統(tǒng)[1]。

為解決傳統(tǒng)測試方式的不足,本文設(shè)計了一種研制基于通用PXI 總線模塊的外系統(tǒng)接口等效器用于接口功能測試,采用PXI DA 板卡作為模擬量信號源,PXI 繼電器開關(guān)板卡作為指令信號源,而數(shù)字量信號采用NI FPGA 可編程邏輯板卡模擬數(shù)字量時序邏輯。盡管不同型號的數(shù)字量信號邏輯協(xié)議和數(shù)據(jù)位數(shù)可能存在不一致,但可以將相同硬件部分復(fù)用,硬件程序部分使用上位機軟件LabVIEW FPGA 模塊靈活編譯下載,無需硬件連線來燒寫新程序,從而實現(xiàn)不同型號之間的靈活通用方式,并且接口通訊協(xié)議的更新可通過LabVIEW 在線編程編譯后升級底層邏輯關(guān)系,該方法適用于外系統(tǒng)接口測試同時兼容多型號不同時序傳輸協(xié)議[2]。

1 信號分析及設(shè)備系統(tǒng)架構(gòu)

1.1 數(shù)字量信號模擬要求

以陀螺脈沖參數(shù)性質(zhì)為例,接口電路如圖1 所示,輸出脈沖的數(shù)字信號電平參數(shù)要求如下:

圖1 陀螺脈沖測試接口Fig.1 Gyro pulse testing interface

(1)幅度:0~5 V;

(2)脈沖寬度:1 μs~4 ms 內(nèi),由FPGA 設(shè)置;

(3)頻率:小于等于500 kHz,由FPGA 設(shè)置。

而計算機字協(xié)議為在接收到中斷請求脈沖后,在要求時間內(nèi)向遙測系統(tǒng)傳輸完一個遙測字,如圖2 所示。因此等效器設(shè)計時需要在硬件和軟件協(xié)議上滿足接口要求,從而實現(xiàn)對數(shù)字量參數(shù)的信號模擬。

圖2 計算機系統(tǒng)測試接口時序Fig.2 Timing of computer system test interface

1.2 設(shè)備系統(tǒng)架構(gòu)和組成

外系統(tǒng)接口等效器中激勵信號模塊的設(shè)計架構(gòu)要求基于PXI 儀器組合與信號調(diào)理組合的方式,其中數(shù)字量信號模擬源采用NI PXI-7841R 數(shù)字板卡編程模塊來實現(xiàn)數(shù)字邏輯協(xié)議,它提供的可編程FPGA芯片,適合板載處理和靈活的I/O操作。本文使用的是PXIe-7854R 下的FPGA 板卡,型號為Xilinx Virtex-5 LX110,它由64 個乘法器,69120 個觸發(fā)器,69120 個查找表和4608 Kb Block RAM 構(gòu)成。它硬件部分是一種具有可重復(fù)配置邏輯門的芯片,在程序設(shè)計和實現(xiàn)上具有很強的靈活性,它可根據(jù)不同的需要而進行配置和修改。同時,它還具有精確時序和同步、快速決策及并行任務(wù)同時執(zhí)行等優(yōu)點,其主要指標如下:

(1)8 路模擬輸入,200 kHz 獨立采樣率,16 位分辨率,±10 V;

(2)8 路模擬輸出,1 MHz 獨立更新率,16 位分辨率,±10 V;

(3)96 條數(shù)字線,可配置為速率高達40 MHz 的輸入、輸出、計時器或自定義邏輯;

(4)Virtex-5 LX50 FPGA,可通過LabVIEW FPGA 模塊對其編程;

(5)3 路直接存儲器訪問(DMA)通道,用于高速硬盤數(shù)據(jù)讀寫。

外系統(tǒng)接口等效器的調(diào)理組合和適配器完成硬件接口的轉(zhuǎn)換,輸出數(shù)字脈沖信號具體實現(xiàn)接口電路如圖3 所示。

圖3 數(shù)字信號輸出調(diào)理接口電路Fig.3 Interface circuit of digital signal output conditioning

2 軟件設(shè)計

外系統(tǒng)等效器采用LabVIEW 界面開發(fā)工具實現(xiàn)程序界面和底層邏輯編寫。其中界面開發(fā)使用LabVIEW 面板設(shè)計,而測試邏輯采用LabVIEW 實現(xiàn)狀態(tài)機方式,采用ACCESS 數(shù)據(jù)庫形式管理流程配置信息、硬件映射關(guān)系和測試結(jié)果,軟件讀取裝載流程配置文件,可解析出流程配置信息,并通過硬件映射關(guān)系轉(zhuǎn)換為底層板卡執(zhí)行指令,最終將測試結(jié)果保存進結(jié)果數(shù)據(jù)庫。

其中FPGA 的程序?qū)儆诎蹇y試邏輯的特殊部分,由于FPGA 為內(nèi)部邏輯可編輯的硬件,由Lab-VIEW FPGA 編譯工具實現(xiàn),編譯后的程序可在線下載到FPGA 板卡,由上位機流程調(diào)用并執(zhí)行。

2.1 FPGA 開發(fā)流程

LabVIEW 是一種用圖表代替文本創(chuàng)建應(yīng)用程序的圖形化編程語言,LabVIEW FPGA 是LabVIEW的一個子模塊,用戶可借助NI LabVIEW 圖形化程序框圖和NI LabVIEW FPGA 模塊,配置各項數(shù)字量專用通信協(xié)議。

通過對LabVIEW FPGA 圖形化的編程開發(fā)可以快速地開發(fā)實現(xiàn)數(shù)字量信號的模擬系統(tǒng),同時也使工程設(shè)計人員無須了解或其他的硬件開發(fā)工具即可開發(fā)系統(tǒng),使用開發(fā)應(yīng)用程序的典型流程如圖4 所示[3]。

圖4 LabVIEW 開發(fā)FPGA 流程Fig.4 Developing FPGA flow chart with LabVIEW

首先創(chuàng)建FPGA VI,使用LabVIEW FPGA 軟件在主控計算機上運行程序,反復(fù)地進行調(diào)試、修改,直至程序邏輯正確無誤、滿足設(shè)計要求。然后編譯FPGA VI,并把程序下載到FPGA 板卡。在上述FPGA程序完成后,在主控計算機上創(chuàng)建用戶界面程序Host VI,使用Host VI 通過FPGA 輸入輸出接口來調(diào)用FPGA VI,最終就完成了整個系統(tǒng)的設(shè)計,如圖5 所示。

圖5 頂層Host 調(diào)用FPGA 程序Fig.5 Top Host program of calling FPGA

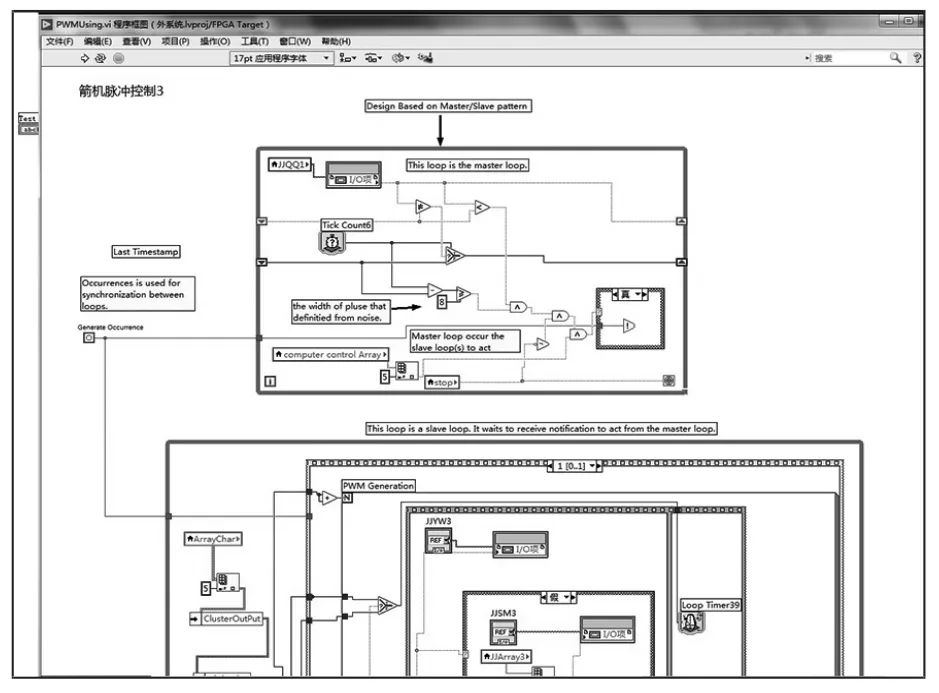

FPGA 程序根據(jù)協(xié)議編寫數(shù)字量的脈沖數(shù)和計算機字的操作,并預(yù)留對Host VI 的接口參數(shù),比如脈沖數(shù)的個數(shù)、脈沖寬度、計算機字的十六進制內(nèi)容等。其中以計算機字為例,測量系統(tǒng)的發(fā)送請求建立中斷響應(yīng),當(dāng)監(jiān)測到發(fā)送信號請求時,開始根據(jù)協(xié)議輸出移位信號和計算機字。在這個中斷響應(yīng)中,需要LabVIEW FPGA 建立一個中斷,其中一個循環(huán)框圖為設(shè)定中斷的條件,即當(dāng)條件滿足時中斷產(chǎn)生。另外一循環(huán)框圖為中斷執(zhí)行內(nèi)容,當(dāng)產(chǎn)生中斷后,將執(zhí)行循環(huán)框圖中的內(nèi)容。如圖6 所示,上框圖循環(huán)監(jiān)測請求脈寬信號是否達到要求,當(dāng)為正常請求脈沖時將產(chǎn)生中斷,中斷產(chǎn)生后執(zhí)行下框圖中的發(fā)送移位和計算機字信號。

圖6 FPGA VI 中斷響應(yīng)程序Fig.6 FPGA VI interrupt response program

2.2 用戶層設(shè)計

程序設(shè)計中多事件之間的邏輯關(guān)系必須正確,否則程序可能陷入死循環(huán)等錯誤,從而造成測試系統(tǒng)死機。自動流程執(zhí)行在此類問題處理的是否得當(dāng)決定了程序運行的效率和可靠性。

狀態(tài)機不僅可以使程序中多事件之間的邏輯關(guān)系更簡潔明了,同時它強大的錯誤處理能力、用戶選擇測試、條件執(zhí)行等功能使多事件間的邏輯關(guān)系處理變得更為簡單。一般可以用狀態(tài)圖來對一個狀態(tài)機精確地描述。LabVIEW 狀態(tài)機由一個While主循環(huán)和一個case 結(jié)構(gòu)組成,并利用位寄存器來實現(xiàn)狀態(tài)的跳轉(zhuǎn)。While 循環(huán)保證狀態(tài)機的連續(xù)運行,case 結(jié)構(gòu)的分支與狀態(tài)一一對應(yīng),即case 結(jié)構(gòu)的分支名稱對應(yīng)著狀態(tài)名稱,分支里執(zhí)行代碼的功能對應(yīng)著狀態(tài)的行為,而case 結(jié)構(gòu)的條件變量與系統(tǒng)事件相對應(yīng),引發(fā)狀態(tài)的變遷及決定狀態(tài)遷移的方向。狀態(tài)機的While Loop+Case 結(jié)構(gòu)+位移寄存器的框架使得程序的結(jié)構(gòu)更為清晰,再次修改也甚為方便[4]。

在LabVIEW 狀態(tài)機程序編寫設(shè)計時需要注意編程習(xí)慣,如圖7 所示,一般完成以下方面:

圖7 狀態(tài)機程序圖Fig.7 State machine program diagram

(1)狀態(tài)用于區(qū)分不同狀態(tài),可以使用數(shù)字對應(yīng)相應(yīng)狀態(tài)。

(2)一般應(yīng)該有:初始化、空閑、信號準備、信號輸出、信號采集、判讀、停止?fàn)顟B(tài)。本程序所需執(zhí)行狀態(tài)為7 個狀態(tài),結(jié)束為程序退出循環(huán)。

(3)“初始化”進行一些初始化的操作;“空閑”是一種過渡狀態(tài),用于和用戶打交道的狀態(tài);“準備”為激勵信號輸出前的準備操作,比如數(shù)字量設(shè)置等等;“信號輸出”為數(shù)字量、D/A、指令等激勵信號的輸出控制;“信號采集”為信號采集;“判讀”為對單步測試結(jié)果的判讀,并決定下一步跳轉(zhuǎn)狀態(tài)。

(4)狀態(tài)始終貫穿整個應(yīng)用程序,并由移位寄存器進行狀態(tài)值的寄存和傳遞。當(dāng)前狀態(tài)分支的結(jié)果將決定下一個狀態(tài)。

3 實驗結(jié)果及分析

LabVIEW FPGA 程序編譯下載到NI PXI-7841R后,使用Host VI 設(shè)置計算機字調(diào)試檢查等效器發(fā)送的信號,等效器設(shè)定發(fā)送0xD5D5 計算機字的示波器信號監(jiān)測圖,如圖8 所示,從示波器信號看出LabVIEW FPGA 程序邏輯與設(shè)計要求一致。

圖8 計算機字數(shù)字信號圖Fig.8 Diagram of digital signal computer word

測試界面如圖9 所示,選擇測試流程,點擊“自動執(zhí)行”,即自動執(zhí)行測試流程,測試流程每步測試會自動顯示返回值,并且比對返回值與設(shè)定合格條件,顯示每項判讀結(jié)果是“合格”或“不合格”。若由流程中任意一步測試結(jié)果不合格,則總結(jié)果判定為不合格,且“測試狀態(tài)”燈由綠變紅。例如等效器模擬源發(fā)送計算機字為0x2345678AB,若遙測采集計算機字的值為0x2345678AB,則判讀結(jié)果為合格。

圖9 外系統(tǒng)等效器測試圖Fig.9 External system equivalent test diagram

4 結(jié)語

利用LabVIEW FPGA 模塊可在線編程的功能可實現(xiàn)控制系統(tǒng)的數(shù)字量信號模擬的靈活配置,本文使用PXI7841R 卡和LabVIEW 圖形化編程方式,通過上位機在線下載和編譯FPGA 邏輯,完成脈沖量和計算機字等數(shù)字量信號模擬,實現(xiàn)調(diào)用不同程序適配不同型號要求,達到了數(shù)字量信號時序邏輯的軟件自定義的目的,最終大幅度提高了設(shè)備的設(shè)計周期和成本。經(jīng)實驗驗證,系統(tǒng)運行良好,本設(shè)計方法開發(fā)周期短、可靠性高、功能擴展性強。