一種基于FPGA的萬兆以太網(wǎng)MAC層設(shè)計(jì)與實(shí)現(xiàn)

安超群 李飛

作者簡(jiǎn)介:安超群(1986— ),女,湖北襄陽人,工程師,碩士;研究方向:模擬電路設(shè)計(jì),集成電路設(shè)計(jì),數(shù)字信號(hào)處理,可靠性設(shè)計(jì)等。

摘要:針對(duì)基于軟件設(shè)計(jì)的萬兆以太網(wǎng)MAC層無法滿足高速數(shù)據(jù)實(shí)時(shí)傳輸?shù)陌l(fā)展要求,文章提出了一種基于FPGA硬件平臺(tái)的萬兆以太網(wǎng)MAC層協(xié)議的設(shè)計(jì)與實(shí)現(xiàn)方案。該設(shè)計(jì)方案主要利用FPGA的并行處理能力,通過Verilog硬件描述語言完成萬兆以太網(wǎng)MAC層數(shù)據(jù)實(shí)時(shí)處理的硬件設(shè)計(jì),實(shí)現(xiàn)大帶寬、低延時(shí)和高可靠性的萬兆以太網(wǎng)MAC層的數(shù)據(jù)收發(fā)功能。試驗(yàn)驗(yàn)證表明:該設(shè)計(jì)方案實(shí)現(xiàn)了萬兆以太網(wǎng)高速率的數(shù)據(jù)傳輸,具有低延時(shí)、高性能、高可靠性與簡(jiǎn)易性等優(yōu)點(diǎn)。

關(guān)鍵詞:萬兆以太網(wǎng);MAC控制器;并行CRC校驗(yàn);并行數(shù)據(jù)處理

中圖分類號(hào):TP311? 文獻(xiàn)標(biāo)志碼:A

0? 引言

以太網(wǎng)(Ethernet)是一種計(jì)算機(jī)局域網(wǎng)技術(shù)。IEEE制定的IEEE Std 802.3協(xié)議,規(guī)定了包括MAC層的協(xié)議內(nèi)容、電信號(hào)以及物理層的連線。從1983年第一次發(fā)布IEEE Std 802.3協(xié)議至今,以太網(wǎng)經(jīng)過了40年的發(fā)展,傳輸速率從10 Mbps、100Mbps提升到1 000Mbps,目前已經(jīng)達(dá)到了10 Gbps[1]。萬兆以太網(wǎng)是也稱10 G以太網(wǎng)(10 Gigabit Ethernet),是在IEEE802.3ae協(xié)議中提出的以太網(wǎng)標(biāo)準(zhǔn),該標(biāo)準(zhǔn)規(guī)范中規(guī)定使用光纖傳輸、傳輸帶寬高達(dá)10 Gbps、傳輸距離最遠(yuǎn)能達(dá)到40km [2],經(jīng)過不斷的升級(jí)與擴(kuò)充,萬兆以太網(wǎng)以其速率高、兼容性好、穩(wěn)定性強(qiáng)的優(yōu)點(diǎn)逐漸成為以太網(wǎng)的核心設(shè)備[3],服務(wù)于工業(yè)自動(dòng)化、5G網(wǎng)絡(luò)傳輸和智慧城市建設(shè)等行業(yè)。

大多數(shù)系統(tǒng)設(shè)計(jì)中,10Mbps、100Mbps和1 000Mbps以太網(wǎng)協(xié)議除了物理層以外的協(xié)議層均以軟件的方式實(shí)現(xiàn),甚至10 Gbps以太網(wǎng)協(xié)議使用高性能CUP或服務(wù)器實(shí)現(xiàn)。基于串行處理的軟件架構(gòu)難以并行處理以太網(wǎng)協(xié)議中的各種事務(wù),同時(shí)CPU還要優(yōu)先響應(yīng)中斷事務(wù),隨著技術(shù)的發(fā)展,CPU的處理頻率已經(jīng)大幅提高,同時(shí)可以用多核CPU來處理多任務(wù)。但是,以太網(wǎng)速度的提升遠(yuǎn)大于CPU處理性能的提升,使得CPU能夠用來處理單個(gè)網(wǎng)絡(luò)數(shù)據(jù)包的時(shí)間減少。如果CPU不能及時(shí)處理網(wǎng)絡(luò)數(shù)據(jù)包,那必然會(huì)影響網(wǎng)絡(luò)傳輸?shù)难訒r(shí)和吞吐量[4]。因此,基于軟件控制實(shí)現(xiàn)的10 Gbps以太網(wǎng)協(xié)議數(shù)據(jù)傳輸效率較低,難以滿足大帶寬、低延時(shí)和高可靠性的數(shù)據(jù)傳輸。根據(jù)高速數(shù)據(jù)傳輸?shù)奶幚硪螅Y(jié)合以太網(wǎng)的傳輸協(xié)議,引入一種并行的以太網(wǎng)協(xié)議處理方式是解決大帶寬、高速率數(shù)據(jù)處理需求和軟件計(jì)算能力有限之間矛盾的有效方法。

1? 萬兆以太網(wǎng)通信協(xié)議架構(gòu)

1.1? 萬兆以太網(wǎng)各協(xié)議層的組成

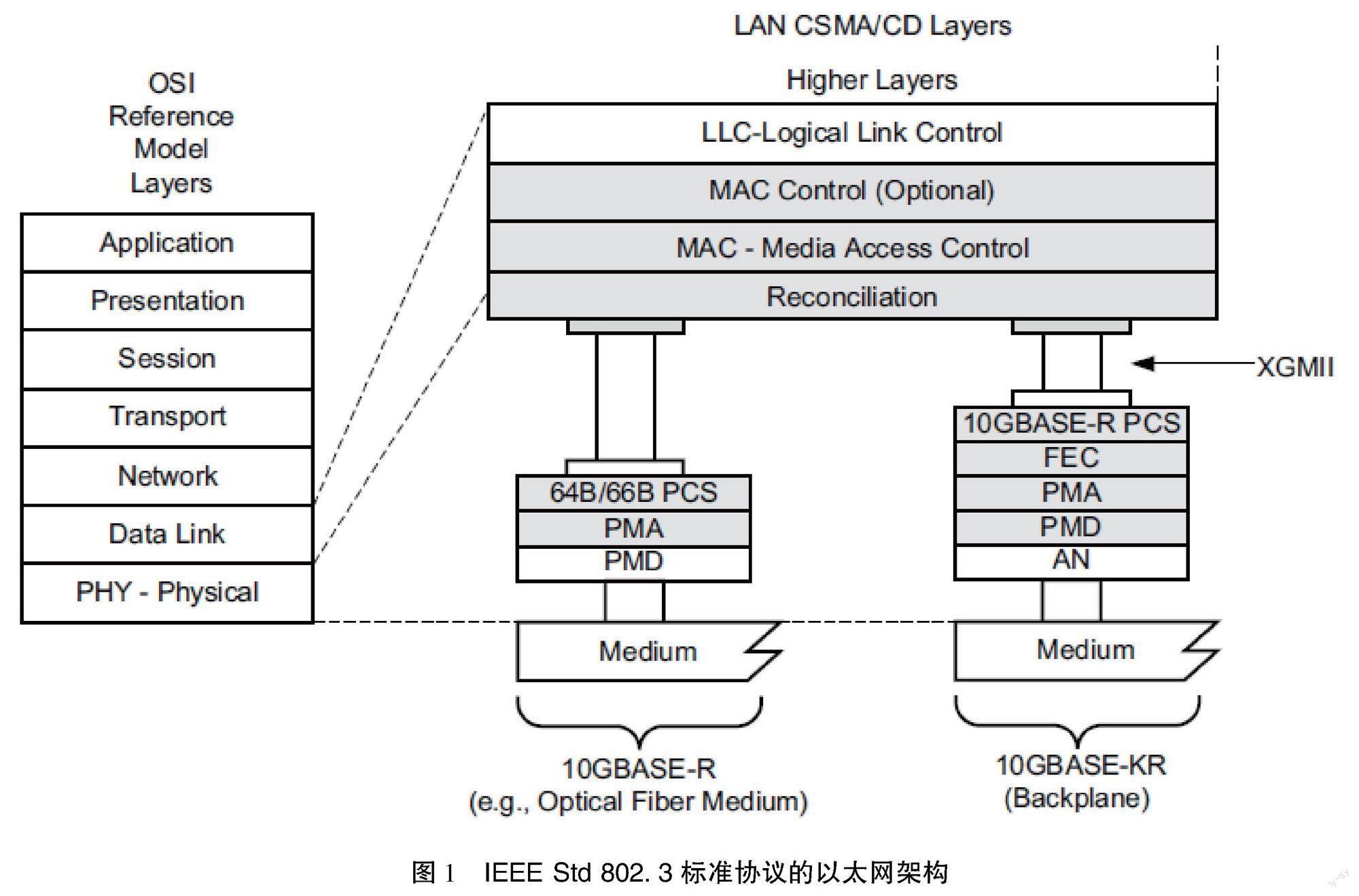

基于IEEE Std 802.3標(biāo)準(zhǔn)的萬兆以太網(wǎng)協(xié)議架構(gòu)如圖1所示,其架構(gòu)主要包括:應(yīng)用層(Application)、表示層(Presentation)、會(huì)話層(Session)、傳輸層(Transport)、網(wǎng)絡(luò)層(Network)、數(shù)據(jù)鏈路層(Data_link)和物理層(Physical)。其中,數(shù)據(jù)鏈路層提供物理地址尋址,讓成幀的數(shù)據(jù)按一定規(guī)則沿鏈路從一個(gè)節(jié)點(diǎn)傳到另一個(gè)節(jié)點(diǎn),負(fù)責(zé)發(fā)送一個(gè)分段內(nèi)的數(shù)據(jù),常見的鏈路層產(chǎn)品就是網(wǎng)卡、網(wǎng)橋等[5];物理層主要規(guī)范了數(shù)據(jù)傳輸?shù)拿浇椤⑽锢磉B接及光電特性能內(nèi)容,保證光電信號(hào)的可靠傳輸。

1.2? 萬兆以太網(wǎng)MAC層特性

萬兆以太網(wǎng)協(xié)議標(biāo)準(zhǔn)中規(guī)定,整個(gè)數(shù)據(jù)通信過程系統(tǒng)的物理層(Physical)通信速率必須具備10 Gbps帶寬的數(shù)據(jù)傳輸能力。根據(jù)協(xié)議規(guī)定,數(shù)據(jù)在物理層的傳輸速率是比較固定的,除了受到器件的物理特性的影響外,設(shè)計(jì)者在這一層級(jí)的優(yōu)化設(shè)計(jì)沒有太大的空間。應(yīng)用層(Application)、表示層(Presentation)和會(huì)話層(Session)的使用主要涉及具體的業(yè)務(wù),這些層級(jí)功能主要靠軟件實(shí)現(xiàn)。在協(xié)議中傳輸層(Transport)、網(wǎng)絡(luò)層(Network)和數(shù)據(jù)鏈路層(Data_link)事務(wù)定義明確,因此具有一定的提速空間。本文主要重點(diǎn)優(yōu)化設(shè)計(jì)數(shù)據(jù)鏈路層的數(shù)據(jù)處理速率。

由圖1可知,數(shù)據(jù)鏈路層的數(shù)據(jù)處理過程主要是將用戶數(shù)據(jù)進(jìn)行MAC層協(xié)議的封裝,MAC層協(xié)議的封裝主要涉及傳輸控制協(xié)議(TCP)和用戶數(shù)據(jù)報(bào)協(xié)議(UDP)。TCP 的傳輸速度慢,效率低,確認(rèn)機(jī)制、重傳機(jī)制、擁塞控制等都會(huì)占用大量的時(shí)間[6]。UDP協(xié)議具備傳輸速率塊、效率高等優(yōu)點(diǎn),如果能夠研究出有效可靠的數(shù)據(jù)處理流程保證UDP協(xié)議數(shù)據(jù)傳輸?shù)目煽啃裕褂肬DP協(xié)議傳輸數(shù)據(jù)將大大提高數(shù)據(jù)傳輸系統(tǒng)的數(shù)據(jù)處理速率。

2? 基于FPGA的萬兆以太網(wǎng)高效率MAC層設(shè)計(jì)與實(shí)現(xiàn)

2.1? 高效率低延時(shí)萬兆以太網(wǎng)MAC架構(gòu)設(shè)計(jì)

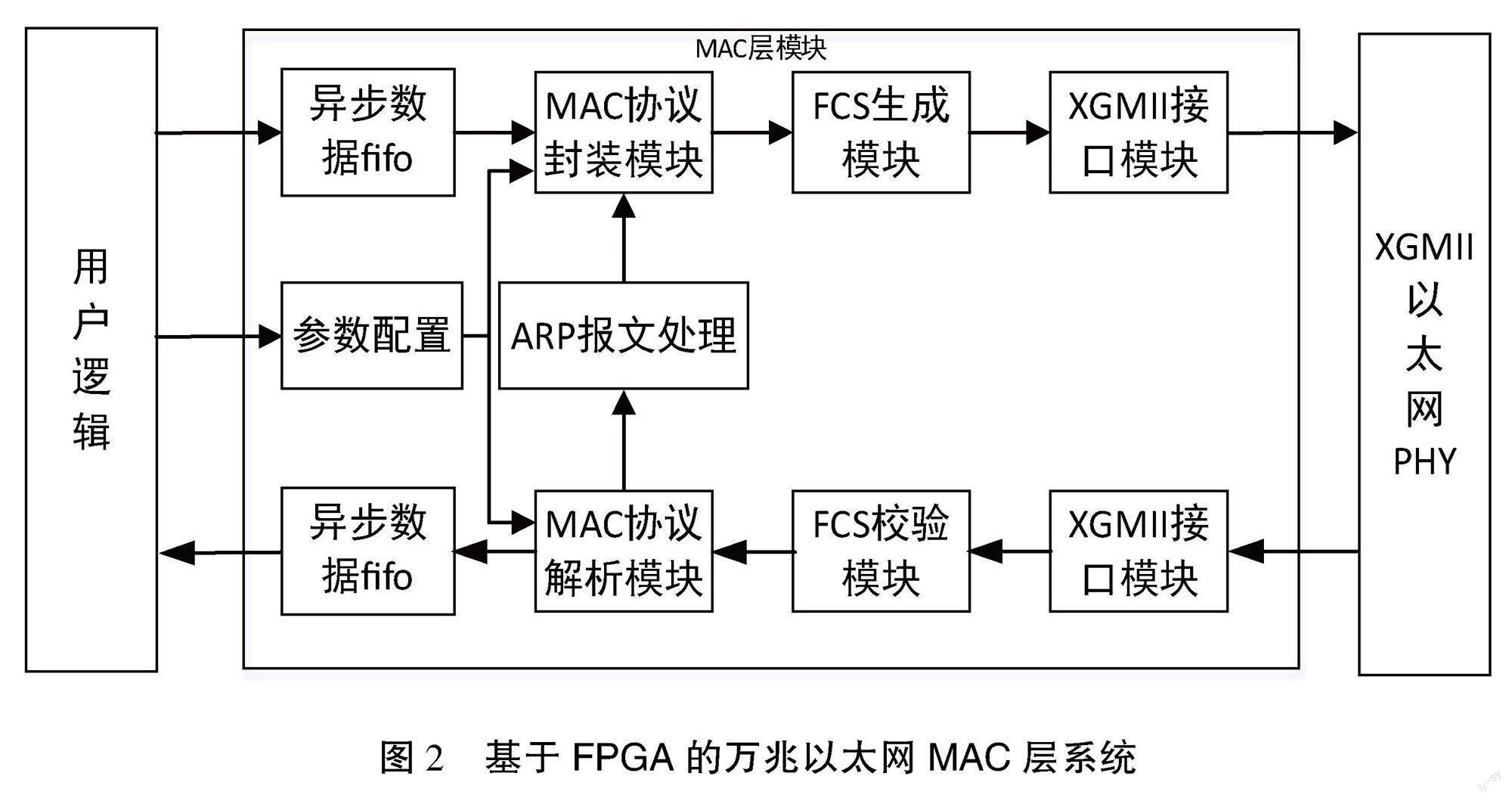

根據(jù)前面分析,應(yīng)用FPGA的并行處理能力實(shí)現(xiàn)萬兆以太網(wǎng)高效率的數(shù)據(jù)鏈路層,并對(duì)其可靠性進(jìn)行驗(yàn)證,可實(shí)現(xiàn)高效率的UDP協(xié)議數(shù)據(jù)傳輸。基于FPGA的萬兆以太網(wǎng)MAC層架構(gòu)如圖2所示。用戶邏輯使用AXI4協(xié)議進(jìn)行數(shù)據(jù)交互,MAC層模塊內(nèi)使用異步FIFO對(duì)數(shù)據(jù)進(jìn)行跨時(shí)鐘域處理,通過參數(shù)配置模塊對(duì)MAC層模塊進(jìn)行本地MAC地址、本地IP地址、ARP控制參數(shù)和端口號(hào)等參數(shù)配置。在發(fā)送通路中,MAC協(xié)議封裝模塊將異步FIFO輸出的數(shù)據(jù)按UDP協(xié)議添加UDP包頭、IP包頭和MAC幀頭,將數(shù)據(jù)封裝成MAC幀,再將數(shù)據(jù)傳輸至FCS生成模塊生成CRC校驗(yàn)數(shù)據(jù),最后將數(shù)據(jù)送至XGMII接口處理模塊進(jìn)行處理發(fā)送。在MAC協(xié)議封裝模塊中,要同時(shí)響應(yīng)用戶數(shù)據(jù)和ARP報(bào)文數(shù)據(jù),其中ARP報(bào)文優(yōu)先級(jí)最高。在接收通路中,在接收前端先將XGMII結(jié)構(gòu)數(shù)據(jù)轉(zhuǎn)換成MAC幀,將MAC幀數(shù)據(jù)送至FCS校驗(yàn)?zāi)K進(jìn)行CRC校驗(yàn),數(shù)據(jù)校驗(yàn)正確后再將數(shù)據(jù)送至MAC協(xié)議解析模塊進(jìn)行處理,解析完成后按照接收的數(shù)據(jù)類型將數(shù)據(jù)傳至異步FIFO或者將信息傳至ARP報(bào)文處理模塊進(jìn)行ARP應(yīng)答。

2.2? MAC層事務(wù)數(shù)據(jù)并行處理算法

根據(jù)圖2分析,MAC層數(shù)據(jù)處理算法流收發(fā)模塊相互獨(dú)立,處于全雙工工作狀態(tài)。同時(shí),F(xiàn)CS模塊中CRC校驗(yàn)和計(jì)算根據(jù)數(shù)據(jù)長(zhǎng)度不同,分別設(shè)計(jì)了并行處理的64 bit、56 bit、48 bit、40 bit、32 bit、24 bit、16 bit和8 bitCRC校驗(yàn)子模塊,最多只需要1個(gè)時(shí)鐘周期就能完成64 bit數(shù)據(jù)的校驗(yàn)和幀尾不同長(zhǎng)度字節(jié)數(shù)據(jù)的驗(yàn)證,在一幀數(shù)據(jù)傳輸結(jié)束標(biāo)準(zhǔn)產(chǎn)生時(shí)能同步無延時(shí)地輸出校驗(yàn)結(jié)構(gòu),很大程度提高了數(shù)據(jù)傳輸效率。在系統(tǒng)初始階段,MAC層模塊根據(jù)系統(tǒng)配置的參數(shù)向目標(biāo)主機(jī)發(fā)送ARP報(bào)文請(qǐng)求,等待系統(tǒng)返回ARP幀獲取主機(jī)MAC地址。在MAC層模塊設(shè)計(jì)中,可通過參數(shù)配置設(shè)定ARP報(bào)文請(qǐng)求次數(shù),等待報(bào)文超時(shí)時(shí)間等參數(shù),目標(biāo)主機(jī)發(fā)送ARP報(bào)文請(qǐng)求時(shí),MAC層模塊將優(yōu)先回復(fù)ARP報(bào)文。

在整個(gè)MAC層模塊中,UDP協(xié)議的封裝和解析,IP層協(xié)議的封裝和解析,MAC層的協(xié)議的封裝和解析大都直接調(diào)用系統(tǒng)預(yù)先配置的參數(shù)封裝和完成解析,這樣處理大大提高了數(shù)據(jù)的處理效率。IP校驗(yàn)和計(jì)算和校驗(yàn)結(jié)果均能實(shí)時(shí)地計(jì)算完成,ARP報(bào)文處理、ICMP報(bào)文處理和數(shù)據(jù)幀處理均能實(shí)時(shí)地響應(yīng),降低了數(shù)據(jù)傳輸延時(shí),提高了系統(tǒng)性能。

3? 系統(tǒng)實(shí)現(xiàn)及試驗(yàn)驗(yàn)證

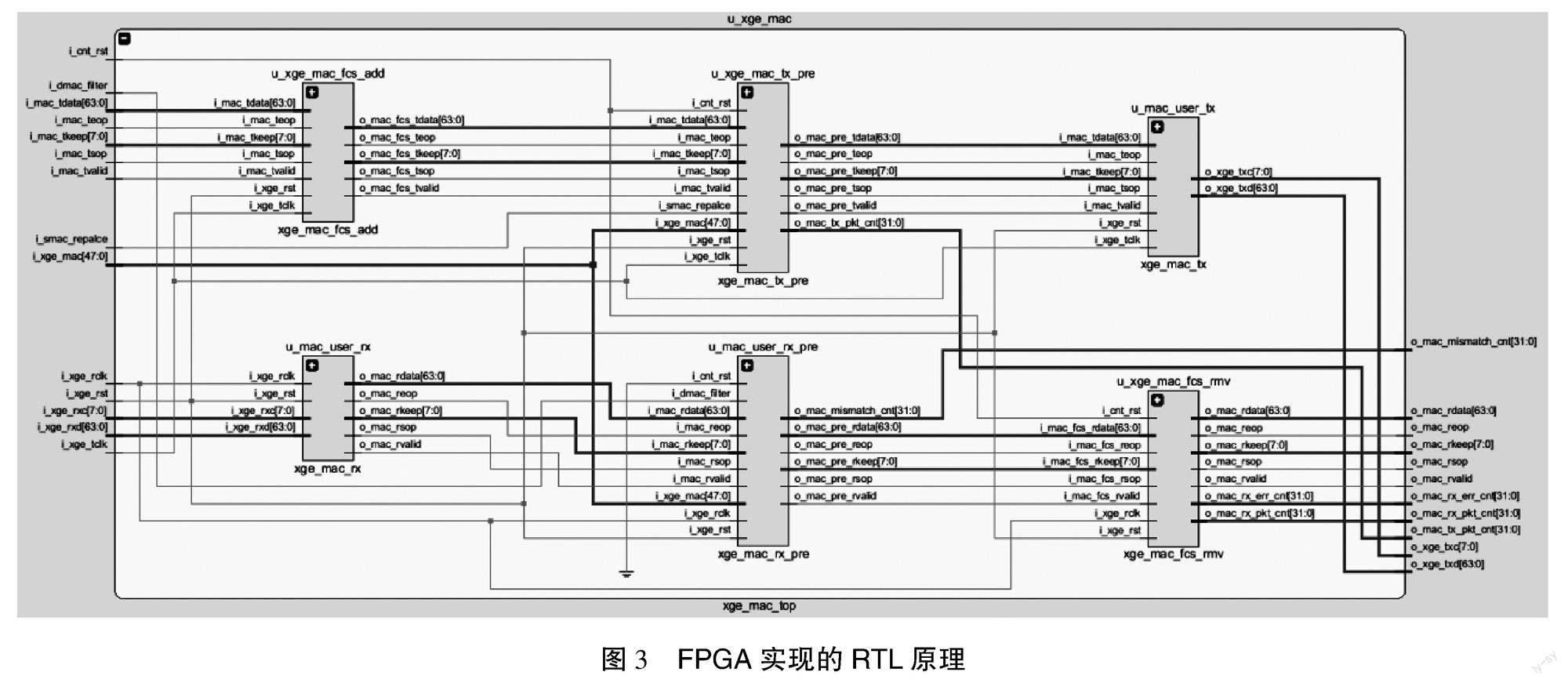

根據(jù)前面分析的系統(tǒng)架構(gòu)和算法設(shè)計(jì),萬兆以太網(wǎng)MAC層FPGA實(shí)現(xiàn)的RTL原理如圖3所示,整個(gè)系統(tǒng)設(shè)計(jì)運(yùn)用自頂向下的設(shè)計(jì)思想。發(fā)送通道主要由u_xge_mac_fcs_add、u_xge_mac_tx_pre和u_mac_user_tx 3個(gè)主模塊組成,3個(gè)主模塊內(nèi)均有是實(shí)現(xiàn)算法設(shè)計(jì)功能要求的相應(yīng)的子模塊。接收通道主要由u_xge_mac_fcs_rmv、u_xge_mac_rx_pre和u_mac_user_rx 3個(gè)主模塊組成。與發(fā)送通道相同,3個(gè)主模塊內(nèi)均有滿足算法設(shè)計(jì)功能要求的相應(yīng)的子模塊。

針對(duì)整個(gè)萬兆以太網(wǎng)系統(tǒng),設(shè)計(jì)測(cè)試模塊進(jìn)行數(shù)據(jù)回環(huán)測(cè)試,測(cè)試系統(tǒng)由數(shù)據(jù)產(chǎn)生模塊、數(shù)據(jù)校驗(yàn)統(tǒng)計(jì)模塊和debug參數(shù)管理控制模塊組成。按照搭建的測(cè)試平臺(tái),利用FPGA內(nèi)部的ILA在線邏輯分析儀對(duì)系統(tǒng)測(cè)試分析,測(cè)試系統(tǒng)RTL如圖4所示。

整個(gè)系統(tǒng)對(duì)相同的一幀數(shù)據(jù)進(jìn)行了10 000次的回環(huán)測(cè)試,錯(cuò)誤統(tǒng)計(jì)結(jié)果為0,由此驗(yàn)證了整個(gè)UDP協(xié)議的MAC層數(shù)據(jù)傳輸?shù)目煽啃裕瑤^處理延時(shí)為91個(gè)時(shí)鐘周期,除去幀頭延時(shí)數(shù)據(jù)發(fā)送延時(shí)為2個(gè)時(shí)鐘周期。根據(jù)試驗(yàn)結(jié)果,應(yīng)用該方法設(shè)計(jì)的萬兆以太網(wǎng)MAC層數(shù)據(jù)傳輸效率顯著提高。

4? 結(jié)語

本文介紹了一種基于FPGA硬件平臺(tái)的萬兆以太網(wǎng)MAC協(xié)議的詳細(xì)設(shè)計(jì)與實(shí)現(xiàn)方案,利用此平臺(tái)完成了萬兆以太網(wǎng)MAC層數(shù)據(jù)的收發(fā)仿真與實(shí)物測(cè)試。該萬兆以太網(wǎng)測(cè)試平臺(tái)主要由光電轉(zhuǎn)換模塊、光纖和FPGA芯片及外圍電路組成硬件框架,利用此硬件架構(gòu),通過數(shù)據(jù)回環(huán)測(cè)試實(shí)現(xiàn)了大帶寬、低延時(shí)和高可靠性的萬兆以太網(wǎng)MAC層的數(shù)據(jù)收發(fā)功能。試驗(yàn)驗(yàn)證表明,該設(shè)計(jì)方案完成了整個(gè)通信流程的數(shù)據(jù)收發(fā),實(shí)現(xiàn)了萬兆以太網(wǎng)UDP協(xié)議數(shù)據(jù)收發(fā)功能,除去協(xié)議開銷,用戶數(shù)據(jù)傳輸速率高達(dá)8.546 Gbps,具有高性能、高可靠性與簡(jiǎn)易性等優(yōu)點(diǎn)。該方案設(shè)計(jì)在有高速率、大帶寬且具有一定定制化要求的高速萬兆以太網(wǎng)協(xié)議通信設(shè)計(jì)應(yīng)用中具有重要參考意義。

參考文獻(xiàn)

[1]敖志剛.萬兆以太網(wǎng)及其實(shí)用技術(shù)[M].北京:電子工業(yè)出版社,2007.

[2]曹政,李磊,陳明宇.萬兆以太網(wǎng)MAC控制器設(shè)計(jì)與實(shí)現(xiàn)[J].小型微型計(jì)算機(jī)系統(tǒng),2007(6):5.

[3]趙柏山,王禹衡,劉佳琪.用于視頻傳輸?shù)?0G網(wǎng)絡(luò)接口設(shè)計(jì)[J].微處理機(jī),2018(3):28-32.

[4]張佳怡.基于10G光通信網(wǎng)絡(luò)加速系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[D].南京:南京理工大學(xué),2020.

[5]王禹衡.基于FPGA的10G以太網(wǎng)UDP/IP處理器視頻傳輸接口設(shè)計(jì)[D].沈陽:沈陽工業(yè)大學(xué),2018.

(編輯? 王永超)

Design and implementation of a 10 Gigabit Ethernet MAC layer based on FPGA

An? Chaoqun1, Li? Fei2

(1.Guangdong Vocational College of Mechanical and Electrical Technology, Guangzhou 510515, China;

2.Guangzhou Haige Communications Industry Group Co., Ltd., Guangzhou 510663, China)

Abstract:? In response to the software based design of the 10 Gigabit Ethernet MAC layer being unable to meet the development requirements of high-speed real-time data transmission, a design and implementation scheme of the 10 Gigabit Ethernet MAC layer protocol based on FPGA hardware platform is proposed. This design scheme mainly uses the parallel processing ability of FPGA to complete the hardware design of real-time data processing of 10 Gigabit Ethernet MAC layer through Verilog hardware description language, and realize the data receiving and transmitting function of 10 Gigabit Ethernet MAC layer with large bandwidth, low delay and high reliability. Experimental verification shows that this design scheme achieves high-speed data transmission over 10 Gigabit Ethernet, excluding protocol overhead. It has the advantages of high performance, high reliability and simplicity.

Key words: 10 Gigabit Ethernet; MAC controller; parallel CRC verification; parallel data processing

- 無線互聯(lián)科技的其它文章

- 基于Java的連鎖餐飲管理系統(tǒng)設(shè)計(jì)

- 基于SpringBoot的高校實(shí)驗(yàn)室管理系統(tǒng)設(shè)計(jì)

- 基于STM32的人體體質(zhì)監(jiān)測(cè)系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

- 基于云計(jì)算的圖書館借閱信息管理系統(tǒng)開發(fā)設(shè)計(jì)

- 基于區(qū)塊鏈的計(jì)算機(jī)網(wǎng)絡(luò)智能穩(wěn)定控制系統(tǒng)設(shè)計(jì)

- 基于微信小程序的農(nóng)產(chǎn)品營(yíng)銷系統(tǒng)設(shè)計(jì)和實(shí)現(xiàn)