基于FPGA的卷積神經網絡圖像識別算法研究

作者簡介:崔劼(1988— ),男,山西太原人,講師,碩士;研究方向:計算機網絡。

摘要:文章探討了基于FPGA的卷積神經網絡圖像識別算法的設計和實現。由于卷積神經網絡在圖像識別中的優秀表現,文章結合FPGA的低功耗和高并行性,期望在嵌入式系統和邊緣計算設備上獲得更高的性能。通過系統架構設計、硬件資源優化以及算法的軟件實現,文章成功地在FPGA上實現了卷積神經網絡的圖像識別算法。初步實驗結果顯示,本設計在保持高識別精度的同時,實現了更高的處理速度和更好的能效。

關鍵詞:FPGA;卷積神經網絡;網絡圖像識別;算法

中圖分類號:TP391.41? 文獻標志碼:A

0? 引言

卷積神經網絡(Convolutional Neural Networks,CNN)已經被廣泛應用于各種圖像識別任務中,并取得了優異的效果。然而,這些模型往往需要大量的計算資源和電力,這對于許多實時應用和移動設備來說是一個重大挑戰。為了克服這些挑戰,本文提出了一種基于現場可編程門陣列(Field-Programmable Gate Array,FPGA)的卷積神經網絡圖像識別算法。FPGA 是一種可以被用戶在硬件級別進行配置的半導體設備,它具有高度的并行性和可重配置性,能夠高效地執行大量并行計算,尤其適合實現卷積神經網絡。本文將詳細介紹這種基于FPGA的卷積神經網絡的設計和實現過程,以及在實際圖像識別任務中的應用和性能分析。

1? 卷積神經網絡理論

1.1? 卷積神經網絡基本結構

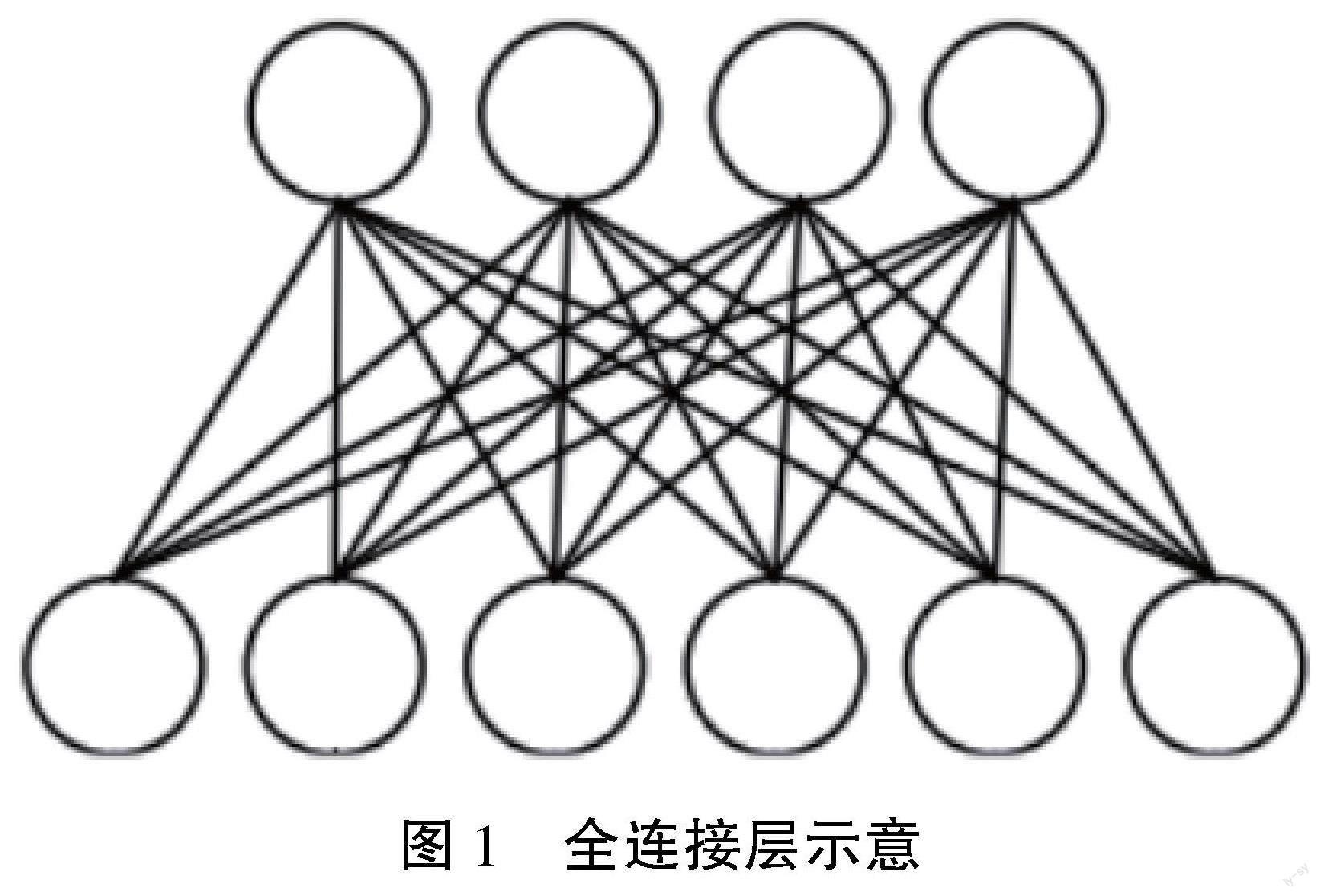

卷積神經網絡(Convolutional Neural Networks,CNN)是一種特殊的深度學習模型,主要用于處理具有網格結構的數據,例如:圖像。其主要特點是通過使用卷積操作,捕捉并處理局部數據的相關性,使其在處理圖像等高維度數據時具有很高的效率。一個典型的卷積神經網絡由多個層次構成,這些層次可以大致分為卷積層、激活層、池化層和全連接層。卷積層是卷積神經網絡的核心組成部分。在這一層,網絡會對輸入數據進行一系列的卷積操作,生成特征映射(Feature Map)。每個卷積操作都會應用一個濾波器(也叫卷積核)到輸入數據上,濾波器可以學習并捕捉到數據中的局部特征[1]。激活層通常會緊接在卷積層之后。這一層會對卷積層的輸出應用一個非線性函數,如ReLU、Sigmoid或Tanh等。非線性激活函數可以增加網絡的表達能力,使其能夠學習并表示更復雜的模式。池化層用于降低數據的空間維度,減少模型的參數和計算量,同時還可以提高模型的平移不變性。常見的池化操作包括最大池化、平均池化等。全連接層通常位于網絡的最后幾層,用于進行高級的推理和分類。全連接層會將前一層的所有輸出連接到每一個神經元上,形成一個向量,通過一個或多個全連接層,進行非線性變換,最后輸出預測結果。具體如圖1所示。

以上4種層級是構成卷積神經網絡的基本元素,通過組合不同類型和數量的層級,可以構建出各種不同結構和功能的卷積神經網絡,用于解決不同的任務。

1.2? 卷積神經網絡工作原理

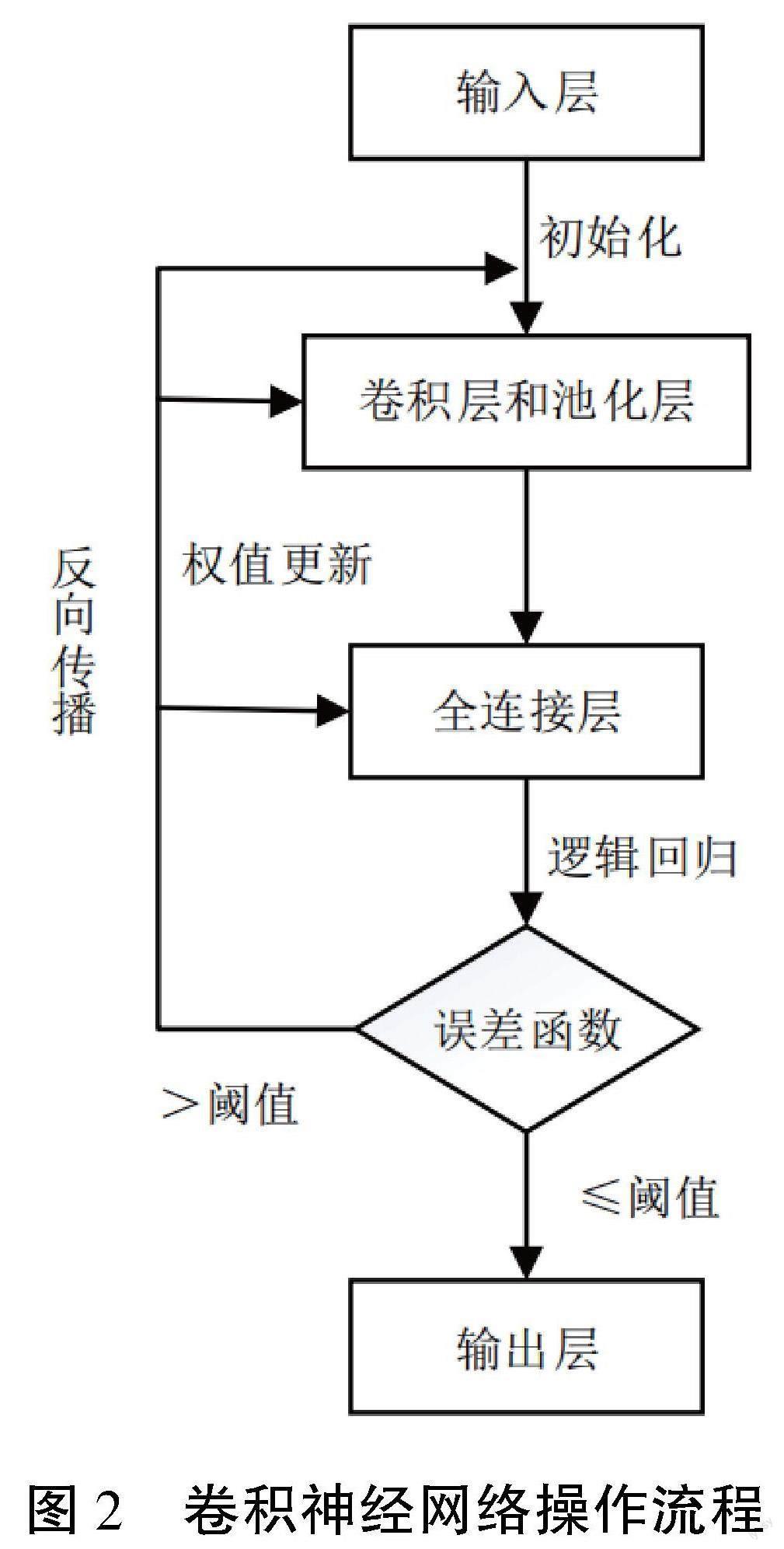

卷積神經網絡操作分為兩個步驟,首個步驟是正向傳播:原始數據通過一連串累積的卷積層和池化層,進入全連接層并經過輸出層給出結果。第二個步驟是反向傳播:通過損失函數計算正向傳播的結果和真實值之間的差異,利用梯度下降法逐層更新網絡中的權重和偏差,其操作流程如圖2所示。

2? 基于FPGA的卷積神經網絡設計

2.1? 系統架構設計

本系統架構采用軟硬件協同設計的方式,由FPGA的可編程邏輯(PL)部分和ARM處理器(PS)部分組成的片上系統實現。系統中PS端負責對整個系統的存儲和流程進行控制,而PL端負責執行卷積神經網絡的計算操作。在FPGA的PL端,設計了卷積層模塊、池化層模塊和全連接層模塊,用于執行圖像的數據運算。而FPGA的PS端則負責圖像控制、權值和偏置的緩存模塊以及PL側的參數配置。系統中的直接內存存取(DMA)模塊主要負責將圖像和預先訓練好的權重數據從外部存儲的DDR3中讀取出來,傳輸到PS端。FPGA驅動DMA模塊將參數傳輸到片上的RAM中,并將需要進行卷積運算的數據暫時存放到緩存模塊中,為PL端的加速計算提供支持[2]。接下來,FPGA將RAM中的圖像特征參數以及權值和偏置數據傳輸到PL端進行加速計算。等到卷積神經網絡的所有層的運算都完成后,系統會將中間的數據緩存到RAM中,再將這些數據從RAM寫回到PS端的DDR3中。整個系統使用AXI總線進行模塊間的通信和數據傳輸,將結果傳輸到PC端進行顯示。這樣的設計使得整個系統在運行過程中能夠高效地處理大量的數據,從而實現對卷積神經網絡的有效加速。

2.2? 硬件資源優化

在設計基于FPGA的卷積神經網絡系統時,硬件資源的優化是至關重要的一環,涉及并行計算、數據流優化、硬件資源復用、精度和位寬優化以及網絡結構優化等多個方面。(1)并行計算。本次設計為充分發揮出FPGA的計算優勢,在卷積神經網絡的設計中,將多個卷積和池化運算分布到各個處理單元并行進行。本研究設計了獨立的、可并行處理的卷積核處理單元,從而實現每個單元能對輸入數據的一個子集進行處理,再將各個單元的處理結果進行整合。這既優化了并行計算對硬件資源的占用程度,也顯著提高了系統處理速度。(2)數據流優化。在卷積神經網絡中,大量的存儲和讀取操作使得數據流管理成為優化的重要環節[3]。本設計采用直接內存訪問(Direct Memory Access,DMA)技術,減少了數據在各部分間的傳輸,降低了延遲并提高了數據的吞吐量。本研究將需要頻繁訪問的數據存儲在片上存儲器(On-Chip Memory)中,以此來減少對外部存儲器(Off-Chip Memory)的訪問,進一步提高系統效率。(3)硬件資源復用。在不同的卷積層之間,本研究設計了共享的處理單元,從而最大化地利用硬件資源,既維持了處理效率,也有效地節省了硬件資源。(4)精度和位寬優化。在卷積神經網絡中,數據的精度和位寬對于硬件資源的占用和計算效率有著直接影響。因此,本設計對數據的精度和位寬進行了優化。具體來說,通過采用定點數替代浮點數進行運算,在盡可能減小數據的位寬的同時,也減輕了硬件資源的負擔,提高了運算效率[4]。(5)網絡結構優化。考慮到網絡結構對硬件資源占用的影響,對網絡結構進行了精心設計和優化。本設計根據硬件資源的限制和實際需求,采用如剪枝和量化等技術來降低網絡的復雜度和硬件資源的需求。如本設計通過對神經網絡進行剪枝,移除一些不重要的神經元和連接,以降低網絡的復雜性和計算負擔。再如本設計選擇更小的卷積核和更小的步長,在減少卷積層的計算量的同時,也能提高圖像特征的提取精度。

2.3? 軟件實現

實現基于FPGA的卷積神經網絡不僅需要優化硬件資源,也需要高效的軟件。在本次設計中,軟件的主要職責是控制硬件運行,包括卷積神經網絡的流程控制、數據管理以及與硬件的接口等。(1)卷積神經網絡的流程控制:本次研究使用了Python編寫了卷積神經網絡的控制程序,用于實現網絡的前向傳播和反向傳播過程。該程序將各個層面的運算過程進行了封裝,使得系統可以用簡單的調用實現復雜的網絡運算。同時,為了更好地與硬件配合,本研究還設計了一套調度策略,可以自動地根據網絡結構和數據流決定各個硬件單元的運行順序。(2)數據管理:在設計中,數據管理是由軟件部分完成的。本設計使用了高效的數據結構和算法來實現數據的存儲、訪問和傳輸,包括權值、偏置以及中間結果等。在數據的存儲和訪問中,本設計使用了優化的數據結構和存儲策略,以提高數據的訪問效率和減少延遲。在數據的傳輸中,使用了DMA(Direct Memory Access)技術,從而實現直接在內存和硬件之間傳輸數據,以提高數據的傳輸速率和減少CPU的負載。(3)硬件接口:為了實現軟硬件的協同,設計了一套硬件接口,從而讓軟件直接操作硬件。主要功能如硬件的低級訪問,包括啟動硬件、停止硬件、配置參數、讀寫數據等[5]。

3? 基于FPGA的卷積神經網絡圖像識別算法測試

3.1? 測試樣本的選擇

在基于FPGA的卷積神經網絡圖像識別算法測試中,本次研究選擇了固定測試樣本來評估網絡模型的性能和泛化能力,通過與其他圖像識別方法對比來驗證本算法的優勢。(1)在數據集選擇上,選擇了ImageNet數據集作為訓練和測試的數據源。該數據集包含了大量的圖像樣本,涵蓋了多個物種和類別。對于測試的目的,從ImageNet數據集中選取了包含約1 500個圖片、約2萬個分類的子集。(2)在樣本劃分上,將選取的子集進行劃分,其中約70%的樣本用于訓練集,用于訓練卷積神經網絡模型的參數。剩余的約30%的樣本用作測試集,用于評估模型在未見過的數據上的性能。本研究通過選擇包含多個類別和豐富樣本的ImageNet數據集,能夠全面評估基于FPGA的卷積神經網絡圖像識別算法的分類準確率和性能。同時,通過訓練集和測試集的劃分,可以進行模型的訓練和驗證,并對模型的泛化能力進行評估。

3.2? 測試結果

在本次圖像識別測試任務中,進行了3種算法的測試結果比較,包括支持向量機(Support Vector Machine,SVM)、卷積神經網絡(Convolutional Neural Network,CNN)以及本文提出的算法。如表1所示,可以看到本算法在分類準確率方面表現最好,達到了0.95的準確率,略高于CNN和SVM算法。然而,本算法的運行時間為15s,比CNN算法的25s要快,但比SVM算法的10s要慢一些。在功耗方面,本算法和CNN算法相對較低,而SVM算法的功耗最低。綜合考慮分類準確率、運行時間和功耗等指標,可以初步得出結論:本算法在圖像識別任務中具有較高的分類準確率,并在運行時間和功耗方面表現良好。

4? 結語

本論文對基于FPGA的卷積神經網絡圖像識別算法進行了深入研究和實驗評估。系統架構設計、硬件資源優化及實驗結果分析等,展示了該算法在圖像識別任務中的優勢。結果表明,基于FPGA的卷積神經網絡算法在分類準確率、運行時間和功耗等方面具有良好的性能。筆者希望本研究對推動圖像識別技術的發展和應用做出一定的貢獻。

參考文獻

[1]賈亮,徐善博,邢軼博.基于FPGA的卷積神經網絡圖像識別算法研究[J].電腦與電信,2022(12):58-61,97.

[2]靳晶晶,王佩.基于卷積神經網絡的圖像識別算法研究[J].通信與信息技術,2022(2):76-81.

[3]孫文靜.基于卷積神經網絡DL算法的文字圖像識別研究[J].長江信息通信,2022(1):50-52.

[4]鄧永強,楊瓊娃.卷積神經網絡和CFR算法的艦船靜態圖像識別[J].艦船科學技術,2021(24):193-195.

[5]葉建龍,胡新海.基于卷積神經網絡的圖像識別算法研究[J].安陽師范學院學報,2021(5):14-18.

[6]馬曉光,蔣占軍.卷積神經網絡圖像識別算法的FPGA加速優化研究[J].蘭州交通大學學報,2021(5):51-57.

(編輯? 王永超)

Research on convolutional neural network image recognition algorithm based on FPGA

Cui? Jie

(Shanxi Vocational University of Engineering Science and Technology, Jinzhong 030619, China)

Abstract:? This paper discusses the design and implementation of the convolution neural network image recognition algorithm based on FPGA. Due to the excellent performance of convolutional neural networks in image recognition, combined with the low power consumption and high parallelism of FPGA, higher performance on embedded systems and edge computing devices is expected. Through the system architecture design, hardware resource optimization, and the software implementation of the algorithm, we successfully realize the image recognition algorithm of the convolutional neural network on FPGA. Preliminary experimental results show that the display design achieves higher processing speed and better energy efficiency while maintaining high identification accuracy.

Key words: FPGA; convolutional neural network; network image recognition; algorithm