基于分立器件并聯的高功率密度碳化硅電機控制器研究

張少昆 孫 微 范 濤 溫旭輝 張 棟

基于分立器件并聯的高功率密度碳化硅電機控制器研究

張少昆1,2孫 微1,2范 濤1,2溫旭輝1,2張 棟1,2

(1. 中國科學院電工研究所 北京 100190 2. 中國科學院電力電子與電氣驅動重點實驗室 北京 100190)

新能源車用的電機控制器通常通過大功率模塊來完成,但大功率模塊一般成本比較高,體積比較大,資源也有限。該文基于SiC MOSFET分立器件并聯設計了一種高功率密度電機控制器,為了從電氣和散熱角度最大程度地提升材料和空間利用率,實現高功率密度以及分立器件的良好動靜態均流,設計了一種新型的電子系統結構,并提出了一種能動態平衡并聯MOSFET電流的高抗擾驅動電路以及可實現低寄生電感、大電流以及高散熱的適合分立器件并聯應用的新型印制電路板(PCB)疊層母排設計方法。提出的電路及方法既有利于實現并聯器件的動靜態均流,又可以減小寄生電感造成的影響,還可以有效抑制負向串擾電壓。對基于上述研究成果開發出的碳化硅電機控制器,經過雙脈沖及功率實驗,結果表明,設計的分立器件并聯控制器并聯均流效果好、散熱好、功率密度高,在風冷的條件下,實現了效率最高為99.5%,功率密度為60 kW/L,可應用到新能源整車系統中。

SiC MOSFET 分立器件并聯 高功率密度 印制電路板(PCB)疊層母排

0 引言

近年來,碳化硅(Silicon Carbide, SiC)作為一種優良的新型器件,已經被大量地應用到電動汽車、航空航天、新能源等領域[1-4]。它的出現不僅顯著地改善了整個系統的性能,而且還顯著地減少了變換器的制造、裝配以及后面出現的維修等問題。隨著功率密度的提升,SiC MOSFET的優勢日益凸現,可以大大減少電力電子設備的體積,并能夠極大地改善電氣性能,提升電氣系統的運行效率[2-4]。SiC MOSFET相比于傳統的功率器件Si IGBT,擊穿與阻斷電壓高、開關速度快、耐溫能力強,而且,關斷過程沒有拖尾電流,能夠大大減少開關損耗[4-5],極大地加快其運行,從而為電氣控制領域帶來了新的發展方向。隨著技術的進步,SiC MOSFET已經可以滿足電氣傳動、新能源等高效的電氣傳輸需求,它的通流能力也可以達到幾十安培,因此,其已經被認定為未來的最佳電氣傳輸設備。“定制化”的功能模塊的銷售數量有限,而且封裝方式存在差異,銷售渠道也相對比較單一。此外,SiC模塊的售價過高,這阻礙了開發更加經濟實惠的電力驅動系統。與傳統的功率模塊不同,分離器件的制造技術更加先進,其制造精度更高,而且生產效果更好,這使得它們在單位時間內的制造費用要低得多[6]。另外,采用分離器件的并聯技術,不僅可以靈活增加或減少器件的數量,還可以根據需要調整器件的參數,從而提供更加靈活的功率拓撲[7-9]。

但是,并聯電路回路中寄生參數比較復雜,分布難免出現不對等的現象。SiC MOSFET的開關速度較高,因而極易在開關過程中電壓與電流產生振蕩比較嚴重的現象,而相比于IGBT來說,會給系統帶來更嚴重的電流負載不均衡問題[10-11]。當輸出負載不均衡時,將會形成各種損耗、應力和短路問題,不僅會嚴重干擾系統的正常工作,還可能會增加系統故障的風險,因此縮短了其實際使用期 限[12-13]。為了解決這一問題,學術界開始關注器件本身的情況,并探討了器件的導流能力、閾值電壓以及其他因素等對元件的動、靜態電流均衡的影響。另外,器件的封裝管腳除了可能會導致漏極、共源極等附加更多的寄生電感外,也會使并聯器件的電流的分布狀況受到影響[14-15]。文獻[16]對器件特性參數是否影響SiC MOSFET的靜動態均流進行了相關研究,并指出耦合電容對SiC MOSFET器件的并聯靜動態均流影響比較小,尤其是在器件間耦合電容差異不大的情況下,影響更小[16]。文獻[17]經過研究也指出,寄生電容的分散性對并聯電流分配幾乎沒有影響。在目前的大多數文獻中,針對器件并聯后可能出現的動靜態電流不均衡的問題,通常會考慮優化印制(Printed Circuit Board, PCB)布局的方法,降低并聯回路寄生電感[18],進而可以有效減小回路雜感不同帶來的開關過程中的電壓及電流不均衡的問題。但是,采用已有的方法,如靠布局優化,不能完全解決電流不均衡問題,有時還會加重原來的不均衡現象[19-21]。文獻[19]使用了一種耦合電感,以控制并聯器件間的不平衡電流。文獻[20]基于對源極電感進行補償,以降低不同并聯回路間的寄生參數的差異,改善均流性能。文獻[21]通過控制MOSFET管的開通與關斷時刻,采用主動補償的方法來改善并聯管的均流性能。但是,以上方法均需要額外增加一些部件,增大了系統復雜度的同時,降低了系統的可靠性,而且不能進行大規模的推廣使用。

另外,在中大功率SiC逆變器中,疊層母排設計也被廣泛應用,其架構可以將母線電容和功率器件緊密相聯,從而實現了逆變器的高性能運行。目前,關于SiC功率模塊的疊層母排如何進行結構設計見文獻[22-24]。文獻[22]提出一種新型的疊層母排的設計方法,采用了雙層疊層,大大減小了整個系統母排的雜感。文獻[23]對一款全SiC功率器件的母排架構進行了多方面優化,以得到更小的寄生電感值。文獻[24]則研究了根據不同結構布置的電感元件對變流器特性的影響,并提出了一種更有利于抑制沖擊電流的母排設計的結構布置方法。然而,適用于分立SiC MOSFET器件并聯的疊層母排的設計方法,還沒有詳細的文獻研究。基于分立器件并聯的疊層母排的設計,除了考慮降低回路的雜感以外,各并聯回路之間的阻抗對稱也是需要重點考慮的要素。這是因為疊層母排如果結構不對稱,必然會帶來寄生阻抗的不對稱,進而使并聯器件之間電流不均衡[19]。不均衡的電流會出現各種損耗、應力以及短路問題,迫使整個系統降額運行。

綜上所述,分立式的SiC MOSFET器件并聯設計需要克服的主要問題為大功率元件并聯均流、低雜感的疊層母排設計、大輸出電流的負載及大功率的散熱問題等。本文采用SiC MOSFET分立元件設計完成了一種高功率密度電機控制器,并克服了這些主要難題,設計出了一個全新的高集成度電子系統結構,不但可以減少強弱電干擾,還可以做到并聯連接功率回路和控制回路的對稱布局,便于均流。為了進一步實現并聯器件良好的工作,還設計了一種能動態平衡并聯MOSFET電流的高抗擾驅動電路,不僅有利于實現并聯器件的動靜態均流,減小寄生電感造成的影響,還可以有效抑制負向串擾電壓。圍繞低寄生電感、大電流以及高散熱等目標,設計了一種新型的適合分立器件并聯應用的PCB疊層母排,并通過仿真以及實驗驗證了所提設計方法的有效性。基于上述研究成果,開發出基于分立器件并聯的碳化硅電機控制器,并聯均流效果好、散熱好、結構緊湊、功率密度高、成本低,可用于新能源整車系統中。

1 分立器件并聯高功率密度SiC控制器設計

1.1 控制器電氣架構設計

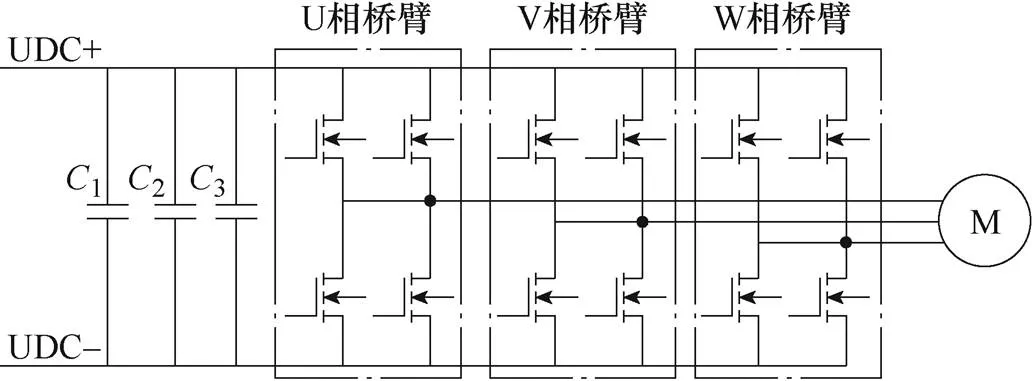

該系統選擇了SiC MOSFET雙管并聯的方法,主回路原理如圖1所示。采用的是常用的三相全橋的電路結構拓撲,為了擴大通流能力,6路開關管均采用了SiC MOSFET管并聯的形式,并聯的管子數量為2,封裝為TO247-4。整個系統共采用了12只SiC MOSFET管。母線電壓正極UDC+與母線電壓負極UDC-所在回路上并聯了3個小體積的薄膜電容1、2與3,以利于實現高功率密度。

圖1 控制器主回路原理

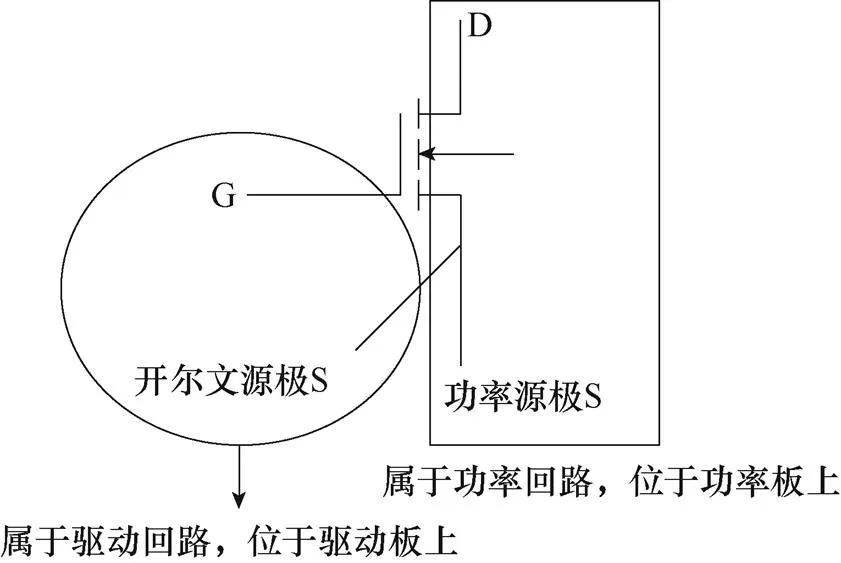

設計的控制器電子系統包括控制模塊、驅動模塊及功率模塊三部分。為了實現最小的電流回路,并減小功率回路與驅動回路之間的相互干擾,主功率板和驅動電路板分別用兩個PCB實現,SiC MOSFET的開爾文引腳在電流方面將功率回路與驅動回路分開,門極G與開爾文源極S1管腳焊接在驅動板上,功率源極S2與漏極VD管腳焊接在功率板上,除了有助于防止高壓側瞬變信號對柵極電壓的反饋帶來的干擾,降低動態損耗,還有利于實現并聯SiC MOSFET管功率回路到驅動回路的對稱布局。控制電路板、驅動電路板以及功率電路板均為圓形,并且是上下三層的結構,主控板的直徑只有72 mm,驅動板、功率板直徑均為88 mm,板子形狀為圓形,有利于分立器件的對稱布局,遵循最簡單的物理對稱原則,進一步有利于均流。在功率回路設計上,為了減小功率回路的耦合電容與雜散電感,并實現并聯器件對稱的功率回路,采用了多疊層的圓形PCB結構來實現低感疊層母排。控制器電子系統結構如圖2所示,設計的電子系統結構布局,不僅可以減小電機控制器的整體體積,進而增強控制器的集成度以及功率密度,還可以達到節省成本的目的。

圖2 控制器電子系統結構

為了從電氣和散熱角度最大程度地提升材料和空間利用率,整個系統實現了功率模塊、驅動電路、電容與母排的協同設計。直流側支撐電容采用多只并聯形式,焊接在功率板上,通過覆銅層連接到各個并聯功率模塊的相應管腳上,以減小等效電感和等效電阻;功率板與電機三相交流輸出端采用銅柱連接,實現電氣和機械結構復用,同時起到支撐電路板的作用;為了節省空間,采用了PCB級電流傳感器,且傳感器位于功率板上;功率模塊均勻布置于圓筒形鋁殼內壁加工出的凸臺上,通過螺釘與安裝面固定并進行散熱。最終設計的分立器件的高功率密度控制器的電氣結構布局如圖3所示。控制電路板、驅動電路板和功率電路板均設置為了圓形,控制板的直徑只有72 mm,驅動板與功率板直徑相同,均為88 mm,高功率密度的電路板增強了整個電子系統的集成度,最終提升了控制器的效率。

圖3 控制器電氣結構布局

1.2 關鍵功率單元設計

1.2.1 模塊選型設計

當使用電力電子設備進行功率管模塊的選型時,首先要確定其能夠承受的最高電流,并且要綜合分析其所處的環境條件,如超負荷、電壓變化、開關故障、溫差變化以及其他可能影響使用壽命的因素,以確定合適的功率管。在進行器件的選型時,必須考慮到各種使用場景,并且要求其能夠承受足夠的能量消耗。因此,需進行熱阻核算,必須確保其最高結溫低于預設的標準,這樣可選擇較小的功率管模塊來通過更大的電流,更加有效地利用功率管。

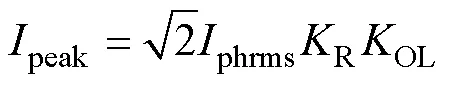

功率開關器件的電流為

分立器件并聯的系統控制器的大功率開關管通常是由幾個分立的開關管并聯而得到的,但按照整個系統的電壓等級和一個分立元件的電壓級別,可選擇由2~6個甚至更多個分立元件并聯。基于控制器的功率以及體積,本文采用了兩個分立的SiC MOSFET管并聯的方案,因單只峰值功率應大于61 A,選用了CREE的1 200 V/115 A的TO247-4封裝的SiC MOSFET 模塊,整個功率單元的三相橋臂共采用了12只。

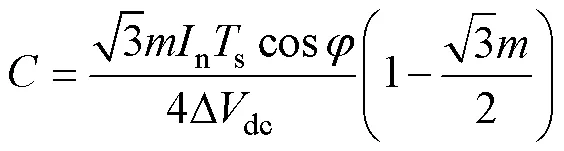

1.2.2 直流側支撐電容設計

直流側電容在控制器的設計過程中一直承擔著很重要的角色,為感性負載供給無功功率,以及保證直流電壓平穩的關鍵作用。同時,直流側電容器也是車用電源驅動系統中非常重要的無源器件,是影響車輛驅動功率密度、穩定性及效率的關鍵部件之一。

在新能源汽車使用中,驅動的直流電源大部分由蓄電池組件供給,在此前提下,直流側電容器組件主要起著與無功功率補償和解耦的功能,以便保證驅動輸入端直流電壓穩定,而且不受負載影響。蓄電池組輸出的電壓理想狀態下是近乎于平滑直流,而直流側電容的電流則是脈動電流,也就是直流側電容器需要吸收由功率開關管不停開關而產生的脈動電流,因此平穩的輸出電壓也可以增加蓄電池組件的使用壽命。

1.3 驅動單元設計

1.3.1 驅動電源設計

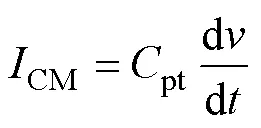

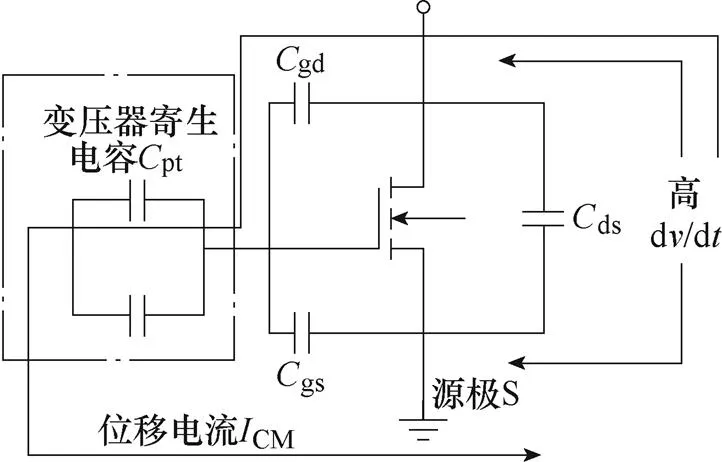

圖4 高低壓側共模電流耦合示意圖

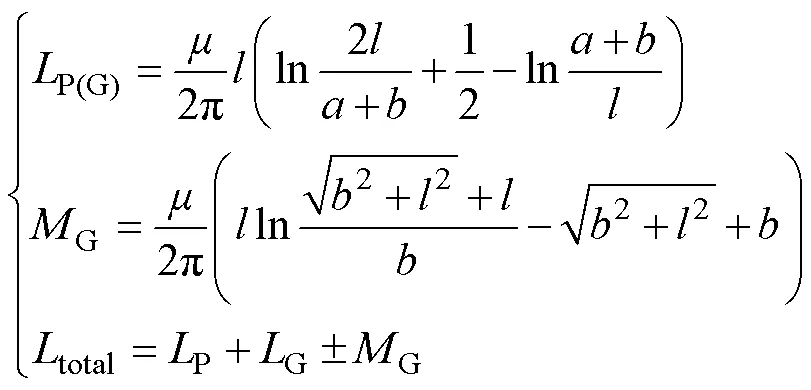

驅動電源采用了一種極其緊湊的反激拓撲結構,最大輸出功率可達到4 W,原理框圖如圖5所示,隔離變壓器采用低耦合電容設計,繞組間電容只有7 pF,有助于實現高的共模瞬態抗擾度,從而適應SiC MOSFET的快速開關。此外,變壓器二次側采用了隔離反激式轉換器2,型號為LT8302,可以通過直接在一次側回掃波形來采樣隔離側的輸出電壓,無需第三繞組或反饋光隔離器件進行調節,可輸出+15 V和-4 V的兩個隔離電源,為了滿足不同的SiC MOSFET芯片的需求,變壓器負壓輸出后端還安裝了電壓調節芯片3,型號為LM337,它可以通過調節電阻1和2的阻值來實現不同的負壓輸出,負電壓EE為

可調節的負壓可以適應不同類型的SiC MOSFET模塊的需求,也有利于防止橋臂之間的管子在相互開通時給對管帶來的直通風險。

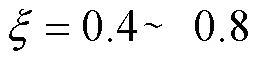

1.3.2 并聯驅動電路設計

并聯驅動電路原理框圖如圖6所示。為了實現并聯均流,兩并聯的SiC MOSFET管共用一個驅動芯片和推挽放大電路,除了共用一個門極驅動電阻0以外,每個SiC MOSFET管還有各自獨立的開通電阻g1(g3)與關斷電阻g2(g4),使每個SiC MOSFET管的門極電壓可以獨立地開通與關斷,保證了在每個SiC MOSFET管的門極閾值電壓有差異的情況下也可實現同時開關。

圖6 并聯驅動電路原理框圖

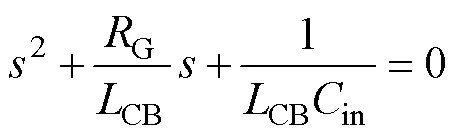

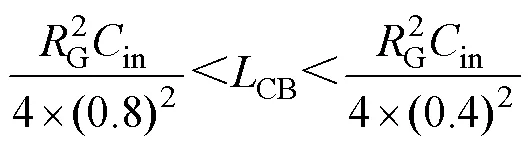

兼顧面積、功率、散熱等因素,選擇了采用磁性元件平衡回路阻抗特性的方法,保證并聯等效阻抗相同。因此,在并聯SiC MOSFET管的開通電阻與關斷電阻的后面分別串聯了一個鐵氧體磁珠g1與g3,同時也可以抑制SiC MOSFET柵極回路中快速開關引起的振鈴。磁珠特有的高頻電阻和低頻感抗特性,可以很好地捕捉和消除高頻噪聲,但其存在的微小電感量對脈沖前沿有一定的影響。阻抗值大的鐵氧體磁珠對信號的高次諧波抑制作用好,但對脈沖信號的上升沿延遲卻較大。為了實現脈沖上升沿延遲小并且高頻抑制作用強,可按電感的暫態特性來計算選擇所需磁珠的阻抗值,這里以MLCB2B3216系列磁珠為例,給出磁珠阻抗選取的理論依據,實際取值可根據實驗結果微調。

磁珠的阻抗由100 MHz時的阻抗確定,因此阻抗值與電感量關系滿足

由此可得

圖7 鐵氧體磁珠頻率與阻抗曲線

圖8 串擾抑制原理

每個SiC MOSFET管的門極GS上均加了一個電阻與二極管的串聯電路,分別為圖6中的1與VD2、2與VD4的組合,該電路是為了增加驅動門極的抗干擾能力。

1.3.3 并聯驅動電路PCB設計

為了減小門極驅動環與功率環之間的耦合與影響,將門極回路與功率回路分別放在了不同的PCB上。PCB設計結構原理如圖9所示,SiC MOSFET的門極G與開爾文源極S焊接在驅動板上,漏極D與功率源極S通過驅動板上的無電氣連接的通孔單獨焊接到下層的功率板上。

圖9 PCB設計結構原理

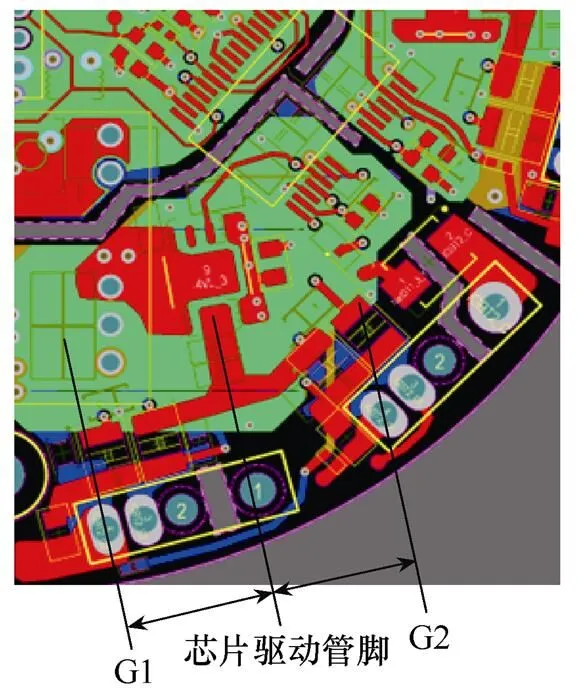

除了在電路上采取均流的措施外,驅動回路布局上也采用了物理上減小并聯雜感的方法,最終的驅動板PCB布局如圖10所示,12個MOSFET管均勻地分布于圓形的驅動板上,兩個并聯的MOSFET管在布局時均滿足從每個管的柵極到驅動器(驅動芯片加推挽芯片)的輸出以及從柵極返回到驅動器的路徑嚴格做到對稱,并且驅動器應放置位于兩個并聯MOSFET管的柵極引腳中心,如圖11所示,而不是放在兩個并聯MOSFET的物理位置的中間。此外,門驅動器距離兩個并聯MOSFET管的距離越近越好,以減小門極驅動回路上的電感。

圖10 驅動板PCB布局

圖11 并聯驅動PCB設計要點

1.4 PCB母排設計

1.4.1 母排結構設計

為了實現控制器的高功率密度,PCB母排上實現了并聯MOSFET管、電流傳感器、放電電阻、直流電容以及交直流端子的一體化設計。不同PCB母排形狀、器件連接方式以及電容布局的差異性,均會產生不同的疊層母排結構。圖12為設計的新型PCB母排結構示意圖,真正實現了小型化、高功率密度與布局對稱。

圖12 PCB母排結構

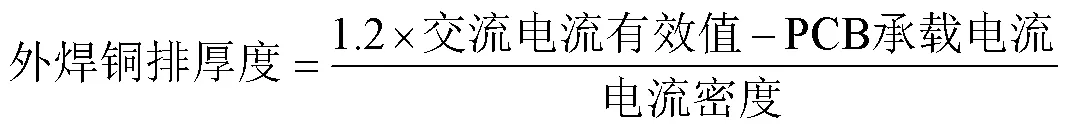

該設計從減小母排總自感、增大母排總互感,具有最大功率密度及物理均流特性的角度出發,實現了一種新型的PCB疊層母排結構。PCB母排形狀為直徑8 cm的圓形,極小的尺寸有利于減小母排的自感,圓形的布局可以更好地保證元器件的對稱性,有利于均流。PCB母排由垂直多回路的多組PCB疊層組成,單組疊層由母線正與母線負組成,該結構有利于增大互感,減小雜感。母排的頂層和底層均具有直流和交流走線的金屬開窗,如圖13所示。可以焊接不同厚度的不規則形狀的金屬片或金屬條,既起到擴流、滿足承載最大電流的同時,又可以達到良好的散熱效果。外焊銅片的厚度需要根據母排承載的電流進行計算,為了留有裕度,母排最終承載電流按實際需要電流的1.2倍進行計算,外焊銅排的厚度(mm)計算公式如式(11)所示。其中銅厚1盎司,寬度1 mm可以走1 A的電流,也就是電流密度為7 A/mm2。

圖13 PCB母排實物

Fig.13 The physical diagram of PCB busbar

功率回路上的12個功率開關器件,均勻排布在圓形母排的周邊上,構成了三相全橋結構。將PCB母排形狀做成圓形,不僅可以更好地保證元器件的對稱性,保障均流效果,在承載盡可能大電流的前提下,功率密度也可以做到最高,同時這種緊湊型的設計也節約了原材料成本。此外,為了節約控制器的空間,采用了兩路PCB級電流傳感器,傳感器的輸入與電機交流點相連,輸出與上下并聯管的中點相連。3個交流連接點處可以外焊銅柱直接與電機相連,實現可靠連接。直流電容位于PCB母排的中間位置,與每組單相橋的功率開關器件并聯。

為了確保電路的穩定運行,在每個直流電容的正負極之間都安裝了放電電阻,這樣即使在電源變化的情況下,電容也能夠保持充放電狀態。

1.4.2 母排低雜感設計

在新能源驅動器中,因為功率回路上寄生電感的影響,導致功率元件在關斷后形成超過耐壓范圍的暫態尖峰,從而致使功率元件擊穿損壞[26]。通過對功率回路中寄生電感的構成分析,SiC MOSFET功率模塊內寄生電感和直流支撐電容等效寄生電感在出廠時就固定不變,唯一可進行設計控制的就是直流母排的電感。

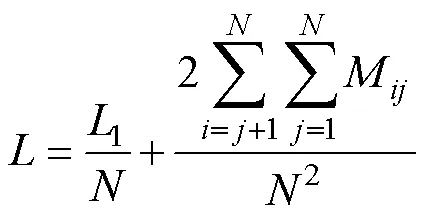

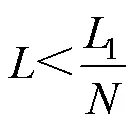

一個最基本的疊層母排結構由導體層(正極層、負極層)和中間的絕緣層組成,電流從正極層流入,從負極層流出。對于單個電流回路,能量存儲在空間中的磁場中,環路電感可以根據存儲的磁能來確定,其計算公式為

圖14 并聯電流等效電路

Fig.14 The parallel current equivalent circuit

總回路電感可表示為

根據式(14)可以看出,減小回路互感可以減小回路總磁能,進而減小總回路電感。

如果并聯電流回路阻抗相同,各個回路的自感也相同,那么每個回路電流大致相等,即

根據式(15)可以將式(14)化簡為

當相鄰回路的電流方向相反時,互感為負值,有

式中,1為單個電流回路上的電感。

因此,并聯電流回路上的電感可以通過減小互感來減小總回路上的電感,當并聯回路相鄰回路電流方向相反時,電感會隨著回路數的增多而降低。

由式(18)可知,疊層母排的總雜散電感不僅取決于導體層的自身特性,也受到導體層與其他層之間的互感影響。減小母排的長度以及正負極之間的距離,可以增大互感,減小總阻抗。通過分析可發現,當PCB相鄰層之間的電流方向是相反的,而且它們之間的距離也比較近,能夠顯著減少由于層之間的電磁感應而造成的電感值。

基于以上原理,利用垂直方向上方向相反的電流在最小的環路面積上有最小的寄生電感的原理,設計的PCB母排直徑只有8 cm,在板子厚度只有2 mm的情況下,單層銅厚可做到4盎司、層數為8的最大通流能力設計。低感疊層母排結構示意圖如圖15所示,板子共有4組PCB疊層,每組PCB疊層均由正母線層與負母線層組成,每組PCB疊層形成一個回路,且正母線層和負母線層中流過的電流大小相等、方向相反。四回路的PCB疊層,又可以進一步降低母排回路的雜散電感,避免功率開關器件在高速開關的過程中承受較大的電壓過沖,從而降低功率損耗,提升系統效率。

圖15 低感疊層母排結構示意圖

1.4.3 低感疊層母排電感測試

圖16 雙脈沖功率回路電感

Fig.16 The inductance diagram of dual pulse circuit

圖17 回路雙脈沖測試波形

表1 回路各部分電感

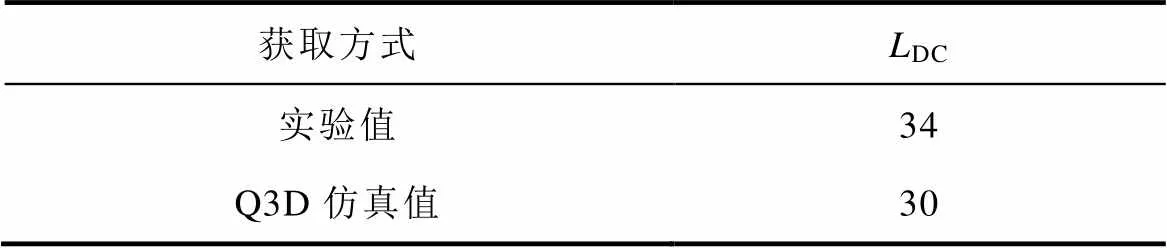

為了驗證實驗測量PCB母排雜散電感的正確性,通過Ansys Q3D對疊層母排進行了仿真。PCB母排在Q3D中的仿真電流分布如圖18所示。仿真中,使用10 MHz的交流電源進行分析,最終獲得的主回路總寄生電感值為30 nH。通過表2里的數據對比,可以發現兩種不同的提取方式產生的母排的電感值存在一定的偏差,但在誤差范圍內。

圖18 Q3D 母排仿真電流分布

表2 仿真與實驗雜感對比

1.5 散熱設計

1.5.1 損耗計算

SiC MOSFET功率器件在工作過程中產生的功率損耗占功率回路總損耗的主要部分,因此,為了有效地降低損耗,必須采用有效的散熱技術,并且通過精確的數值計算,來確定最佳的散熱方案,才能有助于降低損耗,確保控制系統的正常運轉。SiC功率器件在電機控制器功率回路中的損耗主要分為開關損耗與靜態損耗,其中開關損耗分為開通損耗與關斷損耗,靜態損耗分為導通損耗與截止損耗。

控制器采用TO247封裝的SiC MOSFET分立器件作為功率器件。MOSFET正向導通時,其并聯的二極管處于關斷狀態,與IGBT模塊相同。特別地,當二極管導通時,MOSFET也會反向導通,但由于它的導通電阻遠小于二極管的導通電阻,故二者并聯的總電流基本流入MOSFET,流經二極管的電流很小。計算時增加了MOSFET反向導通損耗。MOSFET管正、反向導通損耗公式分別為

MOSFET及其并聯二極管的開關損耗分別為

1.5.2 散熱結構設計

由文獻[28]可知,環境溫度不同對于靜態電流和動態電流間的均衡也有影響,而環境溫度不同又會影響器件的寄生參數,造成并聯器件電流分布不均,進而可能影響到器件的安全運行范圍,或者導致器件的電流損傷。為此,在控制器結構設計時對并聯SiC MOSFET管進行了均溫設計,以降低并聯元件的溫度差異對均流的影響。

由于電機控制器采用風冷方式散熱,設計時將主要發熱器件SiC MOSFET均勻安裝在了圓形殼壁的柱段殼體上,通過熱傳導方式直接將熱量傳遞到外壁面。驅動電路與控制電路發熱較小,且均采用了高溫125℃器件,通過殼體內部空氣的自然對流散熱,不需要額外散熱,對模塊散熱沒有影響。控制系統一共采用了12只TO247-4封裝的SiC MOSFET模塊,而單只模塊的安裝表面寬度約為16 mm,預留一定安裝間隙,每個器件需要安裝并散熱的平面邊長最大值約為23 mm,則需要的散熱器的圓周長不少于276 mm。為了12只模塊散熱均勻,在殼體內部取90 mm的內接正十二邊形平臺作為12只模塊的安裝臺,考慮到固定器件的螺紋深度不小于6 mm,因此起到安裝和散熱作用的圓柱殼體外徑選為100 mm。另外,根據設計要求,散熱圓柱殼體不能有外部肋片或凸起,因此對應模塊安裝面的殼體外壁加工3條深1 mm、寬5 mm的凹槽以加強擾動,同時增大對流換熱面積,如圖19所示。

圖19 控制器散熱結構設計

因SiC MOSFET模塊與殼體進行安裝的面為帶電漏極,因此在模塊與殼壁進行安裝時需考慮絕緣處理,既起到散熱作用又不影響電氣性能,這里通過在模塊和殼體之間增加絕緣陶瓷片的方式來實現電氣隔離,且陶瓷片的尺寸需大于模塊安裝面的尺寸。12只SiC MOSFET的共地部分位于功率板上,3個橋臂的3個下管的功率管的功率源極S管腳焊在功率板上且均與母線負極進行連接,3個上管的漏極管腳D也均焊接在功率板上,且均與母線正極進行連接。

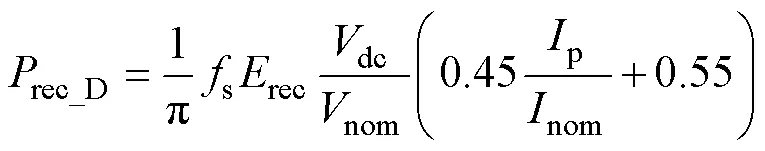

熱流仿真使用ICEPAK和CFDesign軟件,仿真設置如下:

(1)熱源。假設損耗均勻分布于模塊上,根據損耗計算結果賦值。

(2)邊界條件。控制器采取風冷散熱方式,近殼壁處風速為25 m/s。通過ICEPAK仿真先提取出壁面處的平均對流換熱系數為158 W/m2,再將其作為第Ⅲ類邊界條件賦值,空氣溫度不高于40℃。

峰值工況下的控制器溫度場如圖20所示。從圖20的仿真結果可知,殼體內壁穩態最高溫度為147℃。考慮到器件結殼熱阻和陶瓷絕緣墊片熱阻,根據式(25)推算MOSFET的結溫不大于175℃,滿足器件安全運行要求。

圖20 峰值工況下的控制器溫度場

2 分立器件并聯高功率密度SiC控制器樣機及實驗

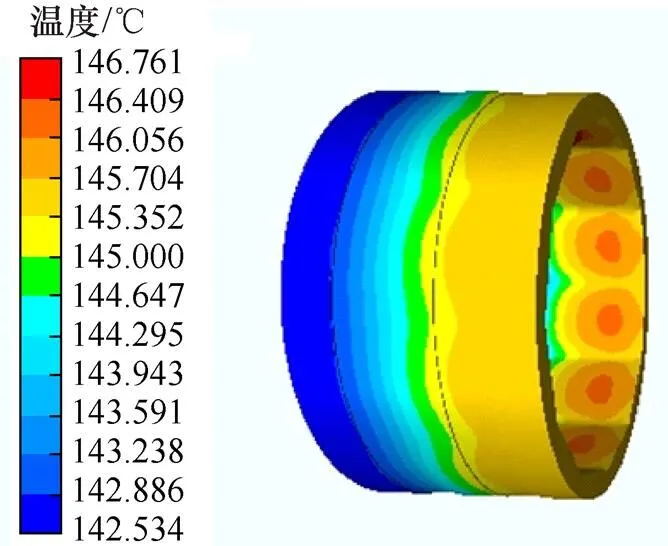

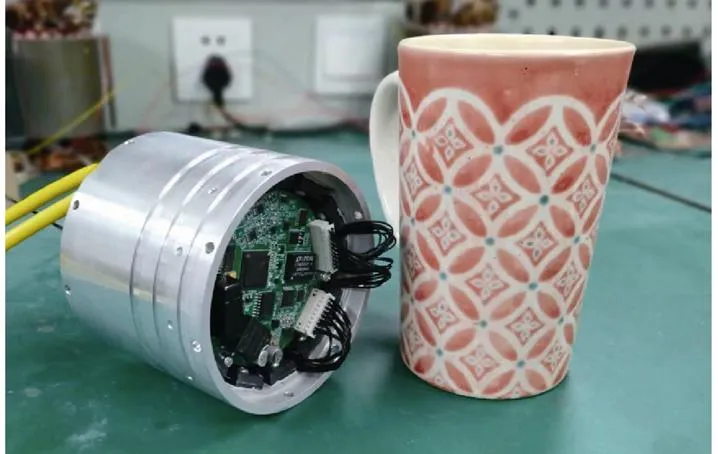

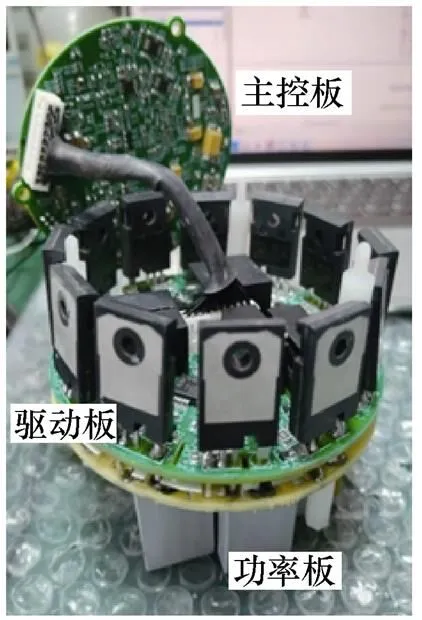

采用第1節所述的SiC MOSFET分立器件并聯控制器關鍵部件設計方法,設計并加工了分立器件并聯高功率密度SiC控制器樣機,設計輸入電壓為600 V,輸出峰值功率為40 kW,控制器體積為0.66 L,最終功率密度達到60 kW/L。控制器外觀如圖21所示,體積與常用的平口喝水杯差不多,功率密度比較高。控制器由圓形控制電路板、驅動電路板以及功率電路板組成的上下三層的電子系統結構,如圖22所示。主控板的直徑只有72 mm,驅動板、功率板直徑均為88 mm,板子形狀為圓形,有利于分立器件的對稱布局,進一步有利于均流。小體積的電路設計節省了系統空間的同時,也有利于降低驅動回路寄生電感。

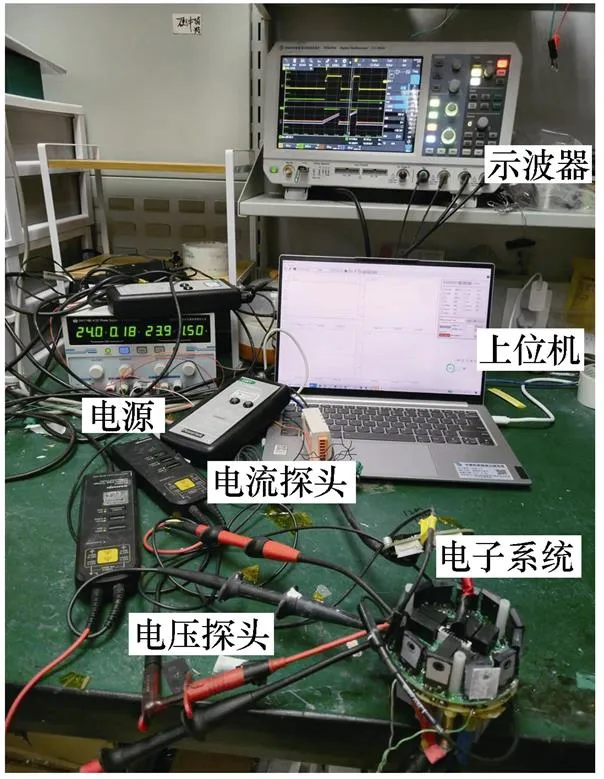

2.1 雙脈沖實驗

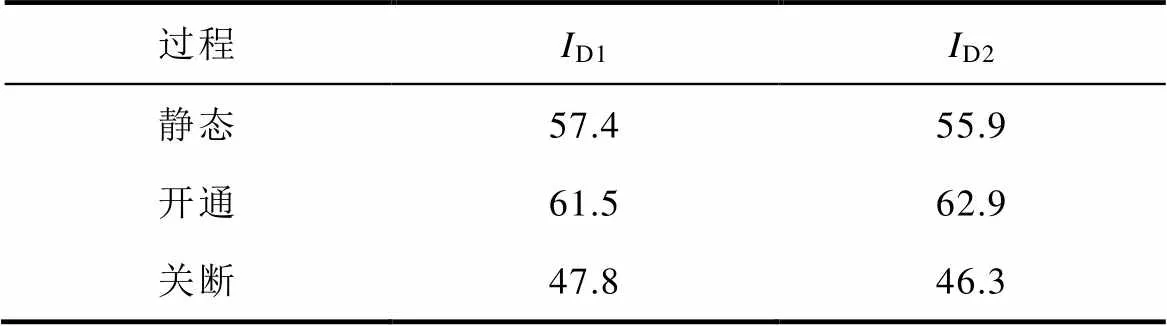

為了驗證系統的均流特性以及在母線電壓600 V下的開關性能,對電子系統進行了雙脈沖測試。測試條件為母線電壓600 V,最大負載電流120 A,驅動電阻2W,負載電感45mH。雙脈沖實驗平臺如圖23所示。電壓探頭采用了兩個差分探頭,型號為TT-SI 8071,帶寬為200 MHz,測量并聯MOSFET管的其中一個的GS電壓與DS電壓。電流探頭采用兩個羅氏線圈,帶寬為100 MHz,分別測量并聯MOSFET管的兩個漏極電流。盡管與同軸分流器相比,100 MHz帶寬的電流探頭由于時間延遲,對于損耗計算可能不精確,但該探頭可以揭示電流波形的細節。雙脈沖測試整體波形如圖24所示,圖中淺藍色線為驅動GS電壓信號,紅色線為MOSFET被測管DS電壓,深藍色與黑色線分別為羅氏線圈測量兩個并聯管的D電流。由測試波形可知,該并聯系統在600 V/120 A的工況下可以可靠地開通與關斷,滿足高功率密度控制器的最大工況要求,并且從并聯MOSFET管的電流波形可以看出系統的動靜態均流效果良好。

圖21 分立器件并聯控制器樣機

圖22 電子系統實物

圖23 雙脈沖實驗平臺

圖24 并聯器件600 V/120 A下均流測試波形

電流不平衡度的計算公式為

表3 并聯管不同時刻的電流瞬時值

2.2 功率實驗

功率實驗中,負載電機轉速由電力測功機控制,轉矩由SiC控制器控制,系統效率及各工況電氣參數由功率分析儀測量得到。直流電源采用850 V電源柜,具有恒壓限流功能。控制器采用風冷強制對流方案,控制器外壁附近實測風速分別約為:上方9 m/s、下方6 m/s、兩側13 m/s。分立器件并聯SiC 控制器在風冷、600 V母線條件下,匹配一臺最高轉速10 000 r/min、額定轉速5 000 r/min、額定功率40 kW、峰值功率80 kW的電機實現了輸出峰值功率40 kW、輸出電流有效值62 A的實驗工況,控制器的功率密度達到了60 kW/L。圖25為并聯SiC MOSFET控制器功率實驗平臺。控制器主體固定在支架上,支架用螺栓固定在實驗桌上,以防倒塌。控制器迎風端安裝半球形導流殼,便于殼體散熱。

圖25 控制器功率實驗平臺

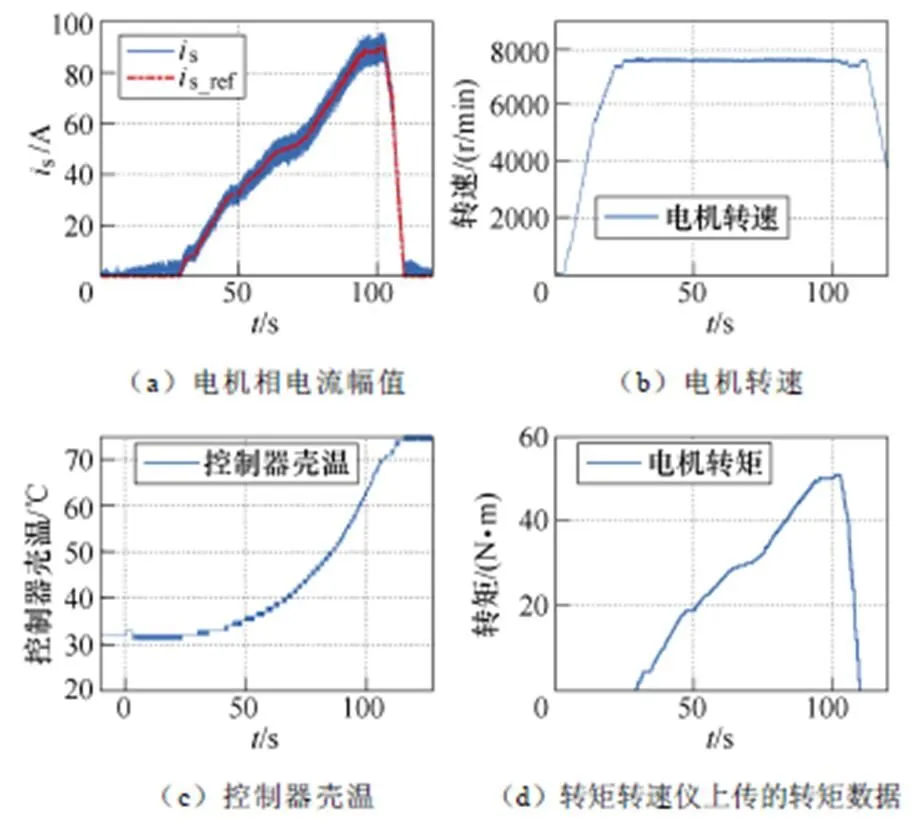

圖26為40 kW實驗時的穩態相電流波形。由波形可看到,三相交流電流幅值相等,均達到88 A,平衡度比較好,控制器運行良好。圖27為上位機與功率分析儀存儲下來的一些數據波形,其中包括電機相電流幅值給定值與實際值波形、轉速波形、控制器殼溫以及電機輸出轉矩的波形。從數據波形可以看到,交流電流峰值達到了88 A,轉速達到了7 600 r/min,轉矩達到了50 N·m。工況持續運行3 min以上時,內壁溫度基本達到熱平衡狀態,內壁最終溫度為76℃,此時估算MOSFET管結溫約為100~110℃,滿足設計要求。這里殼溫為固定在控制器殼體內壁靠近MOSFET模塊處的PT1000測得,由上位機直接讀取溫度值。

圖26 40 kW實驗穩態相電流

圖27 40 kW實驗數據

在風冷強制對流散熱、母線電壓600 V和開關頻率10 kHz條件下測量了控制器在不同轉速(3 000~7 600 r/min)、不同峰值電流(0~88 A)下的效率曲線,其中最高轉速7 600 r/min下控制器達到了峰值功率40 kW。控制器的效率曲線如圖28所示,控制器最高效率達到99.5%,這表明控制器在不同轉速、不同功率下表現優異,能夠高效率運行,也讓整個控制器電機系統達到了95%的高效率,效率數據曲線如圖29所示。

圖28 控制器的效率曲線

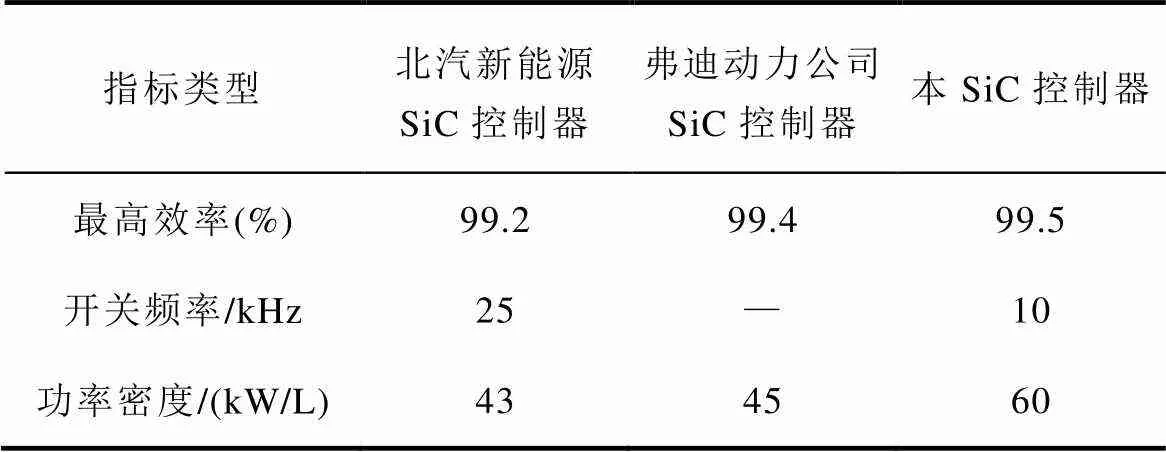

表4列出了研制的SiC控制器與近幾年著名企業研制的控制器的指標對比,無論與北汽新能源SiC控制器相比還是與弗迪動力公司SiC控制器相比,功率密度都近1.33倍,而且效率都比兩個公司的要高。

圖29 系統的效率曲線

表4 本控制器與其他公司控制器指標對比

3 結論

本文基于SiC MOSFET分立器件并聯設計實現了一種高功率密度電機控制器,為了從電氣和散熱角度最大程度地提升材料和空間利用率,實現高功率密度以及分立器件的良好動靜態均流,設計了一種新型的電子系統結構,并提出了一種能動態平衡并聯MOSFET電流的高抗擾驅動電路以及可實現低寄生電感、大電流以及高散熱的適合分立器件并聯應用的新型PCB疊層母排設計方法。提出的電路及方法既有利于實現并聯器件的動靜態均流,又可以減小寄生電感造成的影響,還可以有效抑制負向串擾電壓。對根據這些研究結果開發出來的碳化硅電機控制器,進行了雙脈沖及功率實驗,結果顯示,新設計的分立器件并聯控制器,均流性能好、散熱性能強、功率密度大,并在風冷的條件下,達到了效率最高為99.5%、總功率密度為60 kW/L,為中國的新能源汽車及電機驅動器應用領域,積累了大量具有競爭力的生產技術和寶貴的開發經驗。

在下一階段的工作中,將深入研究并聯器件在更大功率密度下的均流電路設計,研究進一步降低PCB母排雜感的優化設計方法,并且深入研究在更緊湊空間環境下的電子系統和母排間的電氣互聯系統的高效散熱措施。

[1] 劉平, 陳梓健, 苗軼如, 等. 基于開關瞬態反饋的SiC MOSFET有源驅動電路[J]. 電工技術學報, 2022, 37(17): 4446-4457.

Liu Ping, Chen Zijian, Miao Yiru, et al. Active gate driver for SiC MOSFET based on switching transient feedback[J]. Transactions of China Electrotechnical Society, 2022, 37(17): 4446-4457.

[2] 李鑫, 羅毅飛, 史澤南, 等. 一種基于物理的SiC MOSFET改進電路模型[J]. 電工技術學報, 2022, 37(20): 5214-5226.

Li Xin, Luo Yifei, Shi Zenan, et al. An improved physics-based circuit model for SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(20): 5214-5226.

[3] 劉博, 劉偉志, 董侃, 等. 基于全碳化硅功率組件的變流器母排雜散電感解析計算方法[J]. 電工技術學報, 2021, 36(10): 2105-2114.

Liu Bo, Liu Weizhi, Dong Kan, et al. Analytical calculation method for stray inductance of converter busbar based on full silicon carbide power module[J]. Transactions of China Electrotechnical Society, 2021, 36(10): 2105-2114.

[4] 余寶偉, 郭希錚, 部旭聰, 等. 全碳化硅輔助變流器功率回路振蕩問題[J]. 電工技術學報, 2021, 36(增刊2): 619-626.

Yu Baowei, Guo Xizheng, Bu Xucong, et al. Oscillation of power circuit of full SiC auxiliary converter[J]. Transactions of China Electrotechnical Society, 2021, 36(S2): 619-626.

[5] Jahdi S, Alatise O, Ortiz G J A, et al. Temperature and switching rate dependence of crosstalk in Si- IGBT and SiC power modules[J]. IEEE Transactions on Industrial Electronics, 2016, 63(2): 849-863.

[6] Yu Shaolin, Wang Jianing, Zhang Xing, et al. The potential impact of using traction inverters with SiC MOSFETs for electric buses[J]. IEEE Access, 2021, 9: 51561-51572.

[7] 王學梅. 寬禁帶碳化硅功率器件在電動汽車中的研究與應用[J]. 中國電機工程學報, 2014, 34(3): 371-379.

Wang Xuemei. Researches and applications of wide bandgap SiC power devices in electric vehicles[J]. Proceedings of the CSEE, 2014, 34(3): 371-379.

[8] Williamson S S, Rathore A K, Musavi F. Industrial electronics for electric transportation: current state- of-the-art and future challenges[J]. IEEE Transactions on Industrial Electronics, 2015, 62(5): 3021-3032.

[9] 鐘華, 劉志強, 宋佳茵, 等. 分立器件電機控制器功率單元設計與實現[J]. 汽車文摘, 2021(1): 42-47.

Zhong Hua, Liu Zhiqiang, Song Jiayin, et al. Design and implementation of intelligent power unit for dis- crete device motor controller[J]. Automotive Digest, 2021(1): 42-47.

[10] Li Helong, Munk-Nielsen S, Wang Xiongfei, et al. Influences of device and circuit mismatches on paralle- ling silicon carbide MOSFETs[J]. IEEE Transactions on Power Electronics, 2016, 31(1): 621-634.

[11] Hu Ji, Alatise O, Ortiz Gonzalez J A, et al. Robust- ness and balancing of parallel-connected power devices: SiC versus CoolMOS[J]. IEEE Transactions on Industrial Electronics, 2016, 63(4): 2092-2102.

[12] 於少林, 張興, 王佳寧, 等. 分立器件并聯型疊層母排均流分析及優化設計[J]. 電工技術學報, 2023, 38(8): 2086-2099.

Yu Shaolin, Zhang Xing, Wang Jianing, et al. The current balance analysis and optimization design of the laminated busbar with discrete devices in parallel[J]. Transactions of China Electrotechnical Society, 2023, 38(8): 2086-2099.

[13] Peftitsis D, Baburske R, Rabkowski J, et al. Challenges regarding parallel connection of SiC JFETs[J]. IEEE Transactions on Power Electronics, 2013, 28(3): 1449-1463.

[14] Tiwari S, Rabiei A, Shrestha P, et al. Design considerations and laboratory testing of power circuits for parallel operation of silicon carbide MOSFETs[C]//17th European Conference on Power Electronics and Applications, Geneva, Switzerland, 2015: 1-10.

[15] Wang Gangyao, Mookken J, Rice J, et al. Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications[C]//IEEE Applied Power Electronics Conference and Exposition-APEC, Fort Worth, TX, USA, 2014: 1478-1483.

[16] 孫鵬, 魏昌俊, 柯俊吉, 等. 器件特性參數對SiC MOSFET靜動態均流影響的實驗研究[J]. 智能電網, 2017, 5(8): 757-764.

Sun Peng, Wei Changjun, Ke Junji, et al. Experi- mental investigations of the influences of characte- ristic parameters on static and dynamic current sharing of SiC MOSFET[J]. Smart Grid, 2017, 5(8): 757-764.

[17] Abuogo J. Influence of device parameters spread on current distribution of paralleled silicon carbide MOSFETs[J]. Journal of Power Electronics, 2019, 19(4): 1054-1067.

[18] Ning Puqi, Wang Fei, Ngo K D T. Automatic layout design for power module[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 481-487.

[19] 曾正, 邵偉華, 胡博容, 等. 基于耦合電感的SiC MOSFET并聯主動均流[J]. 中國電機工程學報, 2017, 37(7): 2068-2081.

Zeng Zheng, Shao Weihua, Hu Borong, et al. Active current sharing of paralleled SiC MOSFETs by coupling inductors[J]. Proceedings of the CSEE, 2017, 37(7): 2068-2081.

[20] Sadik D P, Colmenares J, Peftitsis D, et al. Experi- mental investigations of static and transient current sharing of parallel-connected silicon carbide MOSFETs[C]//15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2013: 1-10.

[21] Xue Yang, Lu Junjie, Wang Zhiqiang, et al. Active current balancing for parallel-connected silicon carbide MOSFETs[C]//IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 2013: 1563-1569.

[22] Mehrabadi N R, Cvetkovic I, Wang Jun, et al. Busbar design for SiC-based H-bridge PEBB using 1.7 kV, 400 a SiC MOSFETs operating at 100 kHz[C]//IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 2017: 1-7.

[23] 朱俊杰, 原景鑫, 聶子玲, 等. 基于全碳化硅功率組件的疊層母排優化設計研究[J]. 中國電機工程學報, 2019, 39(21): 6383-6394.

Zhu Junjie, Yuan Jingxin, Nie Ziling, et al. Optimum design of planer busbar based on all-silicon carbide power module[J]. Proceedings of the CSEE, 2019, 39(21): 6383-6394.

[24] 董玉斐, 羅皓澤, 楊賀雅, 等. 1.2MV·A混合鉗位五電平變流模塊的結構布局優化和疊層母排設計[J]. 電工技術學報, 2016, 31(8): 11-18.

Dong Yufei, Luo Haoze, Yang Heya, et al. Engin- eering design for structure and bus bar of 1.2MV·A hybrid clamped five-level converter module[J]. Transactions of China Electrotechnical Society, 2016, 31(8): 11-18.

[25] Solero L, Serrao V, Taglioni P, et al. Low-voltage power electronics building block for automotive applications[C]//Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, TX, USA, 2006: 7.

[26] 王寧, 張建忠. 基于開關軌跡優化的SiC MOSFET有源驅動電路研究綜述[J]. 電工技術學報, 2022, 37(10): 2523-2537.

Wang Ning, Zhang Jianzhong. Review of active gate driver for SiC MOSFET with switching trajectory optimization[J]. Transactions of China Electro- technical Society, 2022, 37(10): 2523-2537.

[27] Deng Xin, Huo Y, Wang Qing, et al. Development of a compact 60kW three-phase asymmetry half-bridge power convertor with specifically designed busbar for switched reluctance machines[C]//IEEE NW Russia Young Researchers in Electrical and Electronic Engineering Conference, St Petersburg, Russia, 2015: 311-316.

[28] 范迦羽, 鄭飛麟, 王耀華, 等. 計及熱阻與發射極電感匹配的并聯IGBT芯片穩態結溫均衡方法[J]. 電工技術學報, 2022, 37(12): 3028-3037.

Fan Jiayu, Zheng Feilin, Wang Yaohua, et al. Steady temperature equalization method for the parallel IGBTs considering the thermal resistance and the matching emitter parasitic inductance[J]. Transactions of China Electrotechnical Society, 2022, 37(12): 3028-3037.

Research on High Power Density Silicon Carbide Motor Controller Based on Parallel Connection of Discrete Devices

1,21,21,21,21,2

(1. Institute of Electrical Engineering of Chinese Academy of Sciences Beijing 100190 China 2. Key Laboratory of Power Electronics and Electric Drive Institute of Electrical Engineering Chinese Academy of Sciences Beijing 100190 China)

The motor controllers for new energy vehicles are generally realized by high-power modules, but the high-power module is high cost, large volume, and limited in resources. This paper proposes a high-power density motor controller based on the parallel design of SiC MOSFET discrete devices, which maximizes material and space utilization from the perspectives of electrical and heat dissipation.

In order to achieve high power density, three circular circuit boards with a minimum diameter of only 72 mm, consisting of an upper and lower three-layer structure, were used to design the control circuit, driving circuit, and power circuit. The system has a circular structure and uses the Kelvin source of SiC MOSFET to separate the power and drive circuits. The power circuit uses the power source located on the power board, and the drive circuit uses the Kelvin source located on the drive board. It can prevent the interference of the high-voltage side transient signal on the grid voltage feedback and reduce the dynamic loss, allowing for a symmetrical layout of the parallel tube power circuit to the drive circuit.

In the circuit design, taking into account the area, power, heat dissipation, and other factors, the method of using magnetic components to balance the impedance characteristics of the circuit is selected to realize parallel current sharing. A high anti-interference driving circuit is proposed to dynamically equilibrium the current of parallel MOSFETs. A calculated impedance ferrite magnetic bead is connected in series behind the on and off resistors of each SiC MOSFET tube, ensuring that the parallel equivalent impedance is the same while suppressing ringing caused by rapid switching in the SiC MOSFET gate circuit. In addition, the series connection of source resistance and ferrite bead is added to the Kelvin source pole, which can further synchronize the gate signal and realize current sharing. The anti-crosstalk circuit designed using source resistance achieves dual use of one resistor, enhancing the circuit's anti-interference performance.

A new design of PCB stacked busbar, suitable for parallel application of discrete devices, has been achieved with a focus on the goals of low parasitic inductance, high current, and high heat dissipation. The busbar realizes the integrated design of parallel MOSFET tubes, current sensors, discharge resistors, DC capacitors, and AC-DC terminals. When the opposite direction of current in the vertical direction has the smallest parasitic inductance on the smallest loop area and adjacent circuits have opposite current directions, the inductance decreases with the increase of the number of circuits. Accordingly, a low-noise PCB busbar with multiple sets of stacked PCBs is designed. The top and bottom layers of the busbar both have metal windows for DC and AC wiring, which can weld irregularly shaped metal sheets or strips of different thicknesses to expand the current. Hence, it meets the requirements of carrying maximum current, provides good heat dissipation, and achieves long-term operation with a maximum peak current of 120 A.

Dual pulse and power experiments show that the designed discrete device parallel controller can achieve a maximum efficiency of 99.5% and a power density of 60 kW/L at the highest bus voltage of 600 V, suitable for new energy vehicle systems.

SiC MOSFET, discrete device parallel, high power density, printed circuit board (PCB) stack bus

張少昆 女,1986年生,碩士研究生,研究方向為電力電子系統硬件設計及開發。E-mail: zhangshaokun@mail.iee.ac.cn

范 濤 男,1981年生,博士,研究員,研究方向為高功率密度電機及其控制器系統。E-mail: fantao@mail.iee.ac.cn(通信作者)

TM614

10.19595/j.cnki.1000-6753.tces.230545

十四五國家重點研發計劃資助項目(2022YFB2502800)。

2023-04-27

2023-07-07

(編輯 崔文靜)