一種基于雙模冗余的掃描結構TSPC 型D 觸發器設計

曹雪兵

(中國電子科技集團公司第四十七研究所,沈陽 110000)

1 引 言

隨著工藝技術的不斷發展,集成電路晶體管的寄生電容進一步降低,這也使得集成電路中敏感節點的臨界電荷不斷減小,導致集成電路對軟錯誤愈發敏感[1-2]。由單粒子翻轉所引起的時序邏輯電路中存儲數據的失效一直是業界最為關注的重點。特別是在先進工藝節點的微處理器、微控制器及SoC 中,大量的觸發器邏輯分布于芯片各處,設計出抗單粒子翻轉的觸發器成為系統可靠工作的重要保障[3-5]。進入納米工藝節點后,組合邏輯電路中所產生的單粒子瞬態脈沖成為了繼單粒子翻轉后又一關鍵問題,在納米集成電路中,組合邏輯所產生的單粒子瞬態脈沖寬度已與時鐘脈寬相當,當瞬態脈沖在觸發器鎖存窗口內到達觸發器的數據輸入端時,該瞬態脈沖同樣會引發邏輯錯誤[6-7]。據報道,在65nm 工藝節點,由單粒子瞬態所引發的軟錯誤問題達到了與單粒子翻轉相同的規模,在45 nm 甚至更先進的工藝節點,由單粒子瞬態所引起的軟錯誤將成為危害集成電路可靠性的主要因素[8]。傳統的抗單粒子效應的加固方法包括三模冗余技術以及DICE 單元加固技術,基于空間冗余設計思想的三模冗余技術通過將電路復制三份,然后采用表決器進行表決,從而得到正確的邏輯值[9]。DICE 單元通過將敏感節點進行備份,進而克服單粒子效應的影響。三模冗余結構會消耗較大的面積和功耗,而DICE 結構無法處理SET 問題[10-11]。本研究即基于雙模冗余加固思想,對現有設計進行改進,實現一種具有掃描輸入功能的TSPC(True Single Phase Clock, 真單相時鐘)型D觸發器,TSPC 型觸發器相對于傳統需要互補時鐘信號的D 觸發器,其主要優勢在于面積與性能的提升。本設計基于普通TSPC 型D 觸發器改進完成。

2 普通TSPC 型D 觸發器

觸發器是微處理器、微控制器及SoC 等數字系統的基本存儲單元,其面積和功耗占整個數字系統的相當大部分比重。目前廣泛采用的觸發器結構為采用傳輸門所實現的主從結構觸發器,如圖1 所示。傳統觸發器無法應用于高可靠環境當中。首先,觸發器內的鎖存結構在粒子轟擊下可能會直接發生單粒子翻轉。其次,觸發器輸入數據信號的脈沖信號波動如果落在觸發器的鎖存窗口內,繼而被捕獲也會誘發觸發器發生單粒子翻轉現象,兩種情況都會破壞觸發器輸出端的邏輯值。

圖1 傳統D 觸發器邏輯結構及單粒子效應示意圖

圖2所示為普通TSPC 型D 觸發器的邏輯圖。該邏輯電路由四級反向邏輯所構成,當時鐘信號CLK 為低電平時,假設D 此時輸入數據為1,則P1管關斷、N1管導通,net1 被拉到低電平,如果此時粒子入射P1管的漏極,會在net1 中引入瞬態脈沖,繼而將輸出端Q 的高電平下拉至地,從而引起輸出信號的翻轉。

圖2 普通TSPC 型D 觸發器邏輯結構

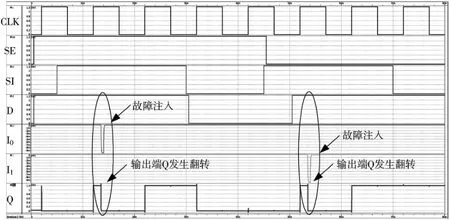

圖3給出了基于UMC 55 nm 工藝的帶有掃描輸入功能的普通TSPC 型D 觸發器的SEU 仿真結果。掃描輸入使能端SE 為高電平,此時掃描輸入數據端SI 信號有效,在13.5ns 時注入雙指數電流脈沖,幅值為10mA,持續時間500ps,上升時間、下降時間皆為50ps。觸發器的數據輸出端在脈沖注入后翻轉為低電平,輸出發生翻轉。當掃描輸入使能端SE 為低電平時,輸入數據端D 有效,在53.5ns 時注入雙指數電流脈沖,脈沖參數與上述注入過程設置相同。從仿真結果可見,觸發器的輸出端同樣發生了翻轉。

圖3 普通TSPC 型D 觸發器單粒子翻轉仿真結果

如圖4 所示為數據輸入端引入瞬態脈沖后,對普通TSPC 型D 觸發器進行仿真的結果。瞬態脈沖的注入時刻為61.9ns,脈沖寬度300ps。從仿真結果可見,在時鐘信號的上升沿,觸發器采到了故障脈沖的低電平,從而引起輸出端Q 值的翻轉。

圖4 普通TSPC 型D 觸發器單粒子瞬態仿真結果

3 改進的D 觸發器結構

在普通設計基礎上進行改進,在此提出基于雙模冗余的掃描結構的TSPC 型D 觸發器(簡稱SDM-TSPC)的邏輯結構如圖5 所示。

為提高系統的可測性能力,此處設計了由P1~P5及N1~N5等晶體管所構成的掃描輸入電路,由掃描輸入控制端SE、掃描輸入數據端SI 及掃描輸出端Q為掃描輸入功能的輸入輸出測試端口。在運行掃描移位模式時,設置SE 為高電平,此時SI 有效,在時鐘上升沿采樣該輸入信號輸出至觸發器的輸出端。在對系統進行故障檢測時,通過將普通觸發器替換成掃描觸發器,完成掃描鏈的插入,進一步利用測試矢量對故障點進行測試。掃描輸入電路的設計增加了該觸發器應用時可測性設計方面的靈活性。

相關研究顯示,在納米工藝節點,由單粒子轟擊所產生的單粒子瞬態脈沖寬度最大可達700ps[12-13]。單粒子瞬態脈沖寬度的增加會大大提高其被捕獲的概率,導致系統軟錯誤率的升高。在SDM-TSPC 型D 觸發器中,設計了由晶體管P11~P14及N11~N14所構成的延遲單元,采用工作在飽和狀態的晶體管來獲得延遲,相比于普通延遲單元具有更低的功耗[14]。在延遲單元以及由CLK 信號控制的C 單元共同作用下,SDM-TSPC 型D 觸發器可以抑制數據輸入端信號上瞬態脈沖的影響[15]。

4 仿真結果與分析

通過仿真,得到基于UMC 55nm 工藝的SDMTSPC 型D 觸發器的SEU 仿真結果,如圖6 所示。掃描輸入使能端SE 為高電平,此時掃描輸入數據端SI 信號有效,在13.5 ns 時注入雙指數電流脈沖,參數設置與常態TSPC 型觸發器仿真時的參數保持一致。觸發器的數據輸出端在脈沖注入后保持高電平,輸出端未受到故障注入的影響。當掃描輸入使能端SE 為低電平時,輸入數據端D 有效,在53.5ns 時注入雙指數電流脈沖,脈沖參數與上述注入過程設置相同。從仿真結果可見,觸發器的輸出端同樣保持原始輸出值,輸出結果未受到故障注入的影響,從而也證明所提出的SDM-TSPC 型D 觸發器具有抗SEU的能力。

圖6 SDM-TSPC 型D 觸發器單粒子翻轉仿真結果

為了評估SDM-TSPC 型D 觸發器在真實輻照環境下的抗SEU 能力,采用故障注入的軟錯誤敏感性評估方法,對普通TSPC 型D 觸發器和改進后的SDM-TSPC 型D 觸發器分別進行故障注入仿真[16]。故障注入脈沖采用雙指數電流源的形式,脈沖幅度設置為4×10-4A,脈沖持續時間設置為100~500 ps之間的隨機值。該脈沖寬度區間為粒子輻照產生瞬態脈沖的主要分布區間。脈沖的上升時間和下降時間設置為50ps[17-20]。在故障注入過程中,雙指數電流源產生于100 個時鐘周期內,并被隨機注入到D 觸發器邏輯結構中的不同電路節點。故障注入的仿真共執行10000 次,得到故障注入仿真結果,具體普通TSPC 型D 觸發器在10000 次故障注入實驗中,發生單粒子翻轉并最終導致輸出信號發生錯誤共374次;SDM-TSPC 型D 觸發器在10000 次故障注入過程中發生單粒子翻轉共39 次。通過對故障注入過程中故障注入點的分析可知,此39 次脈沖注入均發生在SDM-TSPC 型D 觸發器的最終輸出級(N23~N26,P23~P25),而內部敏感節點未出現由于故障脈沖注入引起的輸出端數據錯誤的現象,由此也可證明雙模冗余結構在抗單粒子翻轉方面的有效性。

如圖7 所示為數據輸入端引入單粒子瞬態脈沖的仿真結果。瞬態脈沖的注入時刻為61.9ns, 脈沖寬度300ps,與普通TSPC 型注入脈沖的參數設置相同。從仿真結果可見,在CLK 時鐘上升沿時刻,輸入信號D 上產生瞬態脈沖,但此時觸發器輸出端Q的邏輯電平未受影響,仍然保持瞬態脈沖注入前的高電平。仿真結果證明了所提出的SDM-TSPC 型D觸發器具有抗SET 的能力。

圖7 SDM-TSPC 型D 觸發器的單粒子瞬態仿真結果

5 結 束 語

改進后的基于雙模冗余的帶有掃描輸入功能的TSPC 型D 觸發器,其掃描輸入功能的設計提高了觸發器應用過程中的可測性能力。基于UMC 55nm工藝,在電路級對普通TSPC 型D 觸發器和所提出的SDM-TSPC 型D 觸發器進行了SEU 與SET 的模擬仿真分析,通過故障注入實驗進行驗證,結果表明SDM-TSPC 型D 觸發器具有較好的抗單粒子翻轉和單粒子瞬態的能力。采用雙模冗余結構能夠實現抗單粒子翻轉加固,通過引入延遲單元結構有助于消除輸入數據信號所產生的SET 瞬態脈沖,掃描輸入功能的加入也使得該觸發器具有較高靈活性,大大提高了系統的可測性設計。