K 波段GaN 大功率開關芯片的設計與實現

陳 然,韓玉鵬

(中國電子科技集團公司第十三研究所,河北 石家莊 050051)

0 引 言

射頻開關是通信、測量等微波領域的重要控制元件,射頻開關的存在使得在整機系統可以完成收發、切換、閉塞、優選等一系列的復雜功能,是整機系統的重要元件。隨著裝備的更新與發展,人們對高性能、小型化大功率射頻開關的需求越來越迫切。

近年來,以氮化鎵(Gallium Nitride,GaN)為代表的第三代寬禁帶半導體技術在科學和工程領域突飛猛進地發展,以其高功率密度、高擊穿電壓、高反向關斷電壓、低導通電阻等明顯優勢推動著GaN 微波集成電路(Monolithic Microwave Integrated Circuit,MMIC)工藝技術高速發展,日趨成熟。不斷有新型大功率、高性能的GaN 功率開關電路芯片的報道[1-3]。GaN大功率開關芯片廣泛應用于射頻前端,是實現“兩片式TR”的關鍵器件。

本文介紹的K 波段GaN 大功率開關芯片選用0.15 μm GaN 贗調制摻雜異質結場效應晶體管(Pseudomorphic High Electron Mobility Transistor,pHEMT)工藝進行設計與制作。首先從功率開關的功率壓縮機理分析入手,對GaN 開關模型進行參數提取。在提取模型參數的基礎上,對開關電路進行電路原理圖設計,并利用電路仿真軟件進行整體電路參數的優化和芯片版圖設計及電磁場仿真。通過工藝流片,最終實現了GaN 大功率單刀雙擲開關芯片在18 ~22 GHz 頻帶內,0.1 dB 輸入壓縮功率點可達到連續波12 W,開關插損1.1 dB,隔離度32 dB。控制電壓為0 V 和-28 V 這2 個互補電平,芯片尺寸為1.90 mm×1.50 mm×0.08 mm,滿足實際工程高性能、大功率的應用需求。

1 大功率開關芯片的設計

1.1 功率壓縮機理及模型提取

從開關管模型維度上開展分析,開關管的功率壓縮機理主要有以下2 種:一是在管子的導通狀態下,電流過大超過Imax;二是管子在關斷狀態下,偏壓超出夾斷電壓或者偏壓超出擊穿電壓。對于第一種功率壓縮情況,可以通過增大管子的總柵寬來提高Imax,這種功率壓縮情況一般出現在串聯通路的管子上,因為大部分的射頻信號從這里流過。第二種情況則一般出現在關斷狀態下的管子,對于這種電壓超出臨界值產生的功率壓縮,它所能承受的功率大小取決于管子的擊穿電壓,擊穿電壓越高,功率處理能力越大,但是通過一些手段提高擊穿電壓的同時,也會帶來較大的導通電阻,從而影響插損指標,因此需要在二者之間折衷考慮。實際上,理想的模型本身具有一個較小的RonCoff值,也可以用這個值衡量一個開關模型的性能優劣[4-6]。

首先,對開關模型進行分析,其等效電路如圖1所示,模型的導通電阻Ron是由溝道導通電阻和2個源、漏極板分別對襯底的歐姆接觸電阻共同承擔,而關斷態結電容Coff也會受到源、漏極板對地電容和源漏之間電容的影響,通過調整管子的源漏間距和源漏條的寬度,可以得到不同的RonCoff值,最后通過測試比較,選取了源漏條寬度為8 μm、間距為5.5 μm 的管子模型。

圖1 模型等效電路

通過晶圓流片后實際測試得到了開關模型的S參數,測試電壓為0 V/-28 V,其中一個柵寬90 μm、柵指數為9 的開關模型,Ron為2.95 Ω,Coff為0.68 pF。

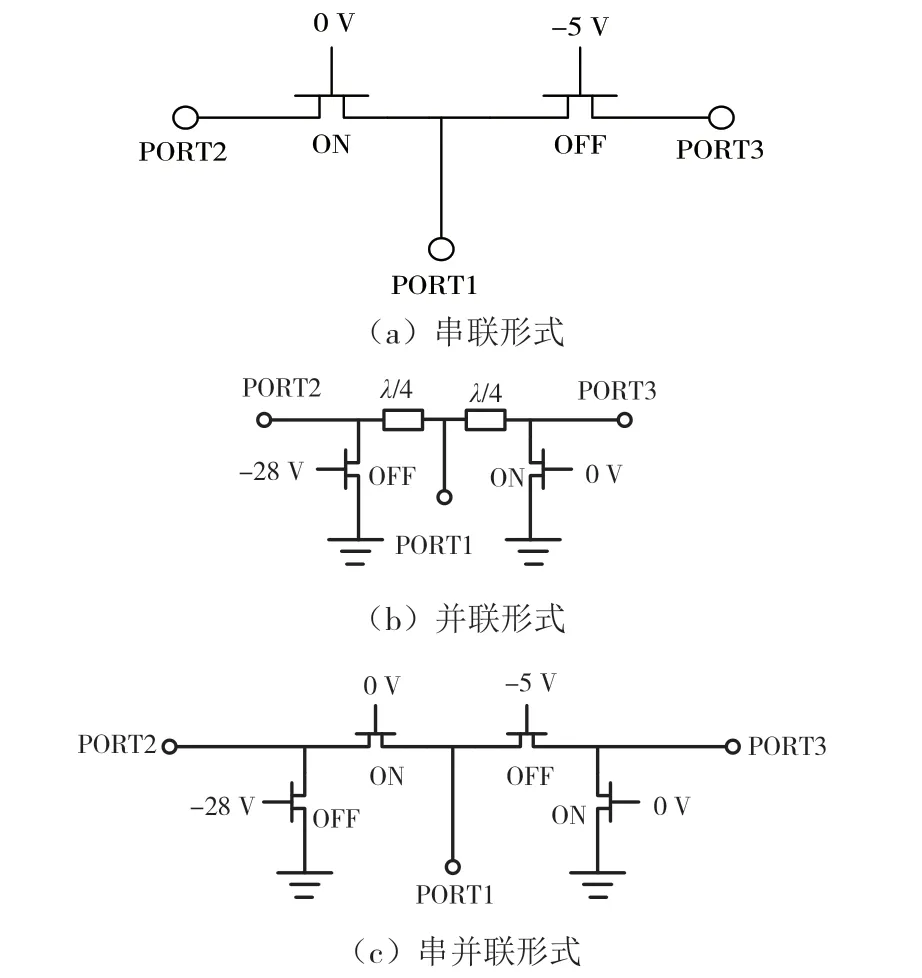

1.2 電路拓撲結構選取

單刀雙擲開關典型的幾種拓撲結構如圖2 所示,其各自優缺點如表2 所示。考慮到射頻前端中對大功率開關的要求主要是耐受功高、插損小以及隔離度好,因此本文選用并聯形式拓撲結構實現K 波段GaN 大功率開關路芯片。

圖2 單刀雙擲開關典型拓撲結構

表2 單刀雙擲開關典型拓撲結構的優缺點比較

1.3 電路參數設計與電磁場仿真優化

電路的設計過程包括電路拓撲結構設計、電路性能參數優化、電磁場仿真和電路版圖的設計。本文介紹K 波段GaN 大功率開關芯片電路設計時,需考慮工作帶寬、0.1 dB 輸入壓縮功率點、插入損耗、駐波比等指標要求及芯片面積的控制。

在設計開關電路時,首先考慮上文中提出的2種功率壓縮機理。對于第一種,即在管子導通狀態時,流過它的電流受限于這個管子的最大承受電流Imax,該工藝下,管子的飽和電流為600 mA/mm 左右。假設一個管子在它的最大電流Imax下工作時,流過功率為12 W,那么它的總柵寬為1.26 mm。對于第二種,即在管子關斷狀態時,偏壓會隨著射頻信號擺動,當它的值超出夾斷電壓或者擊穿電壓時,會出現功率壓縮情況[5,6]。圖3 中可以看出在一個周期之內柵偏置電壓和漏電壓的關系,假設柵上的電阻足夠大(Rbia=1/2πfCgs),即柵極板是射頻開路的,令柵壓的擺幅不超過夾斷或者擊穿電壓,這樣很容易推出當外加控制電壓Ubia等于管子夾斷電壓和擊穿電壓的平均值時,柵壓的擺幅達到最大,即功率處理能力也達到它的極限,此時控制電壓Ubia和最大承受功率Pmax可以表示如下,其中Ubr和Up分別為開關管的擊穿電壓和夾斷電壓。

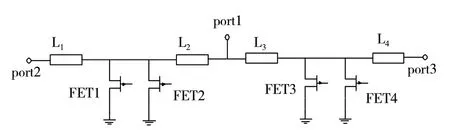

圖4 開關電路拓撲

通過以上分析,采用的電路拓撲如圖4所示,當1、2 端口導通時,FET1 和FET2 處于關斷狀態,FET3和FET4 處于打開狀態。在整個電路中,只有4 只并聯到地的管子,而在串聯通路上,通過幾段四分之一波長線替代了開關管,因此避免了因電流過大而產生的功率壓縮,且這種結構具有較小的插入損耗。

考慮到芯片元器件之間的電磁耦合效應和芯片的實際制作,大功率開關芯片需進行版圖設計和仿真優化,以獲得優異的電性能。基于上述這些必要的匹配網絡,通過電磁場仿真和無源參數的優化,實現所需的電路性能和較小的芯片尺寸。版圖設計中主要需要考慮工藝兼容性和功率容量,在盡量縮小芯片面積的同時充分考慮到帶線與帶線之間、帶線與器件之間互不干擾,通過電磁場分析來提高電路設計的精度。利用仿真軟件對開關電路進行仿真設計,本文設計的K 波段GaN 大功率開關芯片電磁場仿真結果如圖5所示,芯片面積為1.90 mm×1.50 mm。

圖5 電磁場仿真結果

2 芯片制造與測試結果

綜合考慮頻帶、擊穿電壓、反向關斷電壓以及導通電阻等因素,本文設計的大功率開關芯片采用0.15 μm GaN pHEMT 工藝制作。該工藝經過長期的材料性能結構分析研究、優化設計提升以及工藝能力的建設和生長技術的穩定,器件的性能良好、可靠性高,工藝可重復性好、可生產性好且可靠性高。

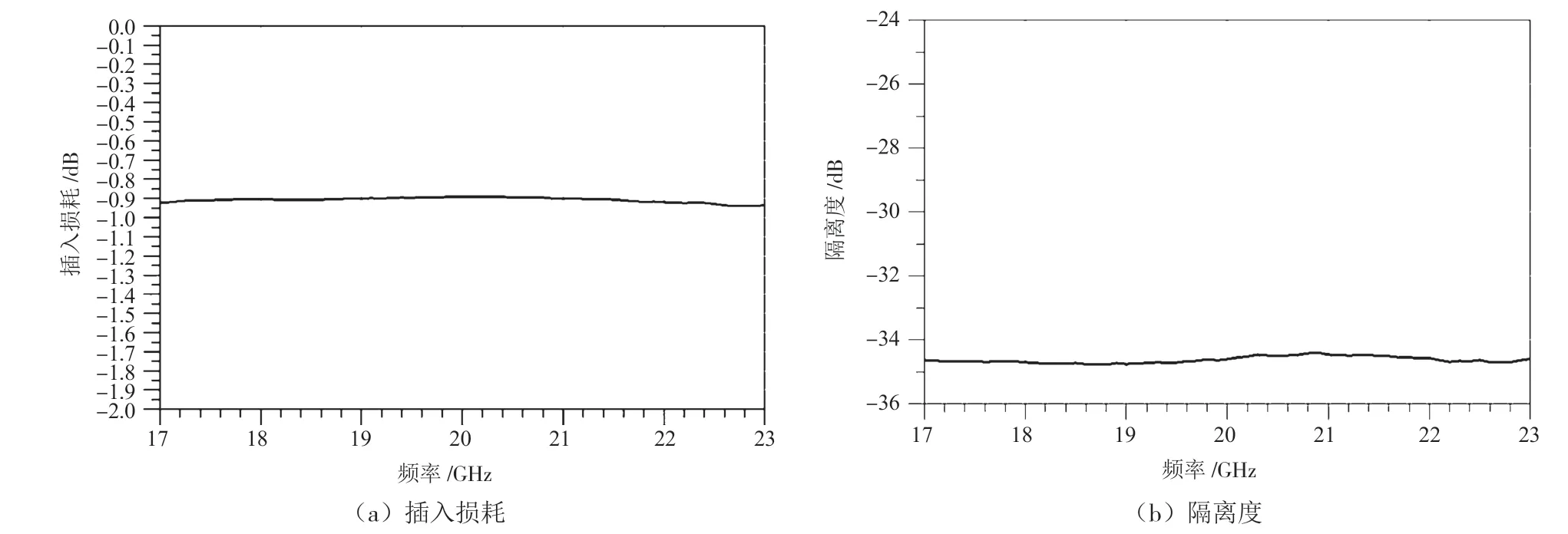

芯片制造完成后,首先對芯片進行裸片測試。本文采用了矢量網絡分析儀和探針臺組成的測試系統,最終設計出的GaN 大功率開關芯片的測試指標如圖6所示。

圖6 測試結果

測試結果為:工作頻帶范圍為18 ~22 GHz;開關插損小于1.1 dB;隔離度大于32 dB;端口回波損耗小于-15 dB。通過裝配測試,在0 V/-28 V 的控制電壓下,測試其連續波功率處理能力,得到開關的0.1 dB 輸入功率壓縮點P_0.1 dB=40.8 dBm,成功實現了開關電路的大功率設計。可以看出,本文提取的開關模型具有可行性,指標優良。

3 結 論

本文對開關電路的功率壓縮機理進行了深入分析和研究,在傳統開關管模型上對其進行改進,獲得了一種高性能的開關模型。并對電路拓撲進行優化設計,基于0.15 μm GaN pHEMT 單片工藝成功設計并實現了一款K 波段GaN 大功率開關芯片。在18 ~22 GHz 頻帶內,0.1 dB 輸入壓縮功率點可達到連續波12 W,開關插損1.1 dB,隔離32 dB。控制電壓為0 V 和-28 V 這2 個互補電平,芯片尺寸為1.90 mm×1.50 mm×0.08 mm,滿足實際工程高性能、大功率的應用需求。