基于快速FIR算法的自適應濾波器的VLSI實現

劉明 丘聰 佳沐

摘 要:【目的】自適應濾波器能根據優化算法來自動調整傳遞函數,是一種強大的自適應系統,在信號處理、通信、雷達、聲吶、地震學、導航系統和生物醫學工程等領域有著廣泛應用。隨著集成電路工藝技術的發展,電路功耗顯得尤為重要,可提升收斂特性和吞吐率。【方法】本研究提出一種基于快速FIR算法的3并行延時LMS自適應濾波器的架構,設計一種新穎的硬件高效架構,用于并行自適應3條支路的權重更新。與傳統濾波器結構相比,并行濾波器具有更高的吞吐率和更低的功耗。為提高自適應數字濾波器的收斂特性,從三條權值更新支路中選擇一個具有更好系統性能的分支。采用細粒度的算術運算單元和重定時技術,能有效降低關鍵路徑的延時。【結果】從ASIC綜合結果可知,與現有最佳結構相比,本研究所提出的3并行9抽頭濾波器架構的功耗降低近16%,面積延時積(ADP)降低近11%。【結論】本研究所提出的架構設計具有重要的實踐指導意義。

關鍵詞:自適應濾波器;3并行DLMS;快速FIR算法;收斂特性;細粒度;專用集成電路

中圖分類號:TN492? ? ?文獻標志碼:A? ? ? 文章編號:1003-5168(2023)09-0015-04

Abstract:[Purposes] Adaptive filter is a powerful adaptive system, which can automatically adjust the transfer function according to the optimization algorithm. It is widely used in signal processing, communication, radar, sonar, seismology, navigation system and biomedical engineering. With the development of integrated circuit technology, circuit power consumption is particularly important,which can improve the convergence characteristics and throughput.[Methods] This study proposes a three-parallel delay LMS adaptive filter architecture based on fast FIR algorithm. A novel hardware efficient architecture is designed to update the weights of three parallel adaptive branches. Compared with the traditional filter structure, the parallel filter has higher throughput and lower power consumption. In order to improve the convergence characteristics of the adaptive digital filter, a branch with better system performance is selected from three weight update branches. The fine-grained arithmetic operation unit and retiming technology can effectively reduce the delay of the critical path. [Findings] From the ASIC synthesis results, compared with the existing optimal structure, the power consumption of the proposed 3-parallel 9-tap filter architecture is reduced by nearly 16 %, and the area delay product ( ADP ) is reduced by nearly 11 %. [Conclusions] It can be seen that the architecture design proposed in this study has important practical guiding significance.

Keywords:adaptive filter; 3-parallel delayed LMS; fast FIR algorithm; convergence properties; fine-grained; ASIC

0 引言

自適應濾波器是目前處理非平穩隨機信號最常用技術。給定輸入信號,迭代設計濾波器參數,以“最佳”映射輸入信號到目標信號[1],估計誤差來自目標信號和濾波器輸出信號。迭代更新濾波器的機制參數來自最小化估計誤差的成本函數,其中最典型的是基于最小均方誤差準則的自適應濾波算法(LMS)[2]。

傳統的LMS算法一般是用軟件來實現的,LMS算法具有嚴格的執行順序[1],將LMS算法映射到具體硬件電路中會產生較長的關鍵路徑。為提高硬件結構的吞吐量,有研究提出一種基于并行DLMS(Paralleled Delayed LMS)算法的自適應濾波器的電路設計方案。DLMS算法更符合真實的硬件電路設計思想,但也有缺點,即隨著延時量的增大,系統收斂性能也會隨之降低[3-5]。

并行處理應用于數字FIR濾波器時,要么增加有效吞吐量,要么降低原始濾波器的功耗[6-7]。已有研究雖對順序FIR濾波器的實現進行考慮,但很少有直接研究降低并行FIR濾波器的硬件復雜性或功耗。本研究提出將并行處理技術與并行DLMS算法結合起來,設計一種基于快速FIR算法的并行DLMS自適應濾波器[7]。

1 并行DLMS自適應濾波器硬件建模

1.1 快速FIR算法

并行處理能有效提高硬件吞吐量和降低硬件功耗。對于傳統并行濾波器,硬件成本隨并行度的增加而線性增加。在實際情況中,設計面積有限制,并行處理所產生的硬件開銷是無法接受的。因此,有必要設計出一種新的并行FIR濾波器,比傳統并行FIR濾波結構占用更少的面積。隨著集成電路技術的發展,電路速度是除面積外非常重要的因素。

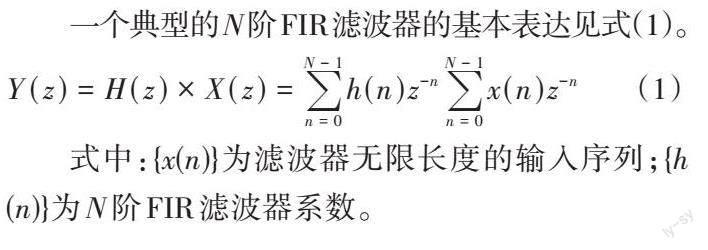

1.2 并行DLMS自適應濾波器的宏觀結構

基于快速FIR濾波算法的基本理論,把(3×3)FFA跟DLMS自適應濾波算法結合起來,構建一個并行度為3的自適應濾波器。一種直接型3并行自適應濾波器整體結構如圖2所示。其中,FIR模塊采用(3×3)FFA結構,相較于傳統的DLMS自適應濾波器,在相同的主頻下,其吞吐量提升2倍。在吞吐率在達到某一特定要求范圍內,可適當降低電路的主頻,并行度的提高能降低電路功耗。直接型自適應濾波器結構具有收斂速度快、穩態誤差小等優點。

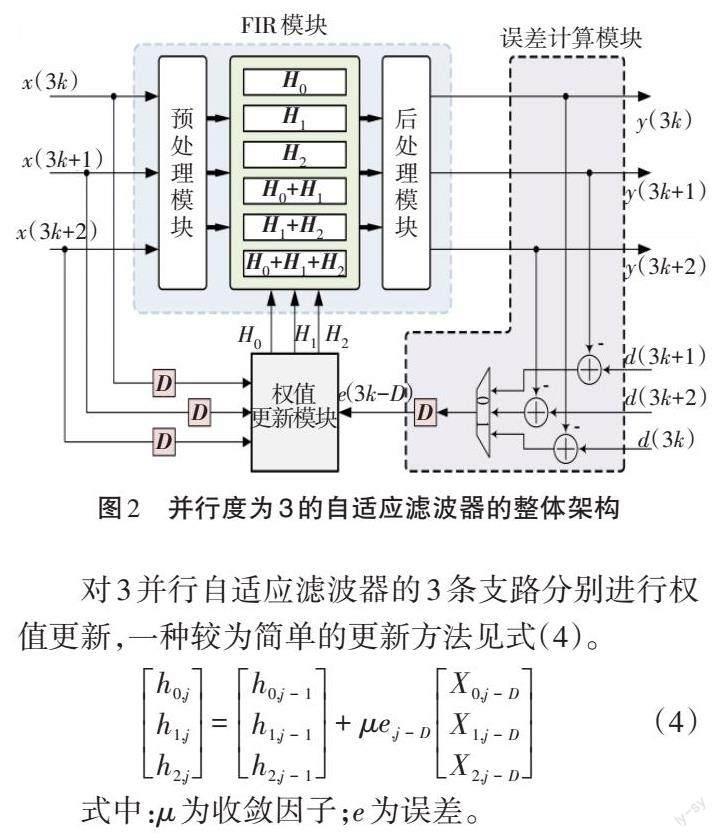

1.3 權值更新模塊的VLSI實現

自適應濾波器跟普通的FIR濾波器最主要區別是濾波器系數的產生機制。自適應濾波器具有自主學習能力,不用先驗知識,最關鍵之處在于權值更新模塊。3并行的自適應濾波器因FIR模塊結構復雜,3條支路都要經過4組濾波器,借鑒傳統的DLMS濾波器設計方法,本研究給出的一種權值更新模塊結構如圖3所示。

從圖3可以看出,共有3條權值更新支路,通過以上權值更新模塊產生9階濾波器系數。其中,H0=[w0(3k)? w3(3k)? w6(3k)],H1=[w1(3k)? w4(3k)? w7(3k)],H2=[w2(3k)? w5(3k)? w8(3k)]。為降低電路復雜性,將收斂因子設置成2的整數倍,可利用移位運算來代替乘法運算,大大降低電路面積。

2 并行自適應濾波器的驗證與分析

自適應濾波器的收斂特性直接決定其性能,大部分應用場景中對收斂速度和穩態誤差要求不高,在設計自適應濾波器時,聚焦于電路主頻、功耗、面積等核心參數。

2.1 自適應濾波算法仿真

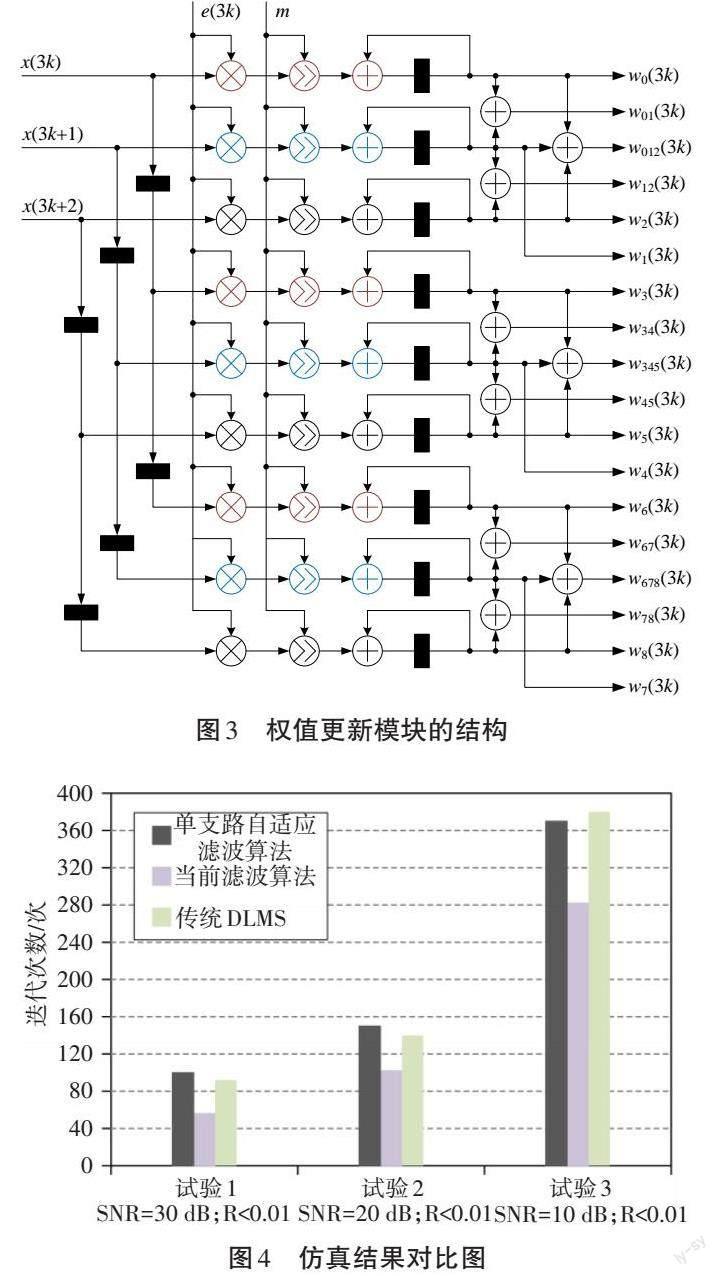

基于系統的實際需求,本研究采用Matlab軟件自適應濾波算法進行仿真研究。該算法采用3條支路的權值更新計算誤差,選擇誤差小的支路的權值,再返回權值更新模塊,循環往復。該算法能加快收斂速度,在一定程度上能降低穩態誤差。

由于噪聲統計具有隨機性,通過并行自適應濾波器來模擬FIR濾波器。假定FIR濾波器系數為h = [10.0, 10.5, -15.0, 41.1, 33.3, 66.6]。試驗時把收斂條件定義為誤差信號絕對值R,分別定義三種邊界條件,即SNR=30 dB、SNR=20 dB、SNR=10 dB,統計結果如圖4所示。從圖4可以看出并行自適應濾波算法的優勢所在。

2.2 并行自適應濾波器硬件仿真

上節已對并行DLMS算法進行仿真比對,展現該算法具有良好的收斂特性。接下來對并行自適應濾波器的硬件建模進行功能仿真,結果如圖5所示。Desired_in信號是夾雜噪聲的輸入信號,Error_out信號是經過自適應濾波后的輸出值,經過2 000 ns左右達到較好的降噪效果。該圖可充分證明本研究設計的自適應濾波器的正確性。

2.3 性能分析

在完成RTL級設計后,對并行自適應濾波器的整體電路進行仿真測試,對比理想值與建模輸出的結果,驗證設計的正確率。基于TSMC 65 nm標準工藝庫,使用綜合工具Design Compiler來完成3PDLMS自適應濾波器硬件單元的邏輯綜合。

在對電路設計進行仿真驗證后,使用TSMC 65 nm標準工藝庫,在0.9 V的工作電壓下完成邏輯實現和綜合,最終得到的硬件速度、功耗、面積等邏輯綜合結果見表1。

由表1可知,本研究提出的硬件結構是3并行9抽頭的濾波器結構,比文獻[1]和文獻[2]中的設計具有明顯吞吐量優勢,幾乎是文獻[1]提出的結構的3倍,同時功耗也減少約16%。因此,在實際應用中,本研究提出的結構能降低電路時鐘頻率,大大降低動態功耗。若要進一步優化,可優先對快速FIR模塊和權值更新模塊進行優化,以最大程度減少電路面積、降低電路功耗,并提高運算性能。

3 結語

本研究對16位3并行自適應濾波器單元進行RTL級建模,在TSMC 65 nm標準工藝下,使用邏輯綜合工具Design Compiler對其進行邏輯綜合實現。本研究設計的3并行自適應濾波器硬件單元完成一次濾波計算要用6個時鐘周期,計算誤差最大不超過1/256,滿足精度高、延遲低的要求。采用簡化3×3FFA濾波結構,比傳統設計大約節省33%的硬件成本。3PDLMS濾波器結構在同樣時鐘頻率下,吞吐率為傳統結構的3倍,在延時方面減小 5.4%,面積延時積(ADP)減小11%,功耗降低16%。

參考文獻:

[1]MEHER P K,PARK S Y.Critical-path analysis and low-complexity implementation of the LMS adaptive algorithm[J].IEEE Transactions on Circuits & Systems I Regular Papers,2014(3):778-788.

[2]YI Y,WOODS R,TING L K,et al.High Speed FPGA-Based Implementations of Delayed-LMS Filters[J].Journal of VLSI signal processing systems for signal,image,and video technology,2005(1-2):113-131.

[3]MEHER P K,MAHESHWARI M.A high-speed FIR adaptive filter architecture using a modified delayed LMS algorithm[C]//IEEE International Symposium on Circuits & Systems,IEEE,2011.

[4]TSAO Y C,CHOI K.Area-efficient parallel FIR digital filter structures for symmetric convolutions based on fast FIR algorithm[J].Very Large Scale Integration Systems IEEE Transactions on,2012(2):366-371.

[5]SRINIVASAN S,BHUDIYA K,RAMANARAYANAN R,et al.Split-path Fused Floating Point Multiply Accumulate (FPMAC)[C]//2013 IEEE 21st Symposium on Computer Arithmetic,IEEE,2013.

[6]姜斌,包建榮.自動變步長BLMS自適應均衡的優化實現[J].電路與系統學報,2013(1):384-389.

[7]尚勇,劉衛東,吳順君.基于并行算法的自適應濾波原理及性能分析[J].電子學報,2001(9):1230-1232.