100BASE-FX物理層收發(fā)器設計與仿真

高金輝, 汪再興, 鄭麗君, 劉曉忠

(蘭州交通大學 電子與信息工程學院, 蘭州 730070)

光通信技術(shù)因具有穩(wěn)定性強與速度快等特點被廣泛應用于各領(lǐng)域之中,且以太網(wǎng)也將光傳輸作為重要發(fā)展方向之一[1-2].100 Mbit/s光以太網(wǎng)作為我國覆蓋最廣的線路之一,研究其PHY層(physical layer,物理層)的設計規(guī)則及實現(xiàn)方式,能為進一步升級以太網(wǎng)傳輸速度提供技術(shù)保障[3].而對物理層的深入研究,了解其傳輸數(shù)據(jù)的速度、位寬與頻率等條件,可為接口處協(xié)議設計提供便利,進一步提高傳輸效率,以此獲得更優(yōu)的用戶體驗[4-6].以太網(wǎng)標準IEEE802.3規(guī)范由IEEE組織制定,其不僅為設計生產(chǎn)PHY芯片提供了規(guī)范,還便于研究者利用統(tǒng)一的標準進行產(chǎn)品開發(fā)[7].

100BASE-FX(100 Mbit/s光纖基帶以太網(wǎng))從20世紀90年代開始被廣泛應用,近年來我國也大量展開100 Mbit/s光以太網(wǎng)的研究.任靖曄[8]提出了一種基于FPGA芯片的100 Mbit/s、1 000 Mbit/s以太網(wǎng)自適應技術(shù).2021年,馮梓軒等[9]研究了乘用車千兆以太網(wǎng)物理層技術(shù).PHY層作為以太網(wǎng)面向用戶的第一層,對其進行研究是探究以太網(wǎng)傳輸規(guī)則及開發(fā)終端設備的首要任務.

100BASE-FX以太網(wǎng)的PHY層可支持全雙工以太網(wǎng)MAC(media access control,控制器)層,且提供并行4B/5B編碼、NRZI(no return zero-inverse,不歸零反相)編碼、數(shù)據(jù)的糾錯及等待功能.上一代10BASE-TX(10 Mbit/s光纖基帶以太網(wǎng))的PHY層使用了曼徹斯特編碼模塊,無并行編碼模塊,數(shù)據(jù)串行輸出.100BASE-FX相較于上一代10BASE-TX串行的編碼方式提供了更高的傳輸效率,在同一時鐘頻率下,并行編碼可提供數(shù)倍于串行編碼的數(shù)據(jù)傳輸速度.

本文主要聚焦于PHY層的PCS、PMA子層,完成收發(fā)器的設計仿真.本設計自上而下設計PHY的頂層功能,設計PCS、PMA兩個子層的功能模塊.實現(xiàn)方式則是由下至上,實現(xiàn)4B/5B和NRZI編碼與解碼、串并轉(zhuǎn)換與并串轉(zhuǎn)換等底層模塊后,通過時鐘匹配與握手協(xié)議將各模塊相連接,實現(xiàn)PCS、PMA兩個子層的功能,完成整體設計.

1 PHY整體結(jié)構(gòu)

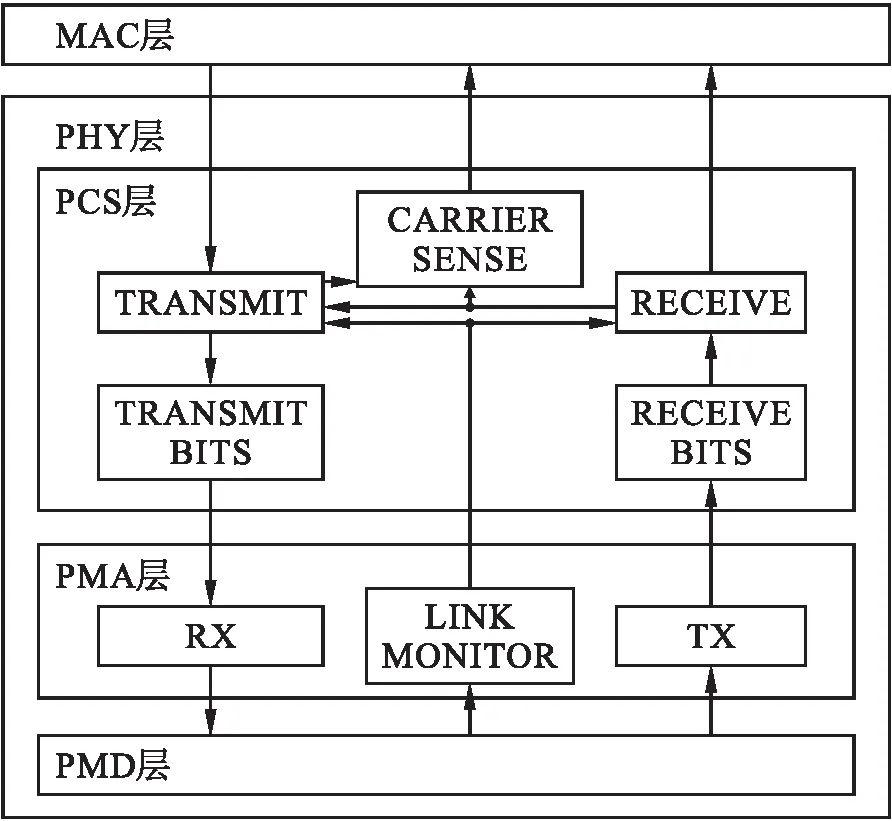

PHY層位于OSI(open system interconnection,開放系統(tǒng)互連模型)七層協(xié)議中數(shù)據(jù)鏈路層的第一層,其負責聯(lián)通MAC層與終端,保證二者間的數(shù)據(jù)轉(zhuǎn)換可正常進行,且規(guī)范物理介質(zhì)參數(shù)并支持100 Mbit/s的數(shù)據(jù)率[10].PHY層結(jié)構(gòu)示意圖如圖1所示.PCS子層與PMA子層共同實現(xiàn)數(shù)據(jù)的收發(fā),其中PCS子層在接收鏈路中將4B/5B解碼后的數(shù)據(jù)送向MAC層,且在發(fā)送鏈路中將MAC層接收的數(shù)據(jù)進行4B/5B編碼;而在鏈路監(jiān)聽功能中,其負責產(chǎn)生載波狀態(tài)信號并將該信號送向MAC層[11].PMA層則在接收鏈路中將從終端接收的數(shù)據(jù)進行NRZI解碼;在發(fā)送鏈路中,將數(shù)據(jù)完成NRZI編碼后再送向MAC層[12].

圖1 PHY層結(jié)構(gòu)示意圖

1.1 PCS子層

PCS子層負責PHY層與MAC層的數(shù)據(jù)交換及鏈路的監(jiān)控,主要提供4B/5B編碼功能[13].服務接口為100 Mbit/s MII(medium independent interface,獨立介質(zhì)接口),所以要求PCS子層的傳輸上限至少為100 Mbit/s.

4B/5B編碼方式由IEEE 802.3協(xié)議定義,具有效率高、易實現(xiàn)等優(yōu)點.在連續(xù)傳送時,傳輸過程中任何一對5 bit代碼連續(xù)的0最多僅有3個,較好地解決了數(shù)據(jù)中出現(xiàn)連續(xù)0的問題,并有助于降低傳輸錯誤率,方便從數(shù)據(jù)中恢復時鐘.

1.2 PMA子層

PMA子層負責與PCS層、PMA層進行數(shù)據(jù)交流和生成使能信號,提供NRZI編碼功能.由于PCS層輸出速度與接收不同,所以需在PMA層重新匹配時鐘.例如,PCS層使用25 MHz時鐘,則PMA層的時鐘頻率需達到125 MHz.NRZI的編碼規(guī)則為當前信號跳變?yōu)?,輸出為1[14].此種方法將信號與時鐘相結(jié)合,解決了數(shù)據(jù)中因連續(xù)出現(xiàn)1而導致的容易出錯及時鐘無法恢復的問題.此外NRZI編碼方式還節(jié)約了帶寬,提高了傳輸效率.

2 分層設計

2.1 頂層設計

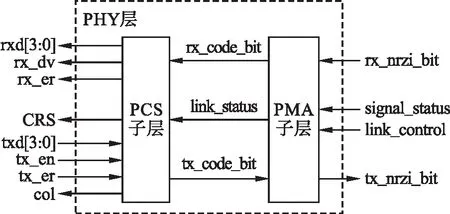

PHY頂層設計如圖2所示.其中,PCS子層受link_status(鏈路狀態(tài)信號)控制,負責對txd(PCS發(fā)送數(shù)據(jù))進行4B/5B編碼和并串轉(zhuǎn)換,或?qū)x_code_bit(串行接收數(shù)據(jù))進行串并轉(zhuǎn)換后4B/5B解碼.PMA子層負責提供使能信號以及NRZI編解碼功能.

圖2 PHY頂層模塊設計

PHY頂層通過聯(lián)通所有的子層模塊從而完成整體設計,但需考慮兩點:

1) 各模塊的信號聯(lián)通.將各模塊相對應的輸入輸出信號連接,以保證邏輯正確,實現(xiàn)發(fā)送、接收鏈路及鏈路反饋等功能.例如,PMA子層LINK MONITOR(鏈路監(jiān)控模塊)所產(chǎn)生的鏈路狀態(tài)控制信號需分別提供給PCS子層的TRANSMIT(發(fā)送模塊)與RECEIVE(接收模塊),進而控制接收與發(fā)送鏈路的工作進程.

2) 提供時鐘.考慮到不同模塊的時鐘匹配,根據(jù)不同模塊的需求,提供對應的時鐘頻率.例如,TRANSMIT與RECEIVE模塊所需的時鐘頻率為25 MHz,方能達到要求的傳輸速率.而TRANSMIT BITS(串行發(fā)送模塊)與RECEIVE BITS(串行接收模塊)模塊為了與其匹配,則需要提供頻率為125 MHz的時鐘.

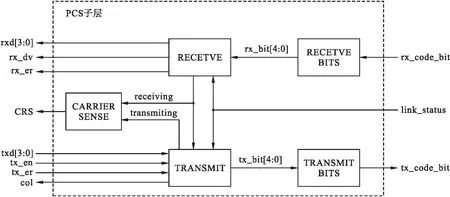

2.2 PCS子層設計

PCS子層模塊結(jié)構(gòu)如圖3所示,共設計了5個模塊,分別是:TRANSMIT、TRANSMIT BITS、RECEIVE、RECEIVE BITS和CARRIER SENSE(載波監(jiān)聽模塊).

圖3 PCS層模塊圖

其中,CARRIER SENSE負責產(chǎn)生CRS(載波狀態(tài)信號)并送向MAC層.此外,當該模塊在檢測到發(fā)送鏈路與接收鏈路均處于工作狀態(tài)或任意一個在工作狀態(tài)時,會判斷CRS有效并向MAC層發(fā)送;而當兩鏈路均未工作時,則將CRS信號視為無效.

RECEIVE負責將來自于RECEIVE BITS模塊的rx_bit(并行接收數(shù)據(jù))解碼成rxd(PCS接收數(shù)據(jù)),并生成用于鏈路監(jiān)控的標志信號,收發(fā)速度可達100 Mbit/s.該模塊在檢測到link_status信號有效后開始工作,當識別出數(shù)據(jù)流中的SSD(start stream data,啟動流數(shù)據(jù)),則開始4B/5B解碼工作.之后可能存在4種工作狀態(tài):若在SSD后為DATA(有效碼型),則正常解碼,并將解碼后的4位寬數(shù)據(jù)送向MAC層;若檢測到ESD(end stream data,終止流數(shù)據(jù)),則解碼結(jié)束,輸出IDLE(空閑碼型)占位并回到空閑狀態(tài);若連續(xù)檢測到5個高電平,即空閑碼型,則解碼過早結(jié)束,此時將rx_er(接收錯誤信號)設置為有效,結(jié)束解碼并回到空閑狀態(tài);而若解碼行為開始后所讀取的數(shù)據(jù)并非上述任意一種信號,則數(shù)據(jù)錯誤,將rx_er設置為有效,之后回到數(shù)據(jù)檢測,并識別下一組數(shù)據(jù).

RECEIVE BITS負責將來自于PMA層的串行rx_code_bit轉(zhuǎn)換為并行的rx_bit.為了與RECEIVE模塊接收速度匹配,RECEIVE BITS模塊數(shù)據(jù)接收頻率5倍于發(fā)送頻率.RECEIVE BITS模塊在檢測到rx_code_bit信號中的SSD指令后,開始工作,將SSD指令后的有效數(shù)據(jù)進行串并轉(zhuǎn)換.當識別出rx_code_bit信號中的ESD指令時,發(fā)送指令,轉(zhuǎn)為檢查SSD狀態(tài).

TRANSMIT負責將來自于MAC層的txd進行4B/5B編碼,生成標志信號,并控制col(鏈路沖突信號)的產(chǎn)生,收發(fā)速度可達100 Mbit/s.空閑時會持續(xù)發(fā)送IDLE數(shù)據(jù),當tx_en(發(fā)送使能信號)有效后,開始4B/5B編碼工作.之后可能有3種工作狀態(tài):若接收SSD的同時,tx_er(發(fā)送錯誤信號)有效,則進入錯誤翻譯路徑,正常發(fā)送兩個SSD信號后發(fā)送HALT(數(shù)據(jù)錯誤碼型),等待tx_er無效,此時col信號取決于接收鏈路;若tx_er無效且接收到有效數(shù)據(jù),則正常編碼,此時col信號同樣取決于接收鏈路;若檢測到ESD指令,則解碼結(jié)束,輸出兩個ESD指令后,回到空閑模塊等待,此時col信號無效.

TRANSMIT BITS負責將已經(jīng)4B/5B轉(zhuǎn)碼后的并行tx_bit(并行發(fā)送數(shù)據(jù))轉(zhuǎn)換為串行tx_code_bit(串行發(fā)送數(shù)據(jù)).為了與接收速度相匹配,數(shù)據(jù)發(fā)送頻率5倍于接收頻率.該模塊對每一個完整的tx_bit進行并串轉(zhuǎn)換,包括SSD、DATA、ESD、IDLE和HALT.

PCS子層設計滿足了100BASE-FX以太網(wǎng)的物理層要求.為了實現(xiàn)時鐘恢復功能,采用了4B/5B編碼方式,此種方式具有16個有效數(shù)據(jù)組,可保證數(shù)據(jù)中擁有足夠多的跳變,從而便于從串行數(shù)據(jù)中恢復時鐘.同時,4B/5B編碼方式可在同樣的25 MHz時鐘頻率下及100 Mbit/s的100BASE-FX上獲得125 Mbit/s的帶寬,滿足了MAC層100 Mbit/s的傳輸速度.

2.3 PMA子層設計

PMA子層負責將PCS子層數(shù)據(jù)進行編碼發(fā)送、將終端數(shù)據(jù)解碼傳回以及對鏈路狀態(tài)進行控制.PMA子層模塊結(jié)構(gòu)共設計了3個模塊,分別是:LINK MONITOR、TX(NRZI編碼模塊)和RX(NRZI解碼模塊),如圖1所示.

TX負責將并串轉(zhuǎn)換后的tx_code_bit進行NRZI編碼,以便被PMD層識別.該模塊對每一個接收到的數(shù)據(jù)均會進行NRZI編碼.

RX負責將從物理終端接收的tx_nrzi_bit進行NRZI解碼,再送向PCS子層.RX模塊對每一個接收到的數(shù)據(jù)進行NRZI解碼,但并不負責檢測數(shù)據(jù)是否為有效數(shù)據(jù).

LINK MONITOR負責對鏈路控制信號進行監(jiān)視,以生成正確的控制信號,并用來控制PCS子層的TRANSMIT與RECEIVE模塊正常工作.當signal_status(數(shù)據(jù)狀態(tài)信號)有效時,啟動計時器.若在計時器周期內(nèi)該信號均是有效的,則等待link_control(鏈路控制信號)狀態(tài),若為有效,則再將link_status信號送出.

3 仿真結(jié)果

本文的物理層設計仿真環(huán)境:Intel Core i5-7200U處理器,Microsoft Windows10 Profession操作系統(tǒng),并使用ModelSim SE 10.5(64 bit)進行測試.

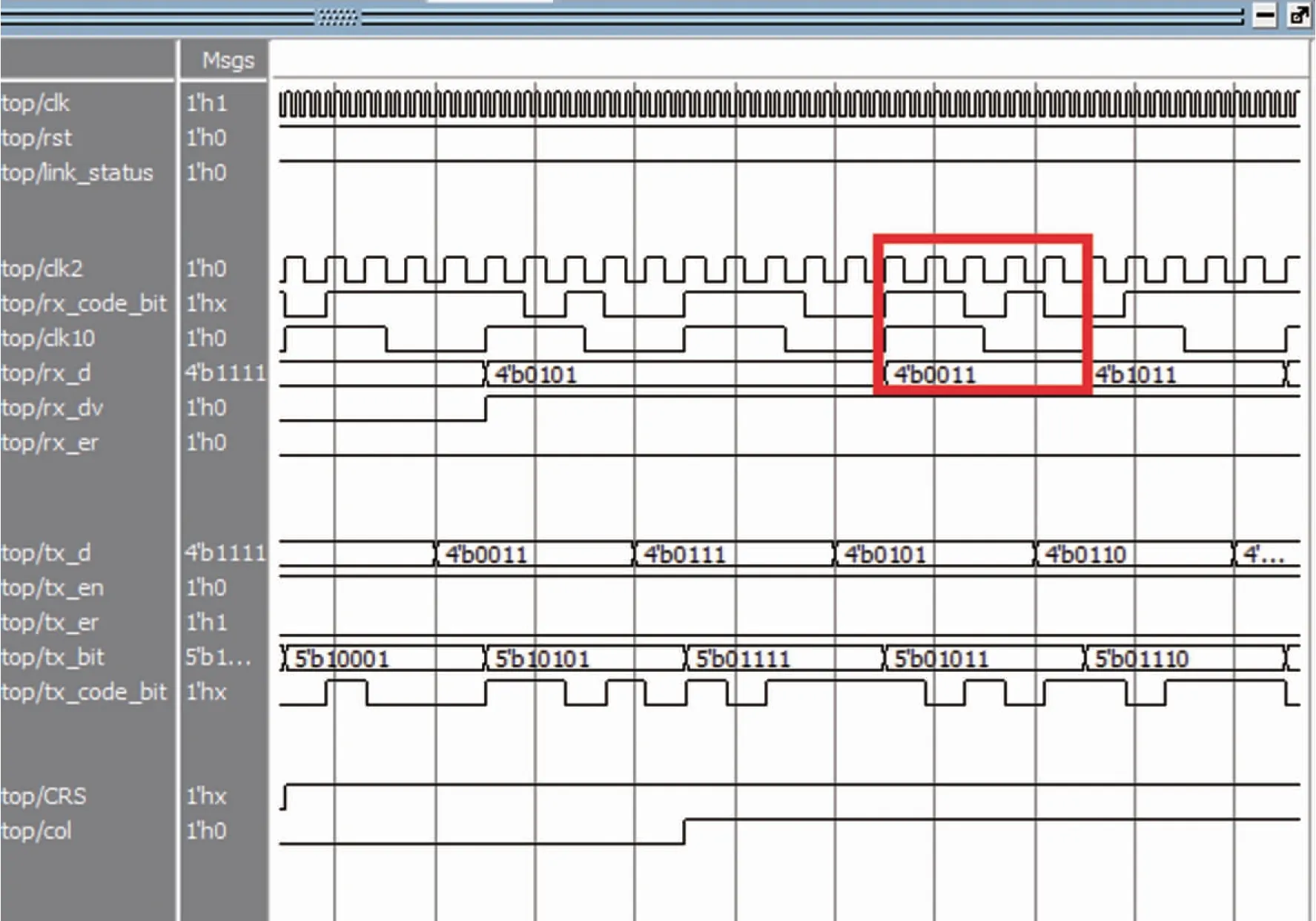

3.1 頂層模塊測試

頂層模塊仿真結(jié)果如圖4所示.10BASE-TX的物理層將終端信號NRZI解碼后送出,數(shù)據(jù)輸出效率十分依賴時鐘,而100BASE-FX在PCS子層采用了4B/5B編碼,使輸出信號并行輸出,較大程度上提高傳輸效率.

圖4 頂層模塊部分信號仿真圖

10BASE-TX僅對輸出信號做了NRZI解碼,輸出速率相當于PCS子層的rx_code_bit,在圖4中對應的時鐘為clk2,頻率為125 MHz;100BASE-FX的輸出為rx_d,對應的時鐘為clk10,頻率為25 MHz.如圖4紅框內(nèi)所示,rx_code_bit在5個時鐘周期內(nèi)共發(fā)送5位數(shù)據(jù),實現(xiàn)了125 Mbit/s的傳輸速度,而rx_d在1個周期內(nèi)輸出4位寬數(shù)據(jù),且信息量相當于4位rx_code_bit,收發(fā)器在25 MHz時鐘下實現(xiàn)了100 Mbit/s的收發(fā).

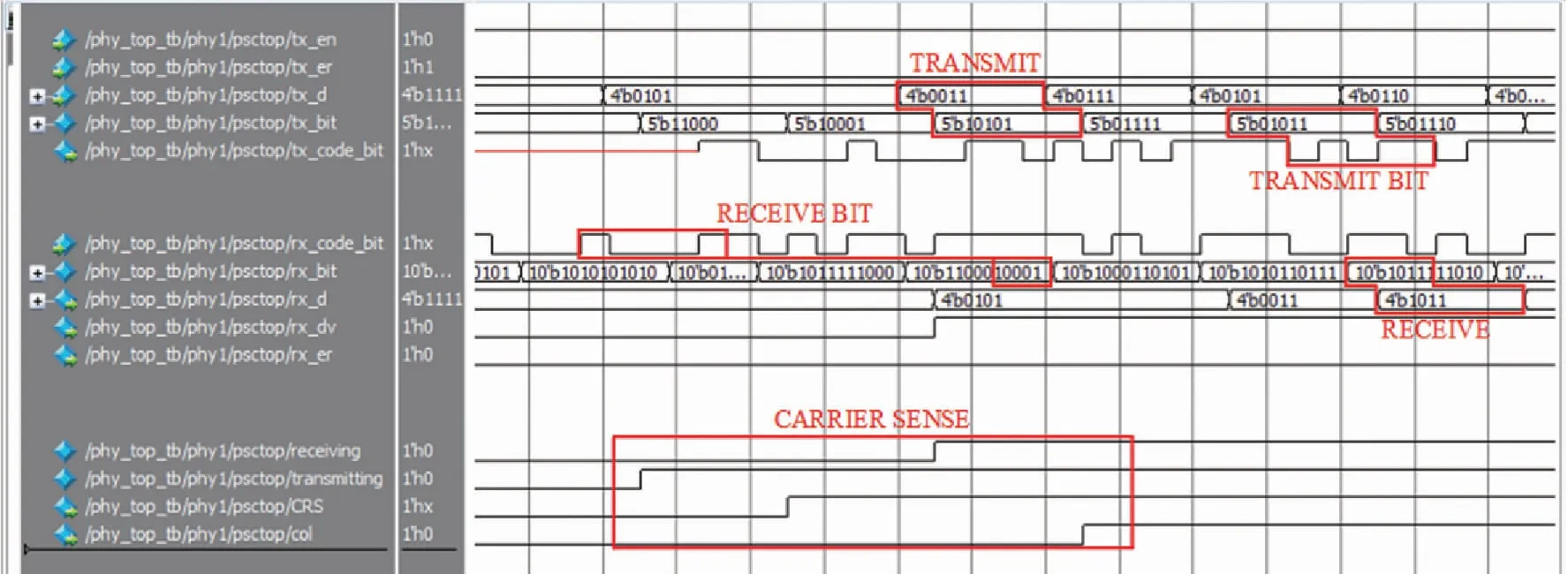

3.2 PCS子層測試

PCS主要完成發(fā)送鏈路的4B/5B解碼與并串轉(zhuǎn)換工作,接收鏈路的串并轉(zhuǎn)換、4B/5B編碼及載波監(jiān)控整體仿真如圖5所示.

圖5 PCS層仿真圖

發(fā)送鏈路中,TRANSMIT與TRANSMIT BIT兩模塊工作正常,獲得有效數(shù)據(jù)后,均在下一時鐘上升沿開始翻譯,且碼型正確.對于無法識別的數(shù)據(jù)不會中斷該發(fā)送過程,而是輸出翻譯錯誤數(shù)據(jù)來占位,以確保用戶可識別出錯誤數(shù)據(jù)組,便于在對應位置檢查,同時也保證其他數(shù)據(jù)的傳輸不受影響.所設計的發(fā)送鏈路在保證傳輸?shù)耐瑫r對錯誤幀位置發(fā)出提示,魯棒性較強.

接收鏈路中RECEIVE BIT與RECEIVE兩模塊工作正常,RECEIVE BIT模塊中輸出信號與輸入信號對應數(shù)據(jù)延時較大,因rx_bit[9∶0]為10位寬信號,所以讀取后輸出信號延遲11個時鐘周期;RECEIVE模塊則在接收到數(shù)據(jù)后的下一個時鐘沿輸出對應數(shù)據(jù).當接收鏈路檢測出接收數(shù)據(jù)中存在無效信號時,將rx_er設置為有效,并跳過解碼該數(shù)據(jù).這樣可有效標記出數(shù)據(jù)錯誤位置,同時不影響其他數(shù)據(jù)傳輸.在接下來的層級處理數(shù)據(jù)時,可根據(jù)rx_er的位置來判斷數(shù)據(jù)是否有效,提高了系統(tǒng)的檢錯能力.

CARRIER SENSE模塊在receiving、transmitting信號同時無效時,CRS信號無效,否則有效.當transmitting信號為高電平而receiving信號為低電平時,CRS信號仍有效.而二者均為低電平時,CRS信號有效,載波監(jiān)控功能正確.本模塊向上層提供鏈路工作情況,并指示上層控制信號的產(chǎn)生,例如在鏈路空閑時提示可進行數(shù)據(jù)傳送等.

3.3 PMA子層測試

PMA子層進行鏈路控制、NRZI編碼及解碼工作的仿真結(jié)果如圖6所示.LINK MONITOR模塊負責生成鏈路工作信號,通過監(jiān)控終端工作狀態(tài),決定PCS子層的發(fā)送、接收進程是否能夠進行.

圖6 PMA子層仿真圖

TX模塊負責將tx_code_bit翻譯為NRZI碼型的tx_nrzi_bit信號.NRZI編碼方式為電平翻轉(zhuǎn)代表邏輯0,電平不變則代表邏輯1.圖6中,tx_code_bit信號100011被翻譯成01101數(shù)據(jù)流,邏輯正確,NRZI編碼功能實現(xiàn).

RX負責將接收到的NRZI碼型的rx_nrzi_bit數(shù)據(jù)翻譯為rx_code_bit信號.圖6中,100001數(shù)據(jù)流被翻譯成rx_code_bit信號101011,邏輯正確,NRZI解碼功能成功實現(xiàn).

4 結(jié) 論

本文介紹了100BASE-FX的PHY層結(jié)構(gòu),著重陳述了PCS子層與PMA子層的信號傳遞方式,且利用4B/5B編碼、NRZI編碼和串并轉(zhuǎn)換等技術(shù)代替了10BASE-TX物理層中的曼徹斯特編碼,完成了對100BASE-FX的PHY層結(jié)構(gòu)及功能的設計,大幅提升了傳輸效率.在ModelSim軟件上進行了驗證,獲得了正確的仿真結(jié)果.在25 MHz時鐘下,實現(xiàn)了最高100 Mbit/s的數(shù)據(jù)交換速度,滿足IEEE802.3規(guī)范.本文所設計的PHY層結(jié)構(gòu)在實現(xiàn)了更快傳輸速度的同時,還可適配市場上所有滿足IEEE802.3規(guī)范的PHY芯片.