一種高穩定諧振芯片封裝技術研究

于 洋,孫 權,孟憲寧,李修鈺,張 強,劉 旭

(中國電子科技集團公司 第四十九研究所,哈爾濱 150028)

諧振芯片的封裝是整個諧振式傳感器制作過程中最關鍵的環節之一,封裝質量對傳感器的性能有直接的影響,其中一個重要的問題是諧振芯片與封裝管座的熱膨脹系數不匹配。

由于硅材料與金屬管座之間的熱膨脹系數不匹配,當環境溫度發生改變時導致諧振芯片上的敏感薄膜發生變形,從而使諧振芯片的本征頻率發生變化,導致傳感器的溫度漂移[1-8]。為了解決該問題,采用隔離層技術,減小因熱膨脹系數不匹配而產生的預應力影響。

目前,通常采用二氧化硅等材料作為隔離層,其熱膨脹系數與硅相同,可在諧振芯片和管座之間起到緩沖作用,當溫度變化時引起的預應力較小。通過ANSYS仿真,比較了不同隔離層厚度對應力隔離的影響,并通過試驗進行對比分析。

1 傳感器工作原理及試驗方法

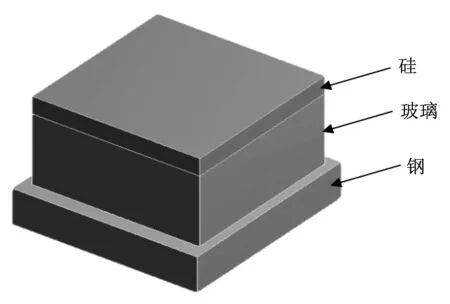

采用的諧振式傳感器芯片結構如圖1所示。以靜電激勵/壓阻檢測為工作方式,采用三層硅結構。力敏電阻在芯片內部聯成惠斯通電橋,壓力敏感膜片與測量介質接觸,在外界壓力作用下,壓力敏感膜片產生變形并傳遞到諧振子,引起振動頻率的變化,實現壓力測量。

圖1 諧振式傳感器結構圖Fig.1 Sketch map of the resonant sensor

當傳感器受到應力作用時,敏感膜片產生的變形會向諧振梁傳遞軸向力。

假設諧振敏感元件沿著X軸設置在[X1,X2]上,由壓力p引起的梁諧振敏感元件的初始應力為[8]:

(1)

(2)

(3)

式中:σ0表示梁所受到的軸線方向應力(Pa);u1、u2表示梁在其兩個端點X1和X2處的軸線方向位移(m);X1、X2為梁在方平膜片的直角坐標系中的坐標值;L表示梁的長度(m),且有L=X2-X1。

兩端固支梁的一階固有頻率為:

(4)

(5)

(6)

式中,ρm表示梁材料的密度(kg/m3);h表示梁的厚度(m)。

敏感膜上力的變化會引起諧振結構諧振頻率的變化。封裝過程中,如果采用芯片直接和金屬管座粘接的方法,當溫度變化時,兩者的熱膨脹系數相差很大,會在敏感膜上引起預應力,從而導致諧振芯片的固有頻率發生變化,導致溫度漂移的產生。

為了減小預應力,采用隔離層技術,在芯片和金屬管座之間增加一層隔離層,減小熱應力的產生。

2 ANSYS仿真分析

采用ANSYS軟件,對諧振式芯片的封裝結構進行仿真,分析其在不同隔離層厚度的情況下受溫度影響后的應力變化情況,仿真模型如圖2所示:

圖2 仿真模型結構圖Fig.2 Structure of simulation model

該仿真結構包括3種材料:上層是硅材料,中間隔離層采用硼硅玻璃,管座采用鋼材料。

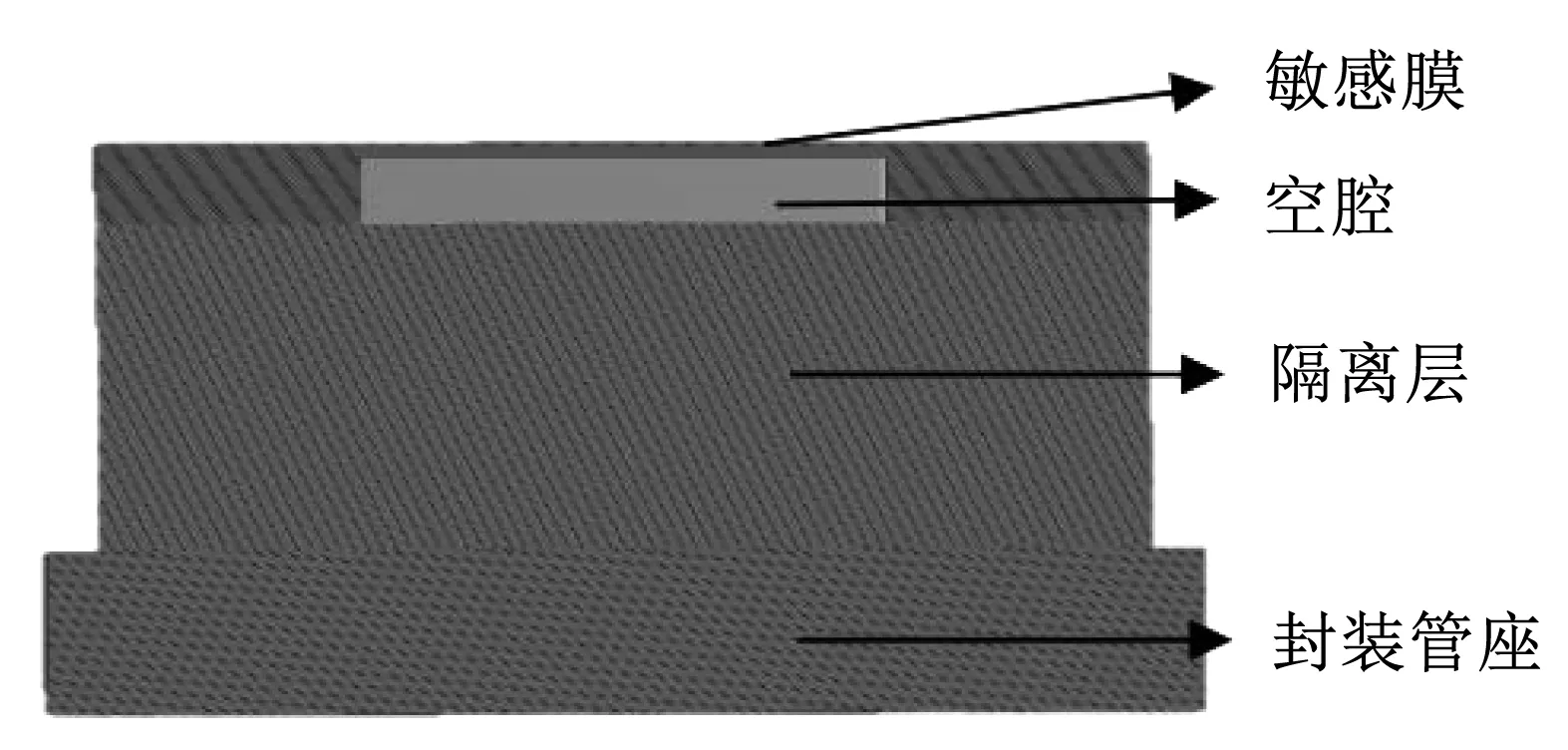

圖3給出了仿真結構的截面圖。諧振芯片是C型硅杯結構,與管座之間通過隔離層過渡。

圖3 仿真結構截面圖Fig.3 Section of simulation structure

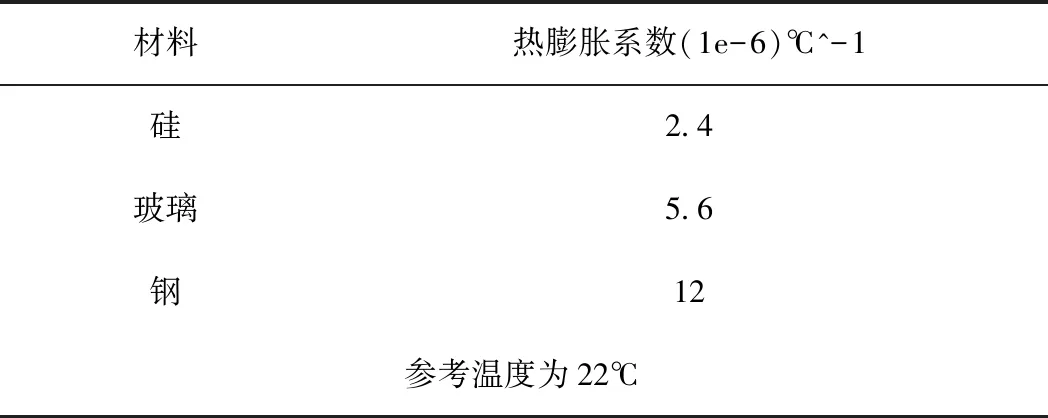

上述3種材料的熱膨脹系數如表1所示:

表1 熱膨脹系數Tab.1 Coefficient of thermal expansion

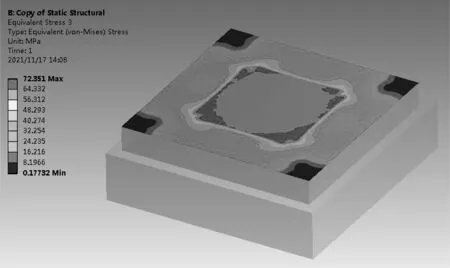

對該結構施加溫度載荷,溫度為80℃,仿真敏感膜上的應力變化,當沒有隔離層時,仿真結果如圖4所示:

圖4 沒有隔離層的仿真結果Fig.4 Simulation results without isolation layer

可以看出,在沒有制作隔離層時,由于熱膨脹系數不匹配,敏感膜上產生的應力最大值為72.3 MPa。

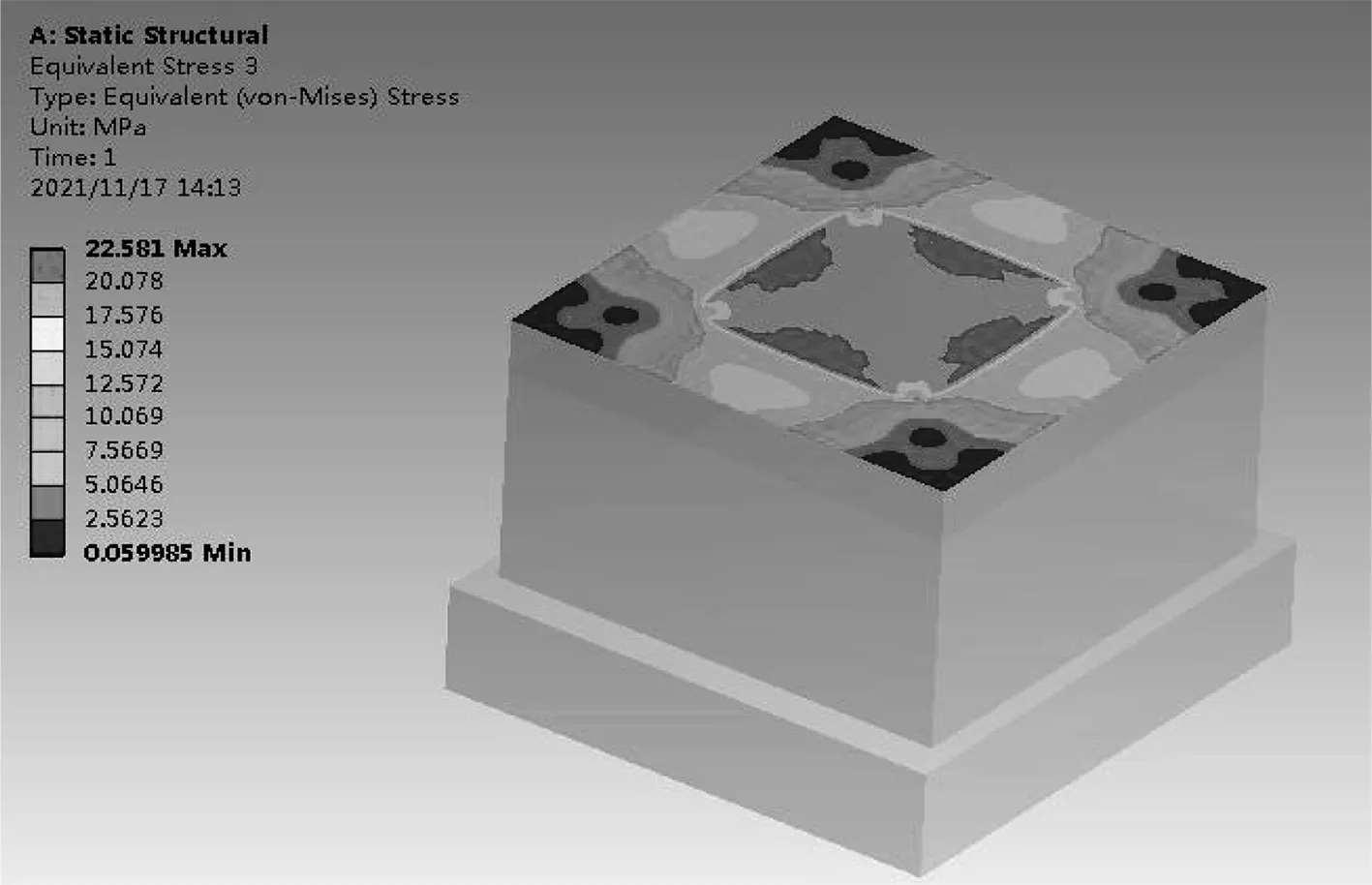

當隔離層厚度為2 mm時,仿真結果如圖5所示:

圖5 有隔離層的仿真結果Fig.5 Simulation results with isolation layer

可以看出,在隔離層的厚度為2 mm時,敏感膜上產生的應力最大值為22.5 MPa。

從仿真結果可以看出,增加了隔離層之后,減小了由于熱膨脹系數不匹配產生的預應力。

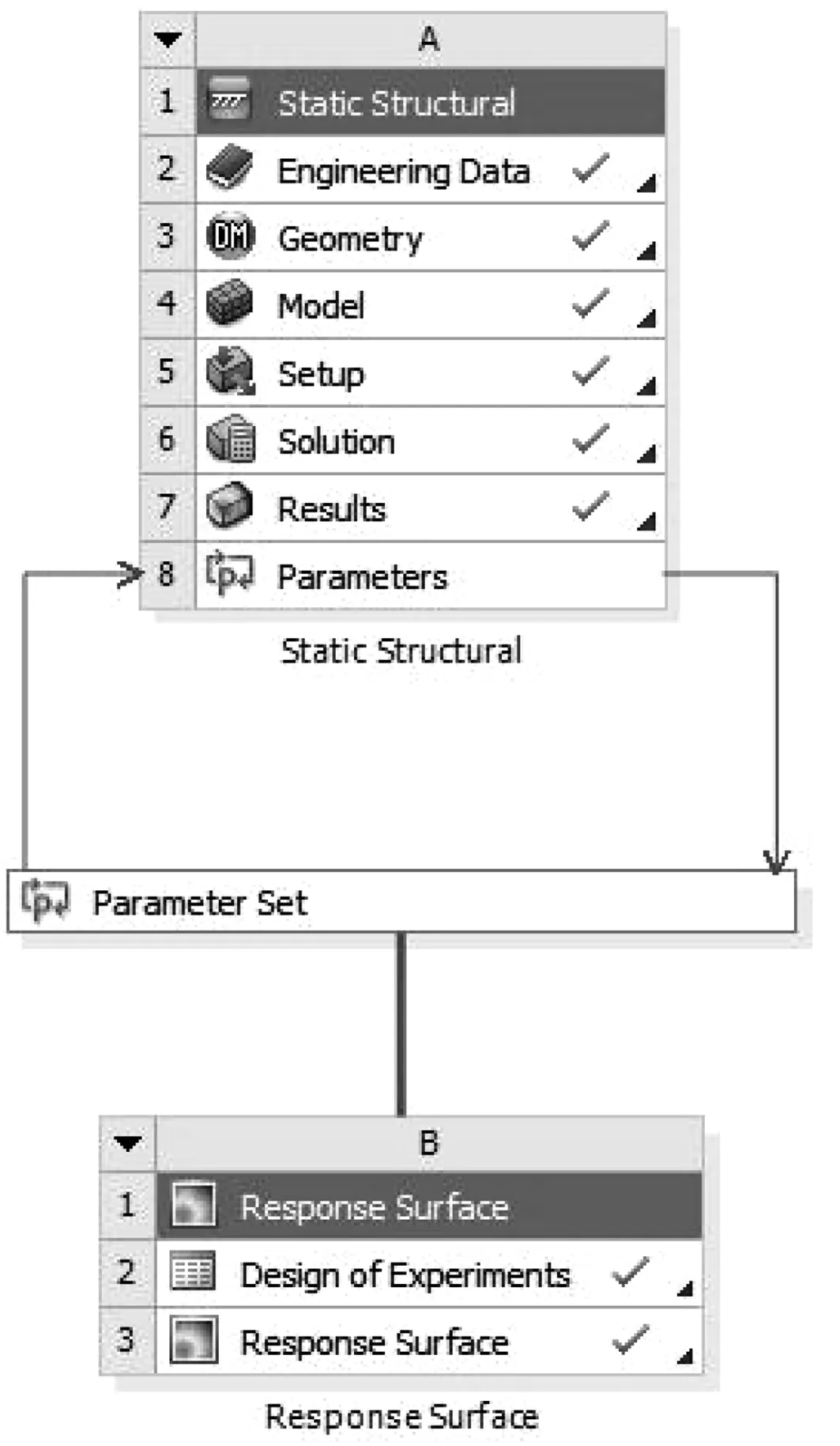

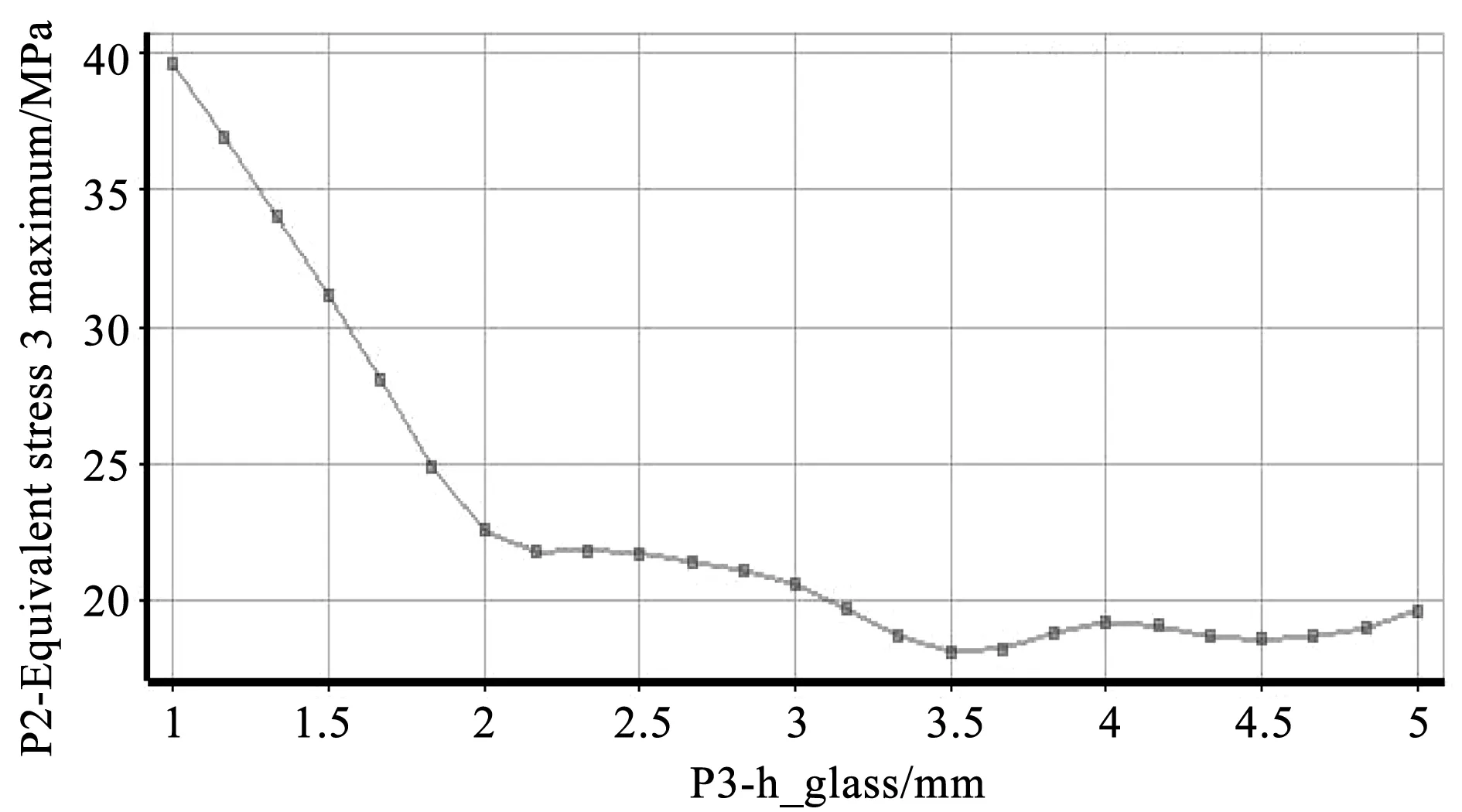

采用ANSYS響應面方法進行DOE分析,分析不同厚度隔離層的影響,設置過程如圖6所示,仿真結果如圖7所示:

圖7中,縱軸是產生的應力值,橫軸是隔離層的厚度,可以看出,隨著隔離層厚度的增加,溫度變化引起的預應力越小,諧振芯片的熱穩定性就越好。

隨著玻璃片厚度的增加,劃片等工藝的加工難度會隨之增加,綜合各種因素考慮,采用隔離層厚度為2 mm和4 mm,分別設計諧振芯片的封裝結構。

圖6 DOE仿真Fig.6 Simulation of DOE

圖7 不同隔離層厚度的影響Fig.7 Influence of different thickness of isolation layer

3 芯片制作及實驗標定結果

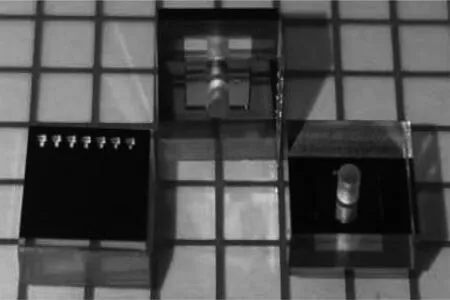

通過靜電鍵合工藝,將器件層和隔離層鍵合在一起,這種鍵合溫度低、鍵合界面穩定、長期穩定性好,圖8為鍵合后的芯片。

圖8 諧振芯片Fig.8 Photo of resonant chip

將鍵合完成的芯片粘接在封裝管座上進行封裝,完成的封裝結構如圖9所示:

對封裝后的諧振芯片進行實驗標定,在不同的溫度下標定其靜態特性。圖10為實驗用的高低溫試驗箱和壓力控制器。

圖9 封裝后的諧振芯片Fig.9 Resonant chip after packaging

圖10 實驗儀器Fig.10 Experimental instrument

為了比較不同隔離層厚度的影響,設計制造了兩種隔離層厚度的芯片封裝形式:一種隔離層厚度為2 mm,另一種為4 mm。

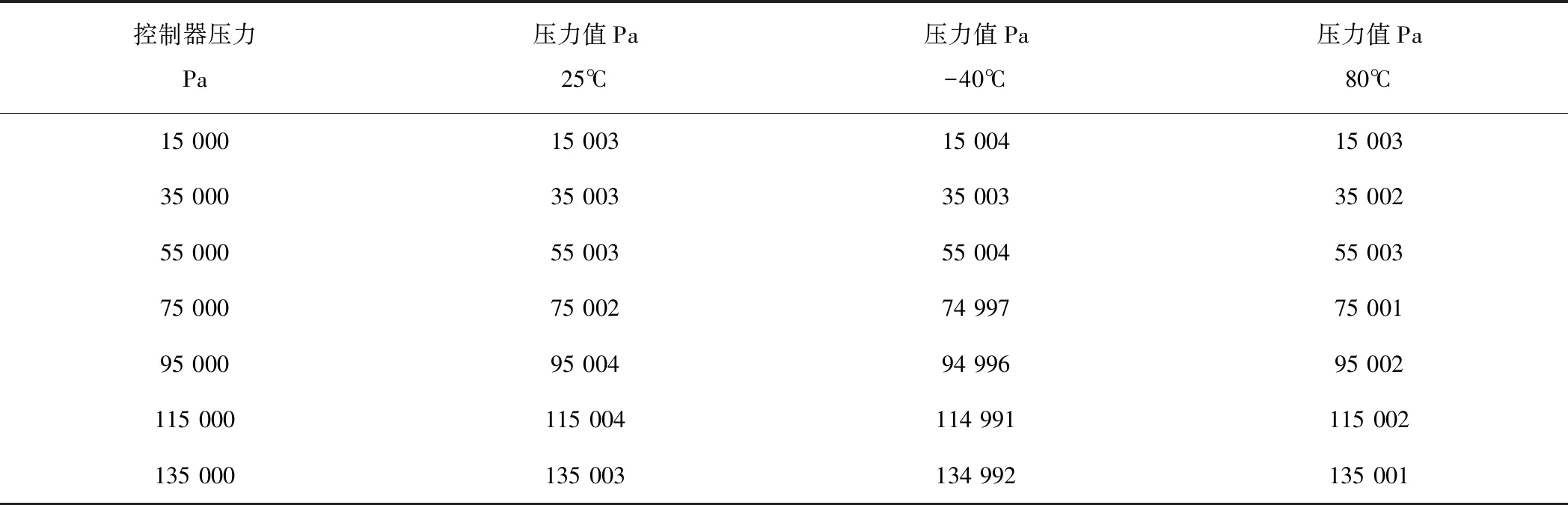

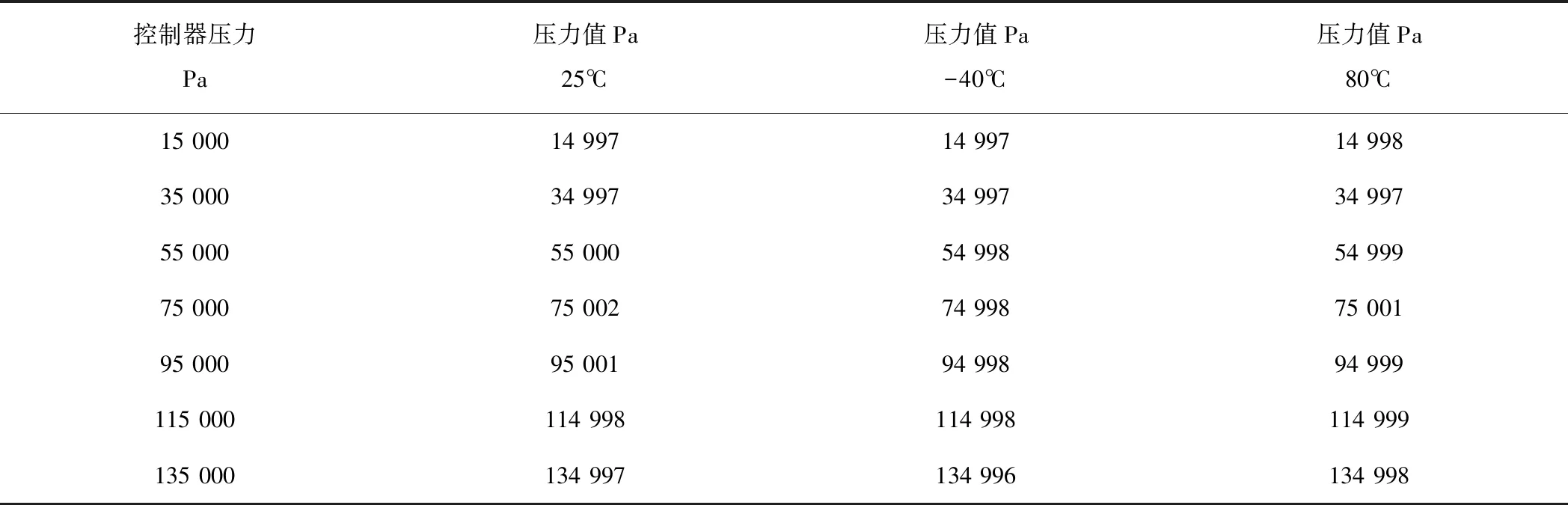

表2為隔離層厚度2 mm封裝結構芯片的實驗結果,表3為隔離層厚度4 mm封裝結構芯片的實驗結果。

表2 隔離層厚度2 mm的芯片實驗結果Tab.2 Experimental results of chip with isolation layer thickness of 2 mm

表3 隔離層厚度4 mm的芯片實驗結果Tab.3 Experimental results of chip with isolation layer thickness of 4 mm

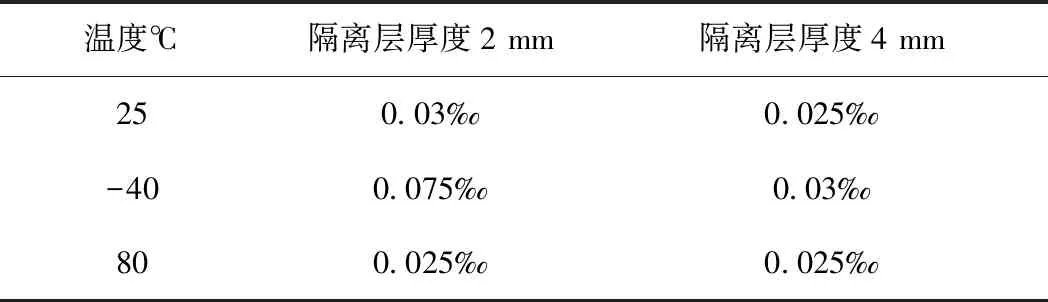

通過實驗數據,計算諧振芯片的精度如表4所示。可以看出,當溫度從-40℃變化到80℃時,2 mm隔離層厚度封裝的芯片的精度漂移為0.55%·℃-1,4 mm隔離層厚度封裝的芯片的精度漂移為0.14%·℃-1,證明隔離層厚度越厚精度的漂移越小,實驗結果與仿真結果一致。

表4 不同溫度下的精度Tab.4 Accuracy at different temperatures

4 結論

采用隔離層技術進行諧振芯片的封裝設計,通過ANSYS軟件,仿真隔離層對預應力的影響,并制作不同隔離層厚度的樣品進行實驗驗證。結果表明,當溫度從-40℃變化到80℃時,2 mm隔離層厚度封裝的芯片的精度漂移為0.55%·℃-1,4 mm隔離層厚度封裝的芯片的精度漂移為0.14%·℃-1。

通過實驗證明,隔離層可有效減小熱膨脹系數不匹配造成的預應力影響,減小諧振芯片的溫度漂移,且隔離層越厚,效果越明顯。