基于浮柵型薄膜晶體管的光控多值存儲(chǔ)器

李博文,張國(guó)成,秦世賢,邢俊杰,李志達(dá),賴秉琳

(福建理工大學(xué) 微電子技術(shù)研究中心,福建 福州 350118)

1 研究背景

人機(jī)交互設(shè)備的興起,對(duì)電子設(shè)備的柔性、透明及溫度敏感等性能提出了新的要求[1]。有機(jī)材料具有來源廣、成本低、范圍寬的光響應(yīng)能力等優(yōu)勢(shì),用有機(jī)材料制作的設(shè)備和器件材質(zhì)輕薄、韌性高,更易做成大面積柔性器件[2]。20世紀(jì)70年代,有機(jī)半導(dǎo)體聚合物的問世使得有機(jī)薄膜晶體管得到快速發(fā)展[3]。有機(jī)材料的成膜方法多樣,將有機(jī)物配成溶液后進(jìn)行薄膜加工,低溫(<200 ℃)退火,能有效控制薄膜的厚度與表面粗糙度,且對(duì)設(shè)備要求低,使晶體管的加工效率提升[4~5]。由于大數(shù)據(jù)背景下摩爾定律失效及馮·諾伊曼計(jì)算構(gòu)架的限制,存儲(chǔ)元件及其他電子器件的功能勢(shì)必迎來一次革新,以應(yīng)對(duì)硬件性能限制信息處理效率的局面。近年來,浮柵層加輔助層的新型器件結(jié)構(gòu)逐漸成為熱門研究方向。Wang等[6]提出了一種基于二維材料的浮柵型非易失性存儲(chǔ)器,采用雙柵結(jié)構(gòu)以降低工作電壓、提高數(shù)據(jù)保持時(shí)間。Li等[7]通過插入半導(dǎo)體層以增強(qiáng)存儲(chǔ)器的性能。Gao等[8]制備了一種異質(zhì)結(jié)構(gòu)垂直有機(jī)光電存儲(chǔ)器晶體管,該器件可以從非易失性存儲(chǔ)器轉(zhuǎn)變?yōu)槿斯ね挥|,展示了一種制造高性能非易失性光電存儲(chǔ)器和人工突觸的新技術(shù)。Chiang等[9]利用一種基于聚合物/鈣鈦礦量子點(diǎn)(QD)混合納米復(fù)合材料作為光響應(yīng)浮柵的光電晶體管存儲(chǔ)器,實(shí)現(xiàn)了完全可光切換的存儲(chǔ)器件。Fu等[10]采用串聯(lián)結(jié)構(gòu),由發(fā)光電阻式開關(guān)存儲(chǔ)器和鈣鈦礦太陽能電池組成了一種電阻式開關(guān)存儲(chǔ)器,器件的狀態(tài)可以進(jìn)行電和光編碼,具有高電阻狀態(tài)和低電阻狀態(tài)。

在溶液法加工過程中,若相鄰兩層薄膜的材料的溶質(zhì)、溶劑的相容性不正交,會(huì)造成薄膜交界面互溶、損壞。而無機(jī)材料與有機(jī)材料的特性在某種程度上能夠搭配、互補(bǔ)。無機(jī)材料通常被認(rèn)為是熱穩(wěn)定性、化學(xué)穩(wěn)定俱佳的材料。但許多無機(jī)薄膜生長(zhǎng)過程中常伴隨著高溫、高壓,對(duì)生產(chǎn)設(shè)備要求極高,導(dǎo)致生產(chǎn)成本提高,大面積生產(chǎn)受限。隨著技術(shù)進(jìn)步,無機(jī)薄膜的制備工藝逐漸完善,甚至出現(xiàn)溶液法制備無機(jī)薄膜的工藝。因此,除了純有機(jī)晶體管,有機(jī)-無機(jī)薄膜晶體管器件的研究也得到關(guān)注。

本研究制備了一種可光調(diào)控的異質(zhì)結(jié)晶體管信息存儲(chǔ)器,器件結(jié)構(gòu)結(jié)合了有機(jī)材料與無機(jī)材料的優(yōu)點(diǎn),通過PN半導(dǎo)體層異質(zhì)結(jié)、有機(jī)浮柵層摻雜與控制無機(jī)隧穿層厚度達(dá)到控制存儲(chǔ)器性能的作用[11],存儲(chǔ)器性能可光調(diào)制、存儲(chǔ)窗口為60 V、開關(guān)比為104。另外,通過使用吸光的共混半導(dǎo)體,使器件具備了一定的光傳感、光檢測(cè)的功能,在光電協(xié)同控制下,具有3個(gè)等級(jí)的電流水平信號(hào)。同時(shí)對(duì)光、電兩種信號(hào)敏感的有機(jī)晶體管存儲(chǔ)器,在電子設(shè)備中可作為基本信號(hào)存儲(chǔ)單元與光感受器,在信息處理、運(yùn)算和顯示等場(chǎng)景中也具有較強(qiáng)的應(yīng)用潛力,可在智能手機(jī)、計(jì)算機(jī)、顯示器等功能日趨多樣化的電子設(shè)備中發(fā)揮作用。

2 器件的制備

2.1 器件結(jié)構(gòu)

器件制備使用的基底是單面拋光的氧化硅片,純Si層充當(dāng)柵電極,SiO2層充當(dāng)絕緣層,如圖1所示。源漏極是用掩模版真空熱蒸發(fā)下形成的圖案化電極,電極間溝道尺寸1 000 μm*30 μm;半導(dǎo)體層是溶液旋涂法制成的P型、N型半導(dǎo)體共混異質(zhì)結(jié);隧穿層為Al2O3;浮柵層為內(nèi)部分散有CdSe@ZnS量子點(diǎn)的PVP絕緣層。

圖1 器件結(jié)構(gòu)圖Fig.1 Device structure diagram

2.2 材料

本研究所采用的晶體管襯底、柵極及絕緣層為單面拋光SiO2,購(gòu)于蘇州晶矽電子科技有限公司;浮柵層為摻有量子點(diǎn)的聚合物PVP薄膜,其溶液由PVP和交聯(lián)劑HAD溶解于溶劑PGMEA組成(均自Sigma-Aldrich);電荷捕獲材料為CdSe@ZnS量子點(diǎn),購(gòu)買于普加福光電;隧穿層材料為原子層沉積的Al2O3;半導(dǎo)體層材料為聚合物IDTBT和PCBM溶解于溶劑CHCl3,其中,聚合物IDTBT和PCBM來自1-Material;電極材料Au顆粒來自普加福光電;溶劑CHCl3及硅片清洗試劑丙酮(99.9%)、異丙醇(99.9%)來自國(guó)藥集團(tuán)化學(xué)試劑有限公司。

2.3 晶體管工藝制備過程及參數(shù)

(1)基片清洗與溶液配制

第一步,使用丙酮、異丙醇、去離子水依次對(duì)基片進(jìn)行清洗,用氮?dú)?N2)噴槍吹干襯底表面殘留的液體。

第二步,按 CdSe@ZnS 量子點(diǎn):先配制 PVP 溶液,將150 mg PVP和15 mg HDA交聯(lián)劑溶解在1 mL的 PGMEA溶劑中,并在磁力攪拌器上60 ℃攪拌溶解24 h。

第三步,取 CdSe@ZnS 量子點(diǎn)溶液(溶劑為CHCl3、5 mg/mL)加入PVP溶液中(CdSe@ZnS:PVP的質(zhì)量比為1∶10)配成浮柵層溶液。

第四步,配制半導(dǎo)體溶液,ITDBT∶PCBM質(zhì)量比為4∶1,混合溶解在CHCl3中,60 ℃加熱2 h。

(2)各層薄膜制備

浮柵層的制備是利用設(shè)備型號(hào)為Therom/EZ6的旋涂機(jī),用直徑為0.22 μm的過濾頭將浮柵層溶液滴到基片上,使用兩步旋涂法,600 r/min旋涂5 s,2 000 r/min旋涂30 s,后將樣品移入手套箱,120 ℃退火2 h。

隧穿層的制備是利用設(shè)備型號(hào)為Beneq TFS 200型的原子沉積設(shè)備(ALD),在浮柵層上利用原子沉積法(ALD)制作8 nm厚的Al2O3作為隧穿層。

半導(dǎo)體層制備所利用的設(shè)備與浮柵層相同,將半導(dǎo)體溶液滴在Al2O3上,1 000 r/min旋涂60 s 后,140 ℃退火10 min。

電極的制備是利用設(shè)備型號(hào)為BOX-RH400型的真空蒸鍍機(jī),利用特制掩模版蒸鍍上一對(duì)金電極作為源極和漏極,用設(shè)備型號(hào)為Keysight B2912A的半導(dǎo)體測(cè)試儀進(jìn)行器件性能測(cè)試。

3 實(shí)驗(yàn)結(jié)果分析與討論

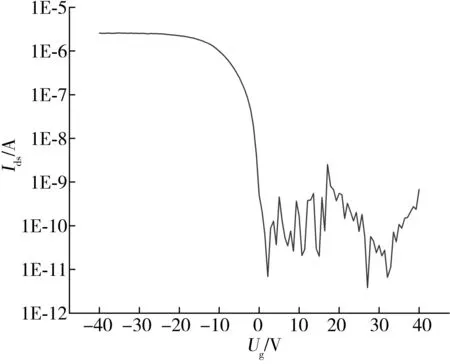

晶體管的轉(zhuǎn)移曲線如圖2所示,柵極電壓Ug在40~-40 V變化,源漏極電流Ids也隨之變化。Ug=2 V時(shí),Ids有明顯的上升趨勢(shì);至Ug=-35 V時(shí),Ids趨于穩(wěn)定,電流飽和,可以讀取到最大的開態(tài)電流。這個(gè)過程中,Ug=2 V被稱為閾值電壓或開啟電壓,是晶體管源漏極開始導(dǎo)通的一個(gè)臨界電壓值。

圖2 晶體管的轉(zhuǎn)移曲線Fig.2 Transistor transfer curve

浮柵型有機(jī)場(chǎng)效應(yīng)晶體管存儲(chǔ)器的工作原理為:柵極施加正電壓Ug> 0 V,使半導(dǎo)體層中部分激子分離成空穴與電子,電子受柵極電壓的影響,越過隧穿層進(jìn)入浮柵層,并被天然具有電子捕獲能力的CdSe@ZnS 量子點(diǎn)所捕捉[12]。撤去柵壓后,電子無法立刻回到半導(dǎo)體層,在浮柵層聚集形成一個(gè)內(nèi)建電場(chǎng),吸引半導(dǎo)體層中的空穴在隧穿層上表面聚集,逐漸形成高電導(dǎo)的溝道,存儲(chǔ)器溝道電流Ids呈高電平“1”,并且由于內(nèi)建電場(chǎng)持續(xù)存在,該高電平可以被保留一段時(shí)間。柵極施加負(fù)電壓Ug<0 V,則空穴被浮柵層捕獲,溝道電導(dǎo)下降,存儲(chǔ)器溝道電流Ids呈低電平“0”。

首先對(duì)存儲(chǔ)器的存儲(chǔ)窗口和開光比進(jìn)行測(cè)量。柵極正脈沖電壓:+40 V、2 s(編程電壓),晶體管閾值電壓增大,轉(zhuǎn)移曲線右移,在理想情況下Ug=0 V時(shí),讀取到開態(tài)電流Ion(“1”);柵極負(fù)脈沖電壓:-40 V、2 s(擦除電壓),晶體管閾值電壓減小,轉(zhuǎn)移曲線左移,此時(shí)在UG=0 V時(shí),可讀取關(guān)態(tài)電流Ioff(“0”)。

如圖3所示,在黑暗條件下,分別加?xùn)艠O電壓(±40 V、2 s)后,轉(zhuǎn)移曲線右偏趨勢(shì)弱,在Ug=0 V讀取的電流水平Ids較低,開關(guān)比Ion/Ioff=102,存儲(chǔ)窗口為30 V。而在200 mW/cm2、675 nm的紅光光源照射下[13],分別加?xùn)艠O電壓(±40 V、2 s)后,轉(zhuǎn)移曲線右移幅度增加,此時(shí)Ug=0 V,讀取到開關(guān)比Ion/Ioff≥104,存儲(chǔ)窗口為60 V,高低電平(“1”與“0”)區(qū)分度很高。

圖3 黑暗條件下與紅光照射下存儲(chǔ)器的編程態(tài)、擦除態(tài)的轉(zhuǎn)移曲線Fig.3 Transfer curve of programmed state and erased state of memory under dark condition and red light irradiation

根據(jù)以上分析可知,光照前后,晶體管的存儲(chǔ)窗口由30 V升至60 V,Ug=0 V讀取電壓下開關(guān)比相差20倍。并且一個(gè)場(chǎng)效應(yīng)晶體管上可以表達(dá)出3種邏輯電平,即675 nm紅光下的“1”、黑暗下的“中間態(tài)”和“0”,呈明顯的光可調(diào)制的邏輯狀態(tài)。

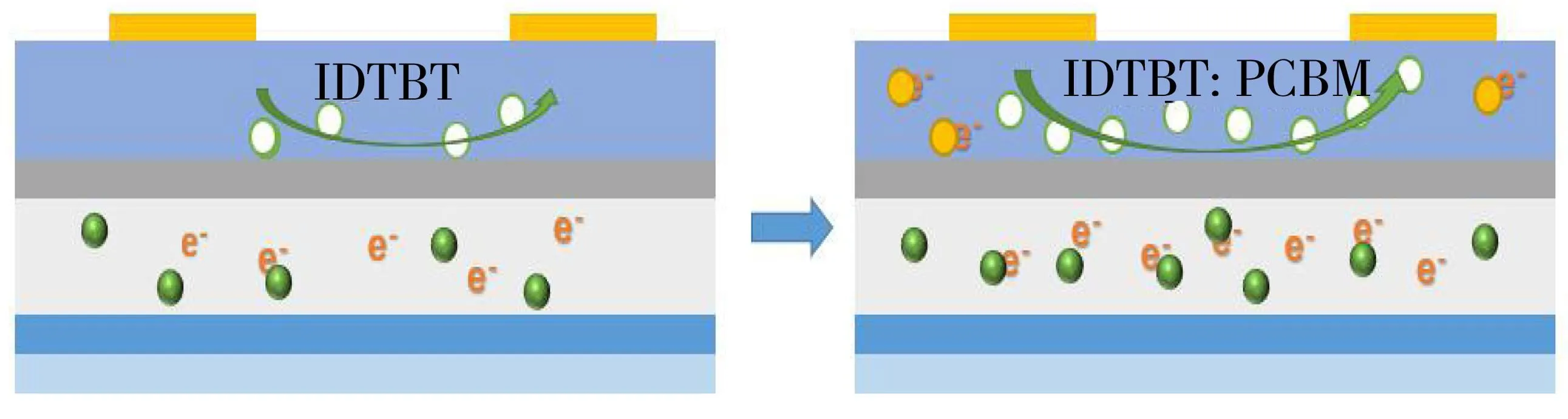

為驗(yàn)證PN共混半導(dǎo)體層的光電特性對(duì)提高器件開關(guān)比的作用,做了對(duì)照試驗(yàn)。第一種情況是僅IDTBT做半導(dǎo)體層的器件,UG=0 V時(shí),Ion/Ioff=103。第二種情況是用IDTBT與PCBM共混做有源層的器件,Ug=0 V時(shí),Ion/Ioff=104。兩種情況在0 V讀取下的電流開關(guān)比相差10倍,如圖4(a)所示。這一差距在線性度坐標(biāo)下更加明顯,如圖4(b)。因?yàn)镮DTBT混入少量PCBM后,兩種半導(dǎo)體材料能級(jí)不同,PCBM的低能級(jí)也能夠捕獲IDTBT的高能級(jí)電子[13~14],如圖4(a)所示。在紅光照射下施加正柵壓,更多的激子分離成空穴、電子,一部分電子進(jìn)入浮柵層,另一部分來不及被浮柵層捕獲的電子被半導(dǎo)體層中離散分布的PCBM捕獲[15],導(dǎo)致半導(dǎo)體層中產(chǎn)生更多的空穴,空穴溝道的電導(dǎo)進(jìn)一步提高,開態(tài)電流Ion增大,如圖5所示。因此PN共混半導(dǎo)體結(jié)構(gòu)的器件開關(guān)比會(huì)更大。

圖4 PN共混半導(dǎo)體層的光電特性對(duì)提高器件開關(guān)比的作用Fig.4 Effects of photoelectric properties of PN blend semiconductor layer on improving switching ratio of devices

圖5 IDTBT有源層與ITDBT∶PCBM=4∶1有源層下器件的導(dǎo)電溝道變化Fig.5 Change of conductive channel of devices under IDTBT active layer and ITDBT∶PCBM=4∶1 active layer

為了測(cè)試存儲(chǔ)器的信息保留時(shí)間,柵極施加編程+40 V電壓2 s后,保持Ug=0 V、源漏極Uds=-20 V 讀取存儲(chǔ)器的電平信號(hào),信號(hào)持續(xù)時(shí)間即信息的保持時(shí)間。加?xùn)艍汉? 000 s內(nèi)仍能維持穩(wěn)定高電平信號(hào),并且電平信號(hào)下降趨勢(shì)減緩,預(yù)估高電平信號(hào)可以至少維持10 000 s,如圖6所示。

圖6 存儲(chǔ)器的信息保持時(shí)間Fig.6 Information retention time of memory

4 總結(jié)與展望

本研究提出了一種可光調(diào)制的浮柵型場(chǎng)效應(yīng)薄膜晶體管存儲(chǔ)器,結(jié)合了有機(jī)材料與無機(jī)材料的優(yōu)勢(shì),使器件具有接近60 V的大存儲(chǔ)窗口,具備實(shí)現(xiàn)多級(jí)存儲(chǔ)器的潛力。

當(dāng)Ug為0 V時(shí),675 nm紅光下可讀取到開關(guān)比大于104的高電平信號(hào),黑暗條件下讀取的電平信號(hào)略有下降,開關(guān)比為102。器件表達(dá)出“1”“中間態(tài)”“0”3種具有明顯區(qū)分度的電平狀態(tài),有望實(shí)現(xiàn)三值邏輯存儲(chǔ),提高信息存儲(chǔ)密度。實(shí)驗(yàn)證明了PN共混結(jié)構(gòu)的半導(dǎo)體有源層(IDTBT:PCBM),比純IDTBT有源層結(jié)構(gòu),能更加有效提高存儲(chǔ)器的開關(guān)比,為改善薄膜晶體管存儲(chǔ)器的性能提供了一個(gè)新的思考方向。