一種具有多晶硅二極管柵極結構的槽柵IGBT 設計

王 波 ,胡汶金 ,趙一尚 ,李澤宏 ,任 敏

(1.川投信息產業集團有限公司,四川成都 610000;2.電子科技大學電子薄膜與集成器件國家重點實驗室,四川 成都 610054)

絕緣柵雙極型晶體管(IGBT)器件作為中高功率開關應用的關鍵半導體器件,受市場需求的影響,其一直朝著降低開關損耗、提高工作頻率和提高器件可靠性的方向發展[1-2]。在傳統槽柵IGBT 結構中,減小關斷損耗會造成器件正向導通壓降的提升,從而對器件的導通特性產生不利影響。隨著場截止技術和載流子存儲技術的發展,人們實現了對IGBT 正向導通壓降VCE(ON)與關斷損耗EOFF兩者矛盾關系的較好的優化[3]。而在優化器件開啟損耗EON的方向上,較高的開關速度雖然可以減小器件的開啟損耗,但同時會帶來較大的電流電壓振蕩,造成柵極電阻Rg無法較好地調控IGBT 的集電極電壓和電流的變化率(dVCE/dt和dICE/dt);同時受到IGBT 開啟速度的影響,電路中的續流二極管(Freewheel Diode,FWD)的反向恢復速度也隨之加快,導致FWD 反向恢復時的陽極電壓變化率dVKA/dt過大,進一步造成集電極電流和電壓的變化過快,最終在系統中引發較為嚴重的電磁干擾EMI 噪聲問題,對器件及應用系統的可靠性產生不利影響,這種情況在小電流應用環境中尤為明顯[4]。

EMI 噪聲的主要來源是開啟瞬態較高的dV/dt和dI/dt,而以上兩個參數主要受位移電流Idis的影響[5-7]。

式中:CGCOX1為柵極-集電極電容(密勒電容)的一部分;Vacc為槽柵周圍電勢;VGE為柵極電壓。當柵極附近的電勢變化速率dVacc/dt大于柵極電壓變化速率dVGE/dt時,位移電流Idis將會通過部分柵氧化層電容對柵極充電,使得實際參與充電的柵電流IG_eff=IG+Idis增大,進而導致dV/dt和dI/dt的不可控現象。

基于以上研究,業內對優化開啟損耗EON和電磁干擾噪聲EMI 噪聲之間的折中關系的主要方向為減小IGBT 的密勒電容CGC和槽柵附近電勢Vacc的變化率dVacc/dt。其中,減小密勒電容的主流思路是減小柵極與集電極之間的交疊面積,或直接實現密勒電容的減小,或是通過將柵極集電極電容轉換為柵極發射極電容以實現密勒電容的間接減小[8-13]。

基于此,本文在具有場截止層的傳統槽柵IGBT 結構的基礎上,提出了一種具有多晶硅二極管柵極結構的槽柵IGBT 結構(Poly Silicon Diodes Gate Structure for Trench Gate IGBT,PDG-TIGBT)。該結構通過在溝槽內部引入多晶硅二極管結構,使多晶硅二極管中低摻雜P 型Poly 柵極區域內形成的耗盡電容與原本的柵氧化層電容串聯實現更小的密勒電容,同時該耗盡電容的存在可提升開啟瞬態過程中的槽柵底部的電位,減小位移電流對柵極的影響,減小開啟過程中電壓和電流的過沖,增強柵極電阻Rg對dV/dt和dI/dt的控制能力,有效改善IGBT 開啟損耗和EMI 噪聲之間的折中關系。

1 器件結構和工作機理

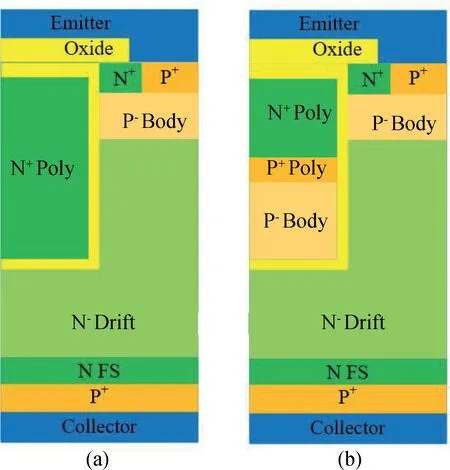

圖1(a)是場截止層槽柵IGBT(Trench Gate IGBT with Field-Stop Layer,FS-TIGBT)結構的橫截面圖,圖1(b)是本文所提的具有多晶硅二極管柵極結構的槽柵IGBT(PDG-TIGBT)的橫截面圖。PDG-TIGBT 與FSTIGBT 結構除槽柵結構外均保持一致。為實現PDGTIGBT 的柵極結構,在N+Poly 柵極和槽柵底部之間引入P+Poly 柵極和P-Poly 柵極,其中P+Poly 柵極主要作為N+Poly 柵極和P-Poly 柵極之間的緩沖結構,P-Poly柵極則用于實現多晶硅二極管結構,通過控制P-Poly柵極的摻雜濃度可以使該區域與IGBT 的漂移區區域相互耗盡形成耗盡電容,該耗盡電容一方面可以有效提升開啟瞬態過程中的槽柵底部的電位,另一方面與原本的柵氧化層電容串聯實現更小的密勒電容。

圖1 (a)FS-TIGBT 和(b)PDG-TIGBT 的結構橫截面圖Fig.1 The cross section of the (a) FS-TIGBT and (b) PDG-TIGBT

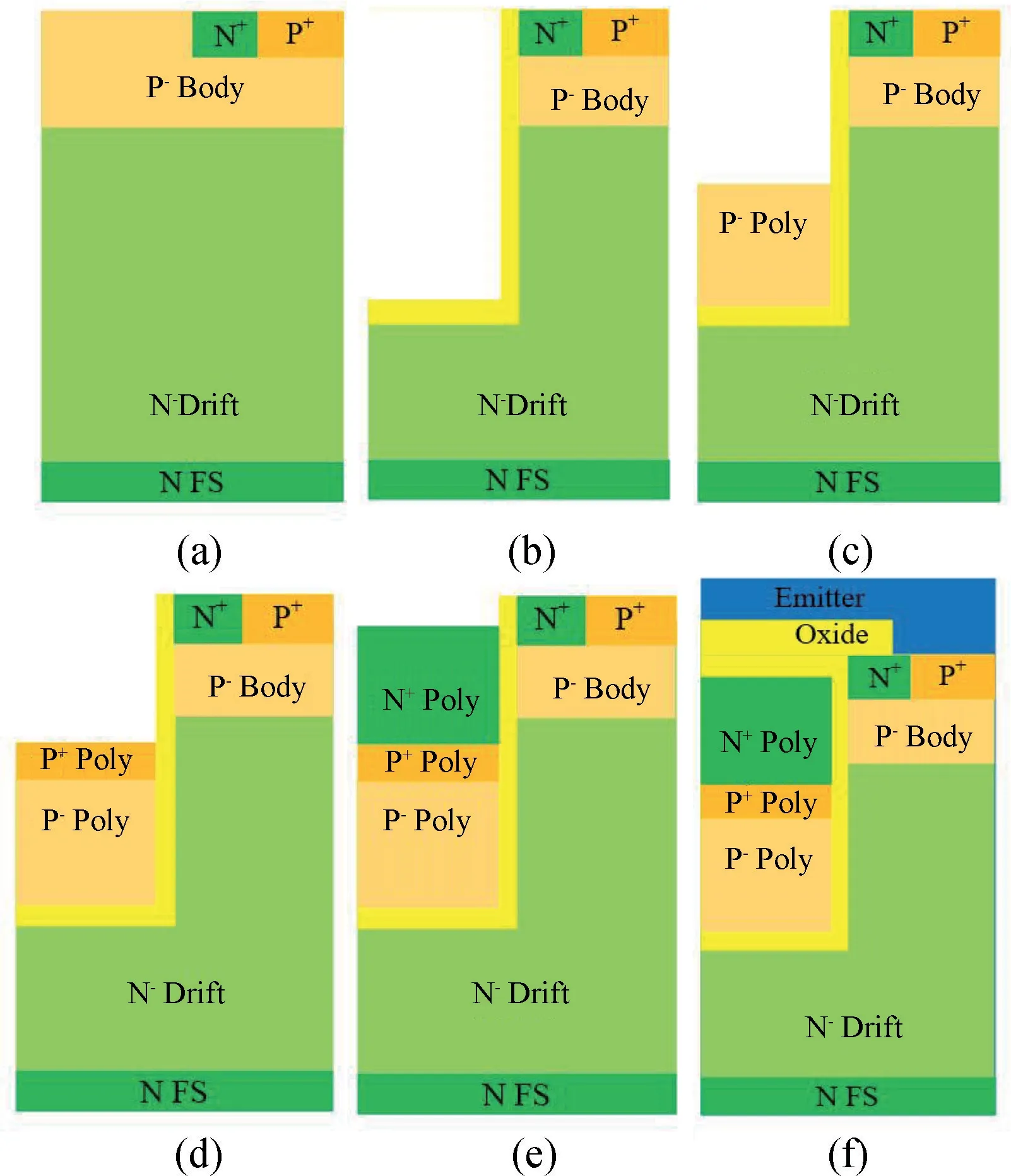

圖2 則展示了PDG-TIGBT 柵極結構的主要工藝制程的步驟。與傳統槽柵IGBT 柵極結構相比,PDGTIGBT 需要經過多次P--P+-N+多晶硅層的淀積與刻蝕以形成多晶硅二極管柵極結構。同時,與傳統槽柵IGBT 工藝不同的是,為了避免IGBT 其他區域推結、退火、介質層形成等工藝的熱過程對P-Poly 柵極摻雜造成影響,本次工藝制程將溝槽的刻蝕、柵氧化層的生長以及Poly 柵極的淀積與摻雜過程安排在場限環、P 型基區、N 型發射區以及P 型接觸區的推結過程之后。圖2(a)為PDG-TIGBT 的主要摻雜區域如N 型FS 層、N-漂移區、P 型基區、N+發射區和P+接觸區的形成結果示意圖,其中N 型FS 層作為整個結構的襯底,而N-漂移區采用外延工藝實現。接下來,如圖2(b)所示,實現槽柵結構中溝槽的刻蝕和柵氧化層的淀積。下一步則用于實現槽柵內部的多晶硅二極管結構,如圖2(c)、(d)和(e)所示,進行P-Poly柵極、P+Poly 柵極和N+Poly 柵極的淀積與刻蝕。最后進行BPSG 介質層的淀積與刻蝕工藝、器件表面的金屬化工藝,如圖2(f)所示。經過以上幾個工藝步驟,PDG-TIGBT 中包含多晶硅二極管柵極結構的正面結構已完全實現。

圖2 PDG-TIGBT 柵極結構的主要工藝設計步驟。(a)N 型FS 層、N-漂移區、P 型基區、N+發射區和P+接觸區的形成;(b)槽柵的刻蝕和柵氧化層的淀積;(c)P-Poly 柵極的淀積與刻蝕;(d)P+Poly 柵極的淀積與刻蝕;(e)N+Poly 柵極的淀積與刻蝕;(f)BPSG 介質層與金屬的淀積與刻蝕Fig.2 The major process design of the PDG-TIGBT gate structure.(a) Formation of N FS-layer,N- drift,P-base,N+ emitter and P+ contact;(b) Trench etching and oxide deposition;(c) PPoly deposition and etching;(d) P+ Poly deposition and etching;(e) N+ Poly deposition and etching;(f) BPSG and metal deposition and etching

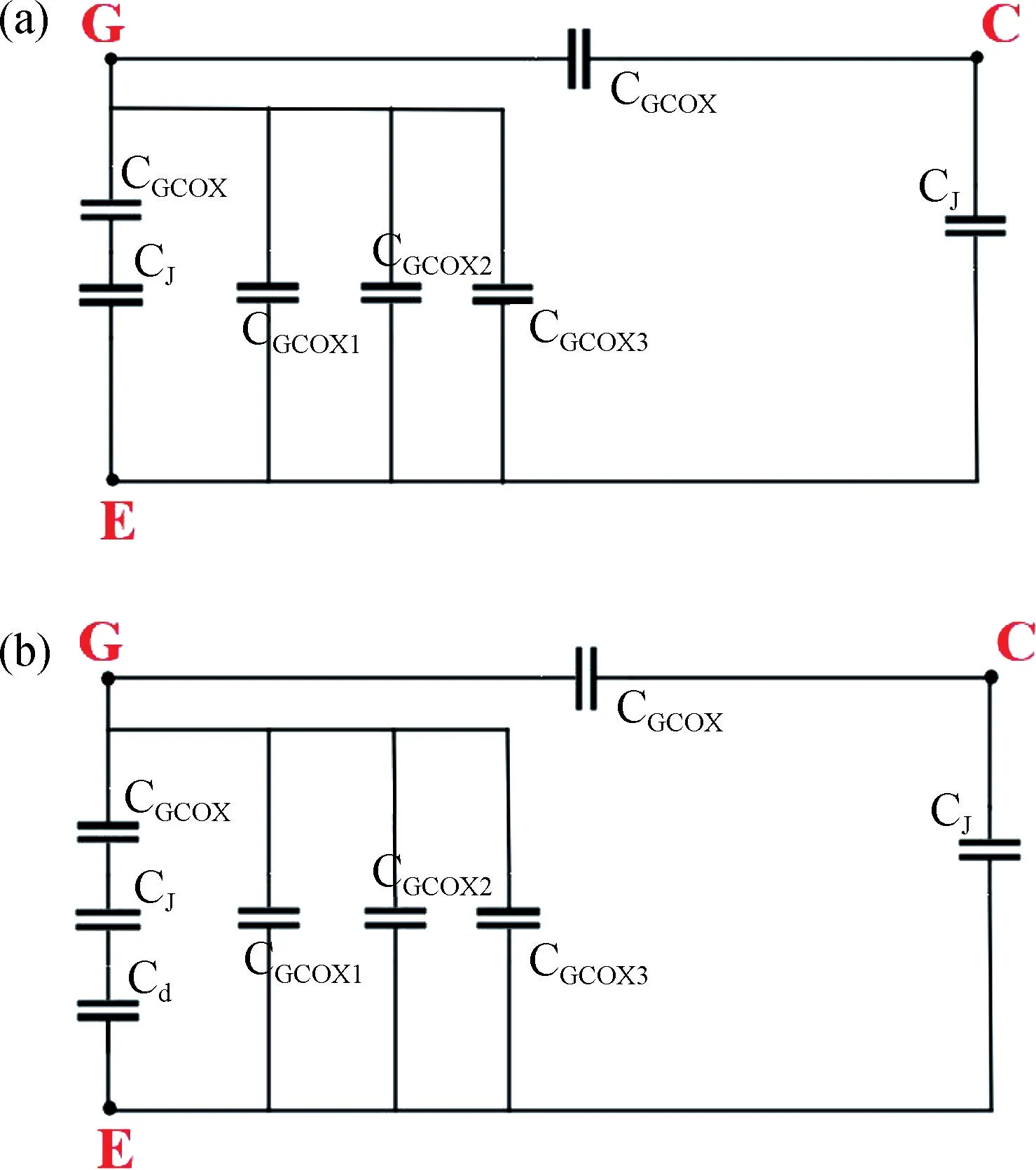

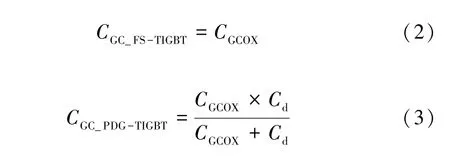

圖3 為簡化后的兩種結構的電容等效電路示意圖。由圖3(a)可知,傳統FS-TIGBT 的密勒電容僅由柵極與N-漂移區之間的半導體電容CGCOX組成。而由圖3(b)可知,本文所提的PDG-TIGBT 結構的密勒電容受到P-Poly 硅柵與N-漂移區之間的耗盡電容的影響可大幅度減小,密勒電容由耗盡電容Cd與CGCOX串聯組成。FS-TIGBT 和PDG-TIGBT 兩種結構的密勒電容的表達式為:

圖3 (a)FS-TIGBT 和(b)PDG-TIGBT 電容等效電路Fig.3 The capacitances network of the (a) FS-TIGBT and (b) PDG-TIGBT

Cd的存在可大幅度減小PDG-TIGBT 的密勒電容,通過調節P-Poly 柵極的摻雜改變耗盡電容Cd的大小,從而進一步實現對密勒電容和槽柵附近電勢的優化。該結構在密勒電容上的優化一方面可以加快器件的開關速度,減小IGBT 的開關損耗;另一方面,減小密勒電容可以有效減小器件的位移電流Idis,從而減小位移電流對柵極驅動的影響。同時,本結構中的耗盡電容Cd可有效提升槽柵附近的電勢Vacc,由于槽柵附近的電勢Vacc初始值Vfix會強烈影響開啟時的dICE/dt,Vfix越大,空穴在槽柵附近積累的數量越少,致使槽柵附近電勢Vacc增長速率變緩,即dVacc/dt減小,從而可以有效減小位移電流Idis對槽柵的影響,減小開啟過程中器件的dV/dt和dI/dt,抑制器件的EMI 噪聲,實現IGBT的EMI 噪聲與開啟損耗EON折中關系的進一步優化。

2 結構仿真與數據分析

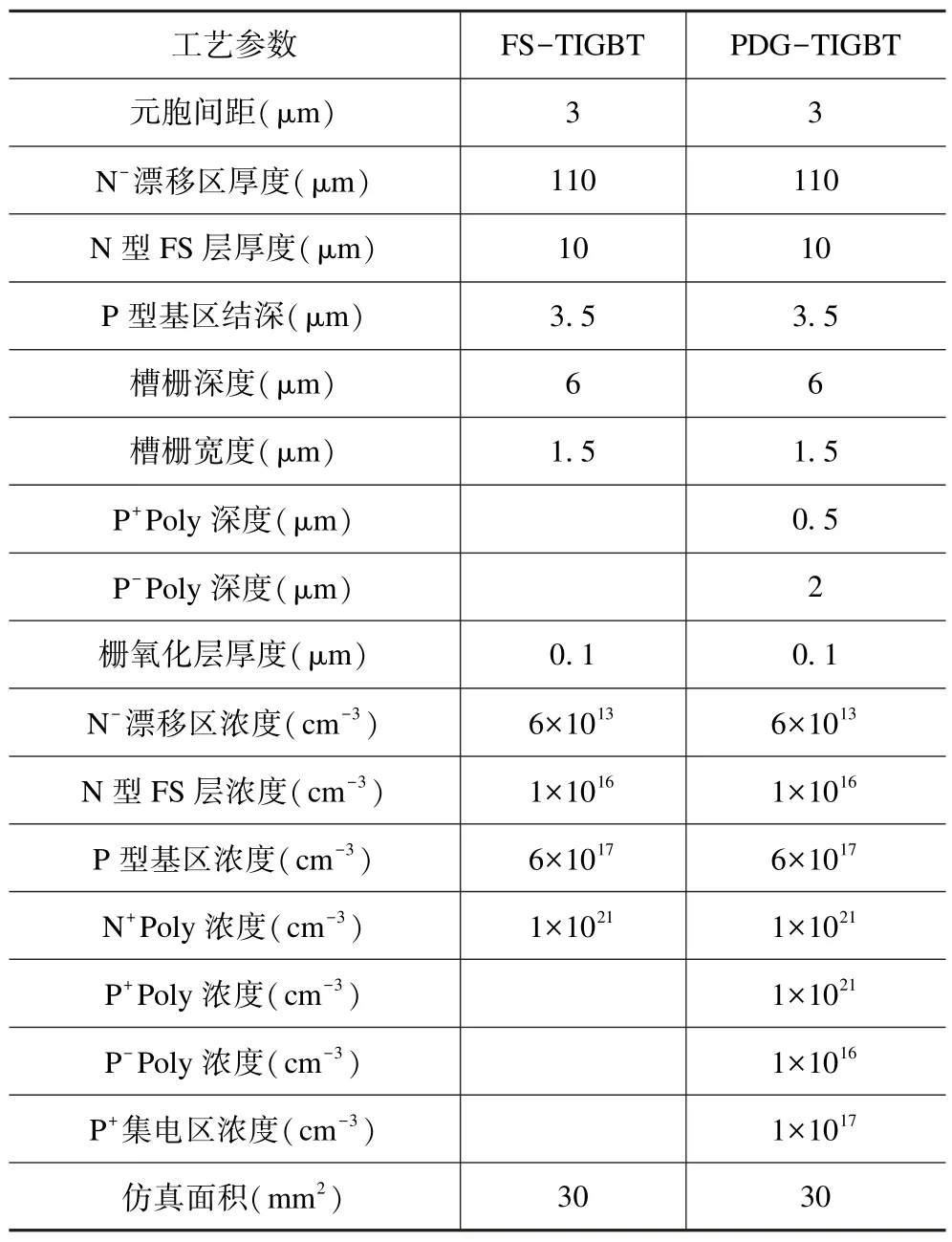

為驗證所提PDG-TIGBT 結構在開啟損耗EON與EMI 噪聲兩者折中關系上的優化,本文利用Sentaurus仿真軟件對FS-TIGBT 和PDG-TIGBT 兩種結構進行靜態特性和動態特性的對比仿真,重點分析兩種結構在密勒電容及開關特性上的區別。兩種結構的關鍵結構參數如表1 所列。

表1 FS-TIGBT 和PDG-TIGBT 結構的關鍵工藝參數Tab.1 Key process parameters of FS-TIGBT and PDG-TIGBT

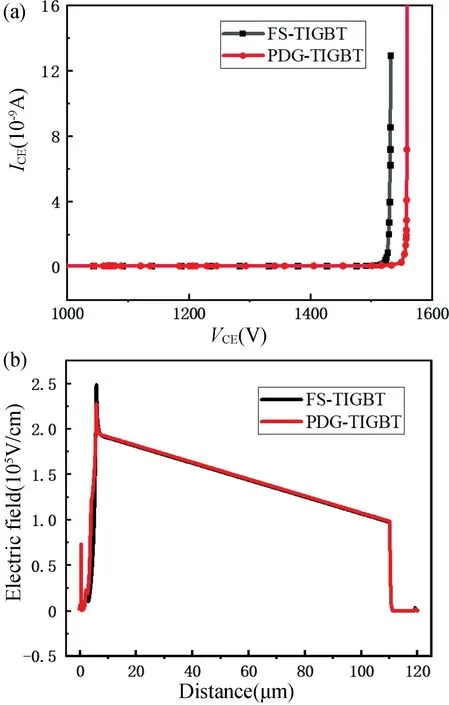

圖4 為兩種結構正向阻斷特性的對比圖,其中圖4(a)為兩種結構在相同結構參數下的正向阻斷電壓仿真結果,圖4(b)為兩種結構在正向阻斷狀態下沿槽柵側壁的電場分布對比示意圖。由圖可知,PDG-TIGBT 的擊穿電壓略高于FS-TIGBT,同時兩種結構的電場峰值均位于槽柵底部拐角處,且FS-TIGBT 結構的電場峰值略大于PDG-TIGBT 電場峰值。該現象的主要原因是在器件的正向阻斷過程中,由于PDG-TIGBT 中P-Poly柵極與N-漂移區之間形成耗盡區域,使漂移區內的電場得到進一步的優化,但P-Poly 不同于與發射極相連的屏蔽柵極,該結構僅能較小幅度優化漂移區內的電場分布,實現對阻斷能力的小幅度提升。

圖4 FS-TIGBT 和PDG-TIGBT 的(a)擊穿電壓曲線和(b)沿槽柵側壁的電場分布Fig.4 (a) BVs and (b) electric field along trench gate sidewall of FS-TIGBT and PDG-TIGBT

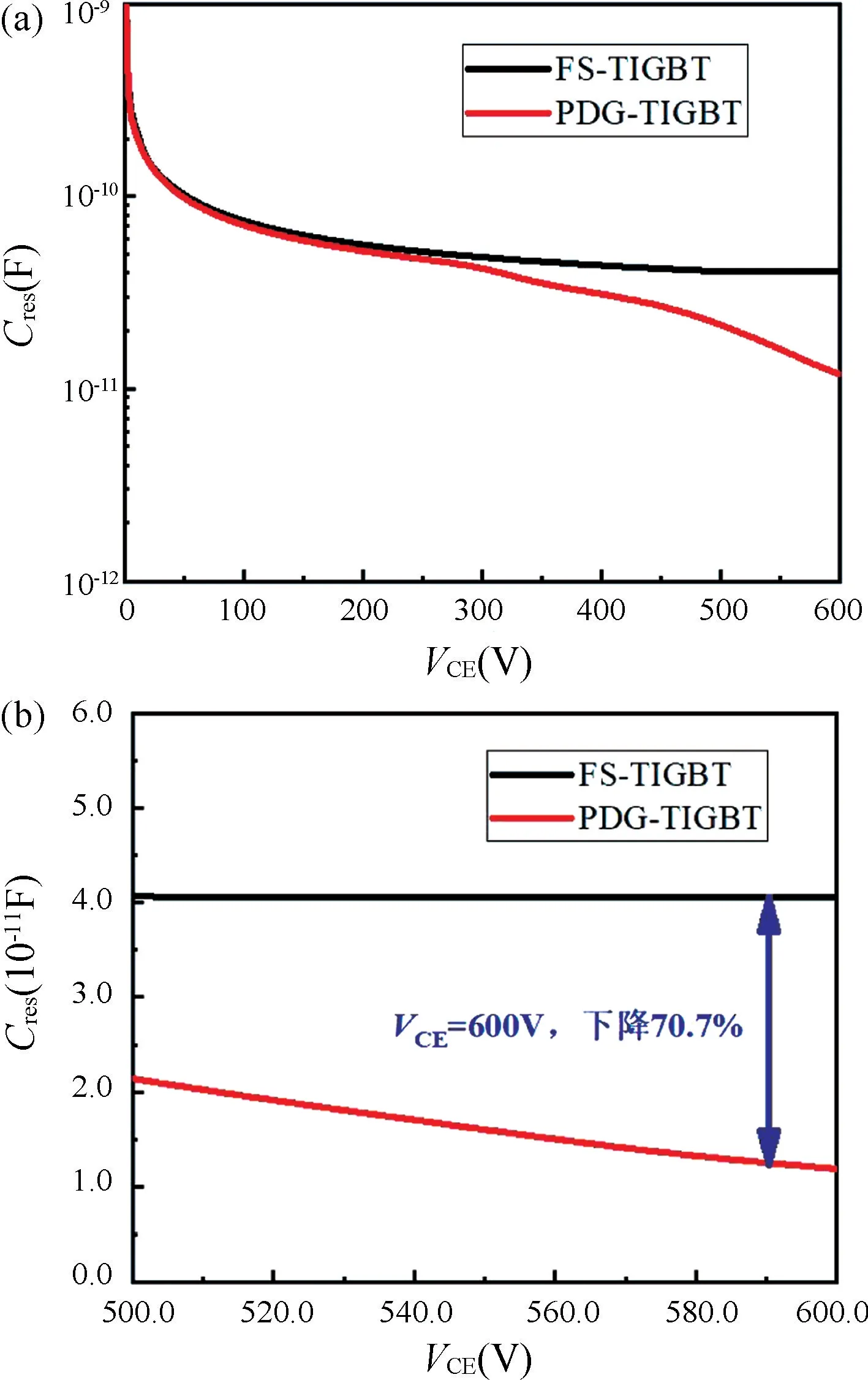

由于PDG-TIGBT 結構中引入的P-Poly 硅柵與N-漂移區之間在高集電極電壓下形成耗盡電容Cd,該電容與原本柵極附近的半導體電容CGCOX串聯使結構的密勒電容大幅度降低。圖5 為兩種結構密勒電容隨集電極電壓VCE變化曲線的對比示意圖,從圖中可以看出,PDG-TIGBT 在0~600 V 的集電極電壓范圍內均小于FS-TIGBT,在小集電極電壓范圍內改善較小,在大集電極電壓范圍內改善較為明顯。其中,在集電極電壓為600 V 時,FS-TIGBT 密勒電容為40.9 pF,PDGTIGBT 密勒電容僅為11.98 pF,本文所提結構的密勒電容減小了70.7%。大集電極電壓下密勒電容的大幅度減小可以有效改善開關過程中位移電流對柵極驅動的影響,同時可以有效減小器件的開啟損耗,具體的量化效果將由開關特性的仿真結果展示。

圖5 (a)兩種結構密勒電容隨集電極電壓變化曲線;(b)高集電極電壓下兩種結構密勒電容大小對比Fig.5 (a) Miller capacitance CGC versus VCE;(b) Comparison of Miller capacitance CGC of FS-TIGBT and PDG-TIGBT at high collector voltage

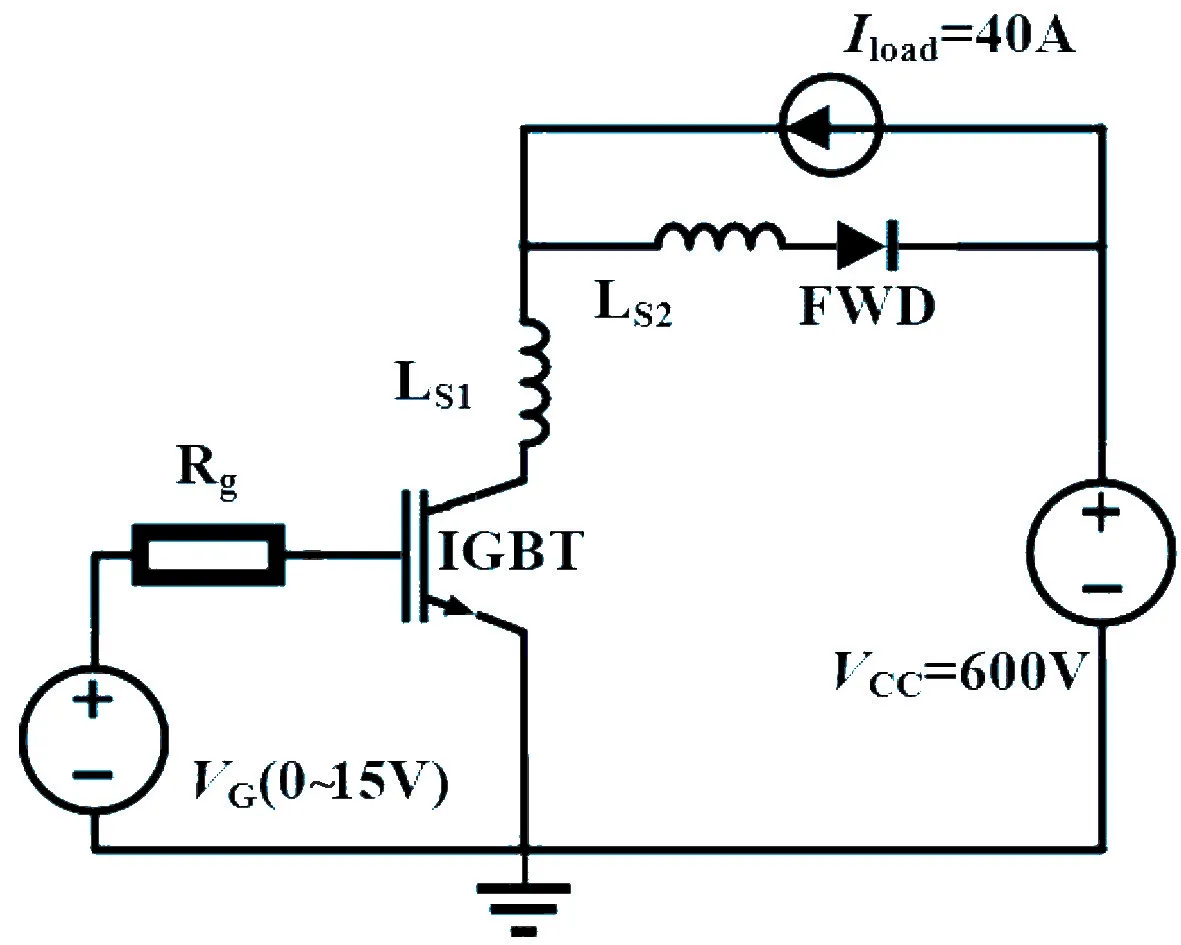

接下來重點分析PDG-TIGBT 對EMI 噪聲與開啟損耗EON折中關系的改善效果。圖6 所示為IGBT 開啟特性仿真所采用的感性負載仿真電路,其中負載電流源Iload為40 A,電源電壓VCC為600 V,柵極電壓范圍是0~15 V,柵極電阻Rg為80 Ω,雜散電感LS1和LS2的值分別為50 nH 和30 nH。電路選取硅基的PIN 二極管作為續流二極管FWD,并設置IGBT 與FWD 的面積之比為2 ∶1。

圖6 IGBT 感性負載開關電路Fig.6 Circuit schematic with inductive load for IGBT transient turn on analysis

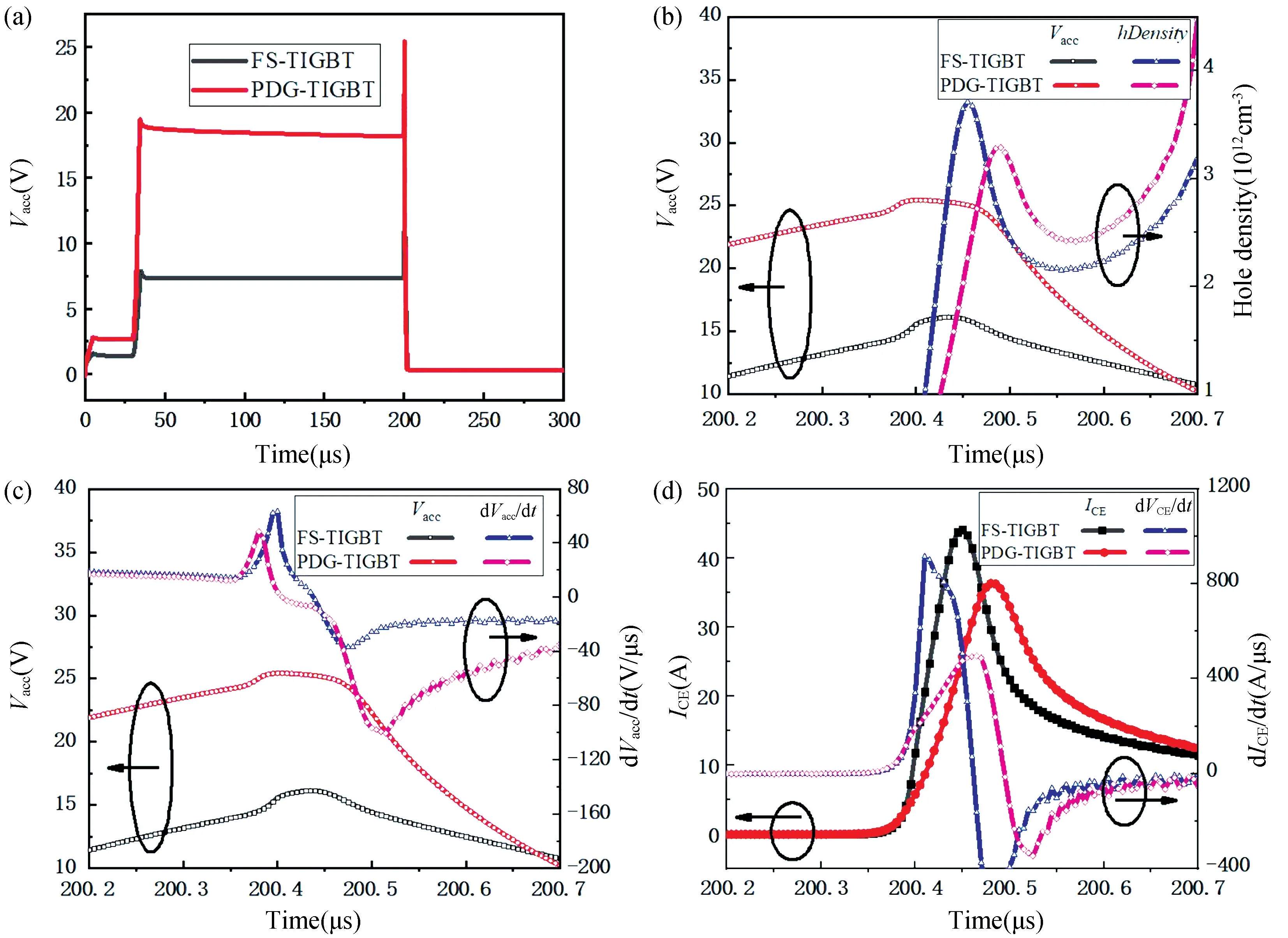

圖7 為柵極電阻Rg為80 Ω、負載電流為0.1 倍率的額定電流即Iload為4 A 時,采用如圖6 所示的開關電路對FS-TIGBT 和PDG-TIGBT 兩種結構進行開啟特性及EMI 噪聲相關特性的仿真分析。圖7(a)顯示了兩種結構在開啟過程中槽柵底部電勢Vacc的變化,如圖所示,PDG-TIGBT 結構受耗盡電容Cd的影響有效抬升了槽柵底部電勢Vacc。圖7(b)和(c)則展示了槽柵底部空穴濃度和電勢變化率dVacc/dt的波形對比曲線,PDG-TIGBT 結構中Vacc電位的提升使更少的空穴聚集在槽柵附近,從而可以有效減小Vacc的增長速率dVacc/dt。圖7(d)通過對比兩種結構集電極電流及其變化率的變化曲線進一步展示了PDG-TIGBT 結構在EMI 噪聲特性上的優化,如圖所示,PDG-TIGBT 結構有效抑制了集電極電流ICE的過沖,并實現了更小的集電極電流變化率dICE/dt。通過對圖7 分析可得,由于密勒電容在集電極電壓VCE為600 V 時減小70.7%,dVacc/dt最大值從63.4 V/μs 下降到48.5 V/μs,即dVacc/dt(max)減小了23.5%,從而實現了最大dICE/dt從914.4 A/μs 下降到495.9 A/μs,使dICE/dt(max)減小45.8%,同時將ICE過沖由44.1 A 抑制到36.3 A。

圖7 小電流下兩種結構開啟特性對比。(a) Vacc開啟波形對比;(b) Vacc和槽柵底部空穴濃度開啟波形對比;(c) Vacc和dVacc/dt 開啟波形對比;(d)ICE和dICE/dt 開啟波形對比Fig.7 Comparison of turn on characteristics of two structures at small current.(a) Comparison of Vacc during turn on period;(b) Comparison of Vacc and hole density at the bottom of trench gate;(c) Comparison of Vacc and dVacc/dt;(d) Comparison of ICE and dICE/dt

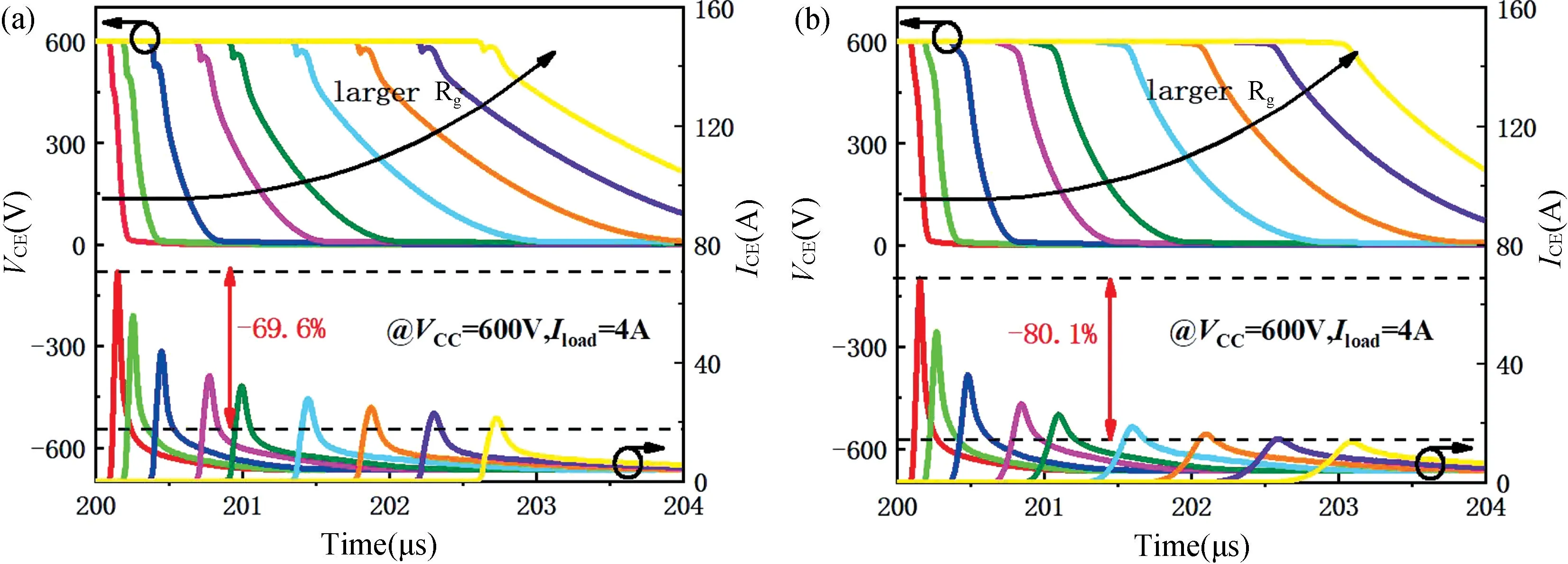

圖8 對比了負載電流為0.1 倍率的額定電流即Iload為4 A 時,不同柵極電阻Rg下的FS-TIGBT 和PDGTIGBT 兩種結構集電極電壓VCE和集電極電流ICE的變化曲線,其中Rg取值范圍為20~600 Ω。從圖中可以看出,不同Rg下的PDG-TIGBT 的集電極電流ICE峰值均低于FS-TIGBT,且隨著Rg的增大,PDG-TIGBT 結構下的VCE和ICE的相應變換趨勢比FS-TIGBT 的更為明顯,即PDG-TIGBT 結構下的VCE和ICE對Rg的變換更為敏感,具有更高的dICE/dt和dVCE/dt的可控性。

圖8 1/10 額定電流下不同Rg(20~600 Ω)下(a)FS-TIGBT 和(b)PDG-TIGT 的開啟特性曲線對比Fig.8 Simulated turn-on characteristics of (a) FS-TIGBT and the (b) PDG-TIGBT with various Rg(20-600 Ω) at 1/10 rated current

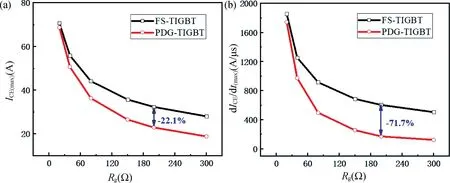

圖9 則進一步詳細地展示了小電流下兩種結構的集電極電流峰值ICE(max)及集電極電流變化率最大值dICE/dt(max)隨柵極電阻Rg的變化關系。在20~300 Ω 的典型柵極電阻仿真范圍內,相同Rg下PDG-TIGBT 的集電極最大電流ICE(max)平均下降22.1%,集電極電流變化率最大值dICE/dt(max)平均下降71.7%,展現出更強的電流可控性。

圖9 (a)Rg-ICE(max)和(b)Rg-dICE/dt(max)的開啟特性折中曲線對比Fig.9 Turn-on trade-off relationships between (a) Rg and ICE(max),(b) Rg and dICE/dt(max) at 1/10 rated current

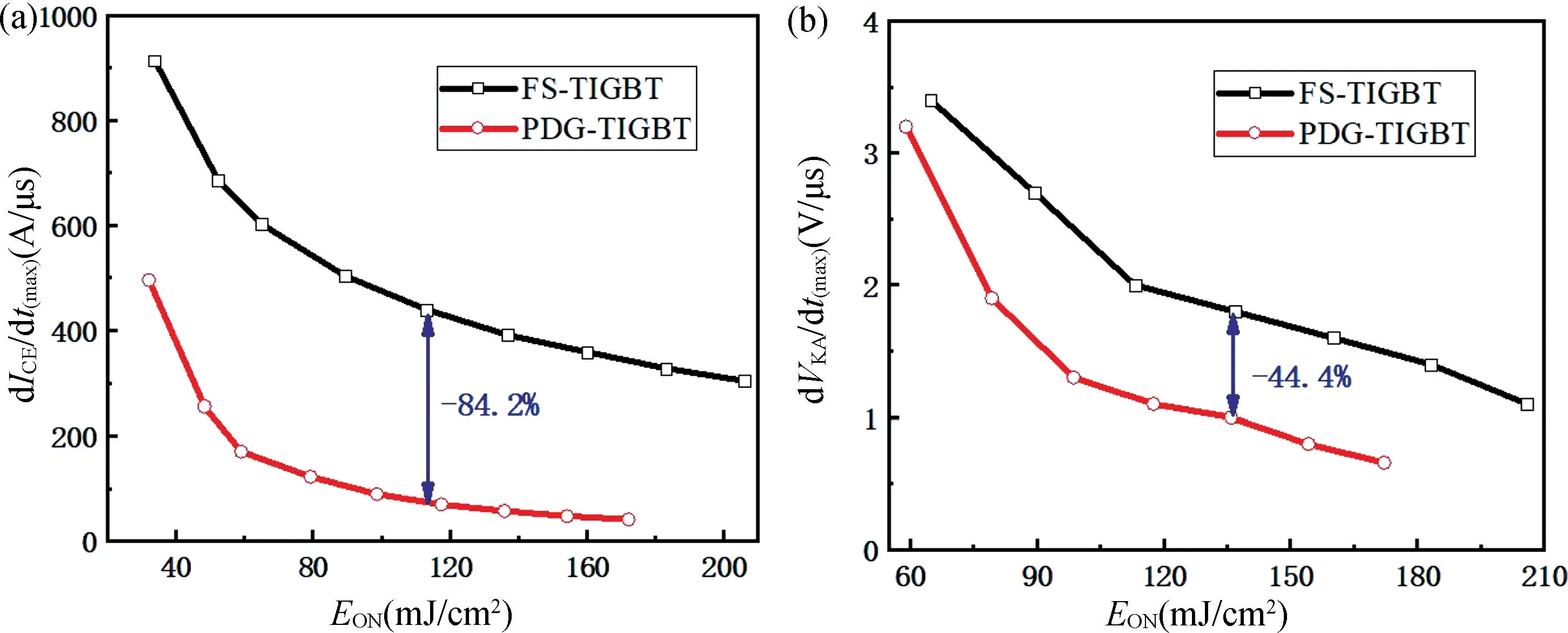

圖10 為開啟損耗EON與續流二極管反向恢復時的陽極電壓變化率最大值dVKA/dt(max)、開啟過程中dICE/dt發生震蕩時的最大值dICE/dt(max)之間的折中曲線示意圖,兩種折中曲線示意圖可以較為量化地展示電磁干擾噪聲EMI 與開啟特性之間的折中關系。其中dICE/dt(max)、dVKA/dt(max)等EMI 噪聲相關參數均在0.1倍率的負載電流4 A 下進行仿真,EON則是在額定負載電流40 A 下進行仿真。圖10(a)為兩種結構的開啟損耗EON與集電極電流變化率最大值dICE/dt(max)的折中曲線對比,從圖中可以看出,在相同的EON條件下,PDG-TIGBT 對應的dICE/dt(max)相比傳統的FS-TIGBT結構減小了84.2%。同時,從圖10(b)所示的開啟損耗EON與續流二極管FWD 反向恢復電壓最大值dVKA/dt(max)的折中曲線對比圖中可以看到,在EON保持一致的前提下,PDG-TIGBT 的dVKA/dt(max)下降了44.4%。由上面描述可知,與傳統的FS-TIGBT 結構相比,所提PDG-TIGBT 結構在一定程度上優化了dICE/dt、dVKA/dt與EON之間的折中關系,有效地改善了器件開啟特性與EMI 噪聲特性之間的矛盾關系。

圖10 (a)EON-dICE/dt(max)和(b)EON-dVKA/dt(max)的折中曲線對比Fig.10 Trade-off relationships between (a) EON and dICE/dt(max),(b) EON and dVKA/dt(max)

3 結論

本文提出了一種可有效改善IGBT 的開啟損耗EON和EMI 噪聲折中關系的具有多晶硅二極管柵極結構的槽柵IGBT(PDG-TIGBT)結構,并基于傳統槽柵IGBT工藝提出了適用于所提結構的工藝制程。對比于傳統FS-TIGBT 結構,在柵極電阻Rg為80 Ω、集電極電壓VCE為600 V 的仿真條件下,所提PDG-TIGBT 結構的密勒電容CGC比FS-TIGBT 降低了70.7%,槽柵底部電位Vacc則抬升了約146%。

基于耗盡電容Cd導致的密勒電容CGC的減小及槽柵底部電位Vacc的抬升,PDG-TIGBT 可以有效抑制位移電流的產生。仿真結果顯示,在開啟瞬態槽柵底部電位增長速度dVacc/dt減小23.5%,集電極電流變化速率dICE/dt(max)減小45.8%,ICE過沖由44.1 A 抑制到36.3 A。同時,通過仿真不同柵極電阻Rg下的兩種結構的開啟特性曲線發現,PDG-TIGBT 結構的集電極電壓VCE和集電極電流ICE對柵極電阻Rg的變化更為敏感,即具有更高的dICE/dt和dVCE/dt可控性。更重要的是,PDG-TIGBT 結構實現了開啟損耗EON與EMI噪聲折中關系的進一步優化,仿真結果顯示,在EON保持一致的前提下,PDG-TIGBT 的dICE/dt(max)減小了84.2%,dVKA/dt(max)下降了44.4%。