基于FPGA的Camera Link接口設計

任麗曄,汪 晨

(長春大學 電子信息工程學院,長春 130022)

隨著工業相機的發展,為了配合高速、實時數據量的處理與傳輸,其對圖像接口的要求也變得越來越高。目前,最快的一種工業相機輸出接口是Camera Link接口[1]。Camera Link協議是一種專門針對機器視覺應用領域的串行通信協議,Camera Link標準中有6對差分信號線,其中4對用于并行傳輸相機控制信號,另外2對用于相機和圖像采集卡之間的串行通信[2]。

FPGA開發所使用的硬件描述語言為Verilog HDL/VHDL,其獨特的硬件結構和并行處理優勢可以大大加強傳輸系統的實時性[3]。本研究基于FPGA實現了Camera Link接口的方法,通過Camera Link接口把實時圖像傳輸到FPGA圖像采集卡中進行數據實時處理,并實現采集卡和計算機之間的通信。

1 Camera Link設計方案

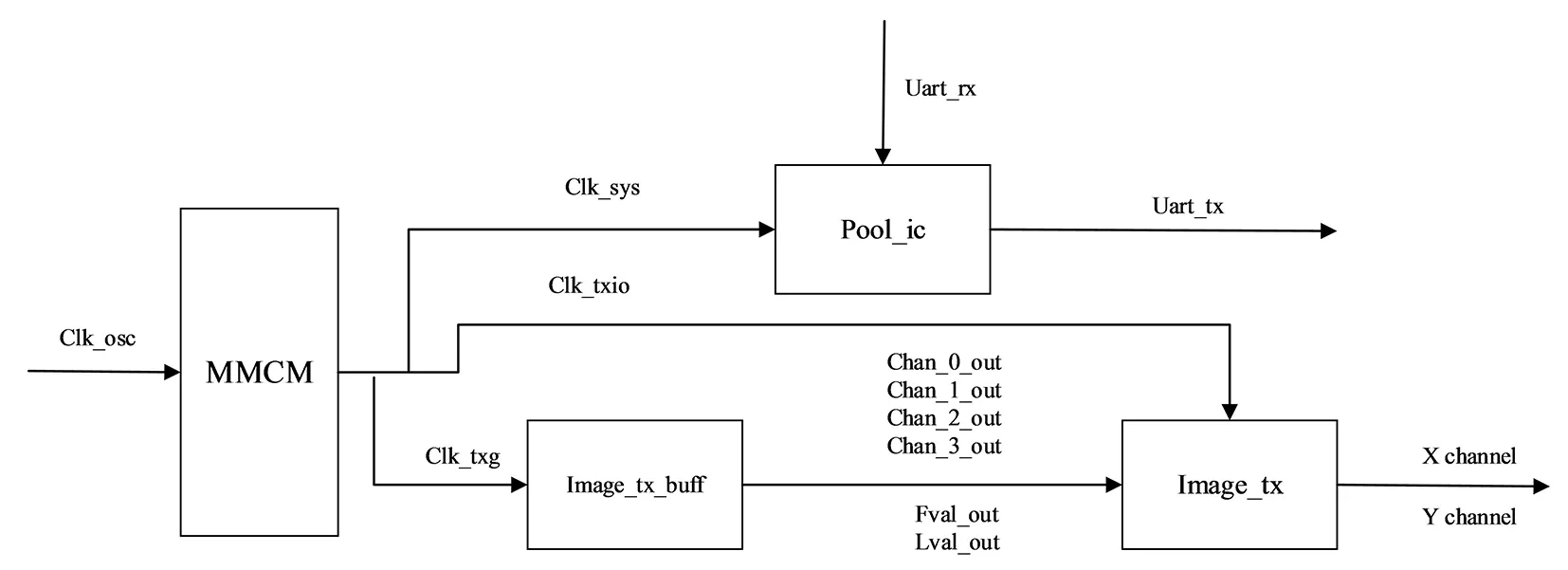

設計基于主控芯片Spartan-7系列的FPGA芯片。相較于之前的芯片,Spartan-7有更高邏輯與IO比,性能更強,也降低了功耗。使用MMCM原語對時鐘進行分頻和倍頻,分別作為圖像傳輸和通信串口的時鐘輸入。設置圖像傳輸模塊,分為4個通道進行傳輸,像素為3 000*3 000,在每一次的行信號lval_out下,傳輸1 250個。最后由圖像的發送端接收信號后,發送兩個通道的信號。設置串口通信的模塊,由PC端發送5個不同的16進制數,通過串口返回另外5個16進制數。最后實現所有的功能,其具體的流程FPGA模塊框圖如圖1所示。

圖1 FPGA模塊框圖

根據傳輸的位數,選擇使用Camera Link基本模式,即Base模式。總線發送端將28位并行數據轉換為4對LVDS串行差分數據傳送出去,運用 LVDS 串行差分數據線傳輸圖像數據輸出同步時鐘;總線接收端將串行差分數據轉換成28位并行數據,同時轉換出同步時鐘。由于采用串行差分傳輸方式,既減少傳輸線的使用量,又減少傳輸過程中的電磁干擾。

2 邏輯設計

2.1 時鐘分頻

MMCM是混合模擬時鐘管理器,有強大的時鐘管理功能,其具體功能分別為時鐘去歪斜、基于整數分頻器的數字效率合成、基于小數分頻器的數字頻率合成、抖動濾波器和相移。MMCM_BASE是基本時鐘管理模塊的原語,例化原語可以實現MMCM的基本功能,調用全局時鐘資源[4]。

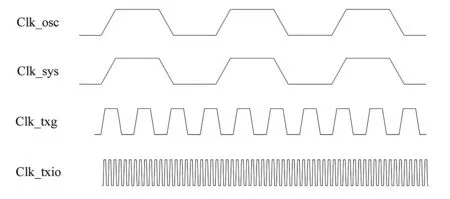

由于FPGA輸入的系統時鐘clk_osc為50 MHz,所以,MMCM_BASE原語的邏輯功能是以50 MHz時鐘信號為基數進行分頻和倍頻,考慮整個模塊的時序與邏輯,對串口通信選擇使用50 MHz的時鐘輸入clk_sys,圖像傳輸選擇使用210 MHz的時鐘輸入clk_txg。圖像輸出的模塊需要2個時鐘,其中clk_txio時鐘的大小是clk_txg時鐘的7倍。像素時鐘 clk_txg首先經過延時模塊平衡7位數據深度的延時后輸入MMCM,通過數據和時鐘解串輸出clk_txio,所以時鐘大小為1 470 MHz。這種時鐘輸入的方式可以保持其相位相同,以便于更好的分析。MMCM時鐘的時序圖如圖2所示。

圖2 MMCM時鐘時序圖

2.2 圖像傳輸

圖像的傳輸是Camera Link接口中最重要的部分。Camera Link標準使用4對LVDS線纜用來實現相機的控制,它們被定義為相機的輸入信號和圖像采集卡的輸出信號,完整的Camera Link接口包含著發送端和接收端[5-6]。

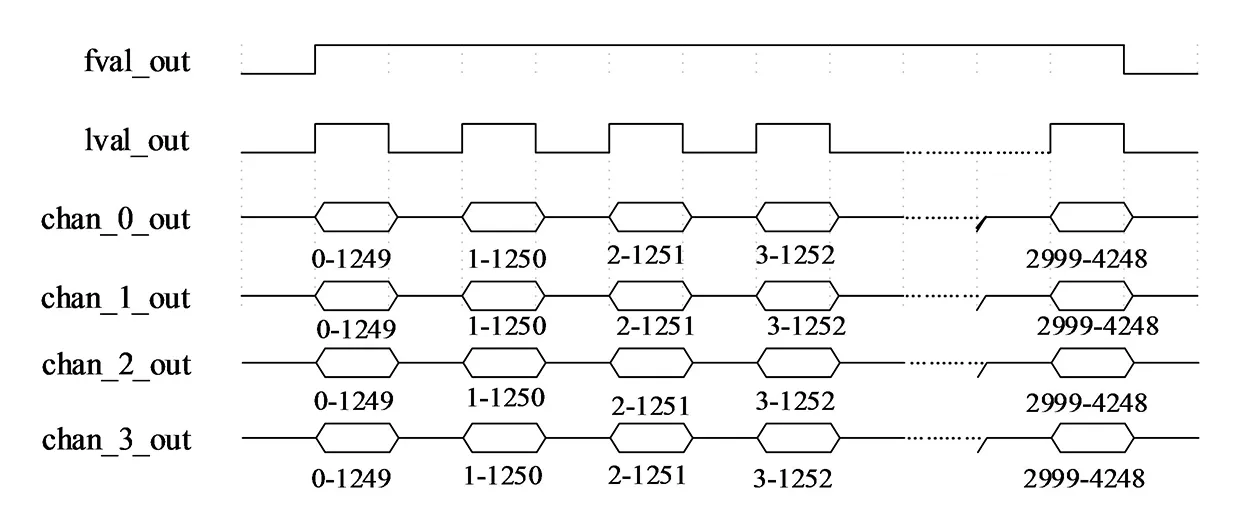

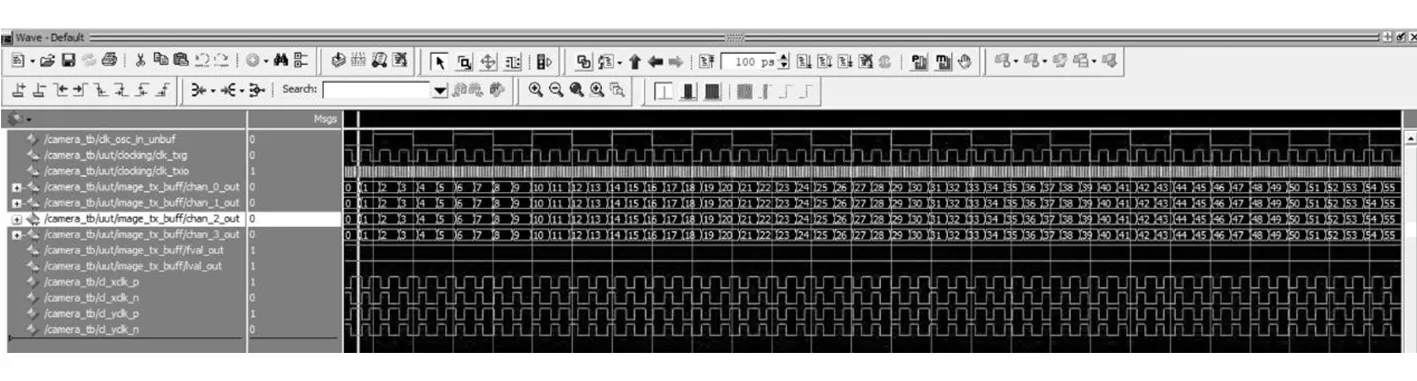

利用image_tx_buff模塊發送相機的有效數據,共有4個通道chan_0_out、chan_1_out、chan_2_out、chan_3_out同時發送像素。當發送新的一幀數據時拉高fval_out場信號,代表一幀數據的開始;拉低fval_out場信號即代表一幀數據的結束。lval_out行信號代表一行的有效數據,一行的有效數據為1 250個,為了不互相干擾,設置每行信號之間間隔50個時鐘周期。當所有像素傳輸完后,同時拉低場信號和行信號,繼續等待500個時鐘周期后進行下一幅圖的傳輸。為了間隔時鐘周期的正確性,分別添加計數器進行計數,每次計數完畢后對計數器進行清零,否則會造成程序的混亂。圖像發送數據的時序圖如圖3所示,0~1 249代表的是一行中傳輸的數據,下一行則從1開始。對于Camera Link標準中的數據有效信號DVAL,只有當場信號和行信號都為高電平時,拉高DVAL信號則代表數據是有效的。利用FPGA直接生成信號,輸出圖像這種方式,考慮到了FPGA的現場可編程特性,使用靈活方便,并且能夠降低硬件電路設計難度。

圖3 圖像數據時序圖

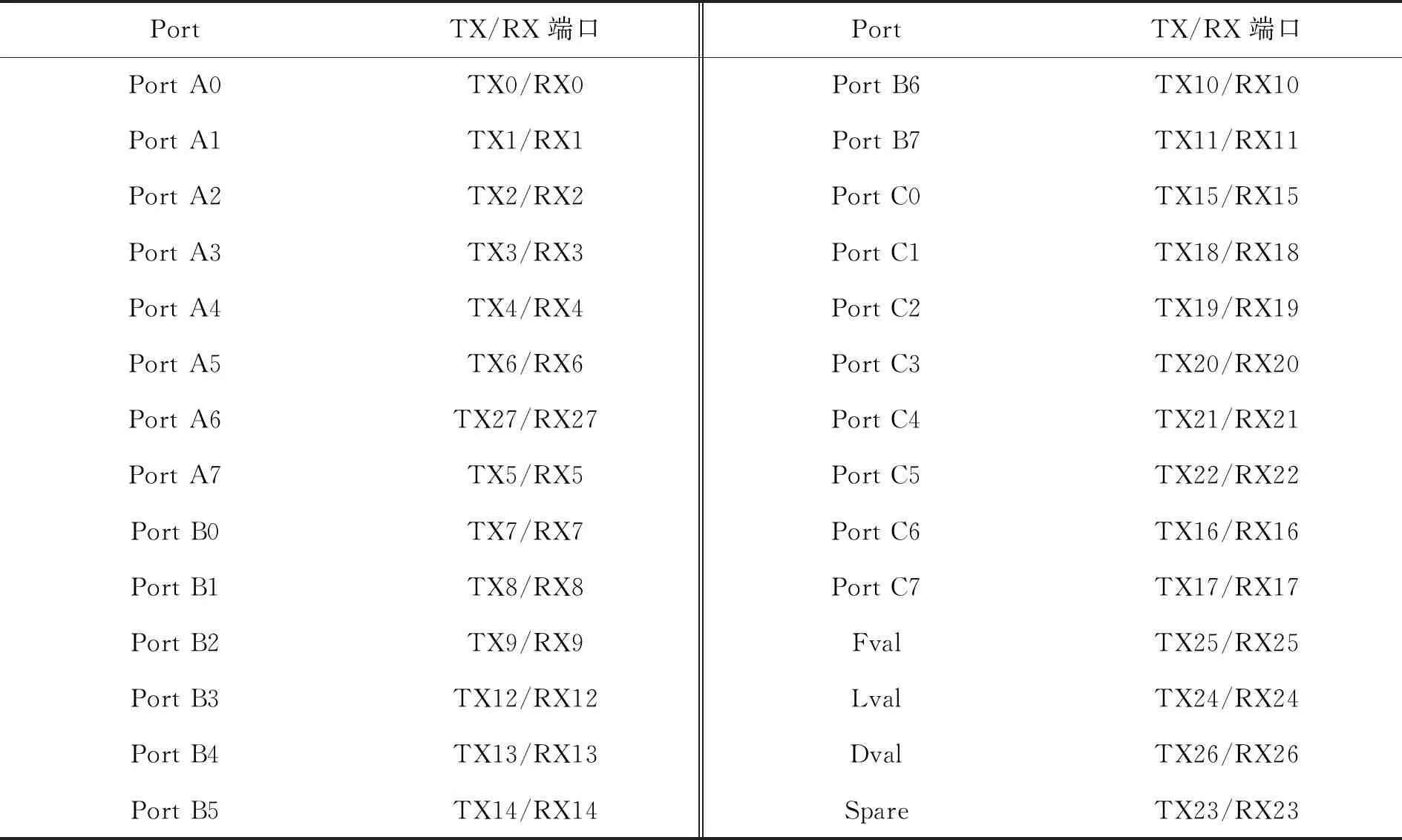

在Camera Link標準中,選擇使用Base基本模式對TX/RX端口的28位數據信號以抽象化的形式分為Port A、Port B、Port C。具體分配如表1所示。采用Port A和Port B的16位數據為圖像的有效數據,4位Fval、Lval、Dval、Spare為圖像傳輸的同步信號。

表1 Camera Link接口的端口分配

當檢測到image_tx_buff模塊中的圖像信號,image_tx模塊會對圖像信號進行發送,Camera Link 標準中并行數據在進行發送時是按照一定的映射方式將數據順序打亂后進行傳輸,這個過程定義為位編碼[7]。位編碼后的數據使用OSERDESE原語可以將7bit并行數據轉換成1bit串行數據。OSERDESE原語可以實現的并轉串轉換比率包括3種:2∶1、3∶1和4∶1[8]。單個IOB 模塊最高可以被配置為4∶1串并轉換比率,因此,使用兩個OSERDESE串聯進行,分組后實現像素數據7∶1的串并轉換比率。OSERDESE數據比率轉換需要使用2個時鐘:clk_txg 和 clk_txio,分別是高度的串行時鐘和分頻并行時鐘,且2個時鐘必須相位對齊。

因此,image_tx模塊中Camera Link接口的發送端主要分為兩個部分:第一部分為輸出編碼部分,首先根據表1數據位對應關系,將需要發送的數據映射到16bit數據輸出端TX;第二部分為串并轉換部分,主要目的是完成由16bit數據到兩組并行7位數據的轉換,同時完成兩組并行7位數據到串行差分數據的轉換;最后通過2個通道X channel和Y channel進行輸出。

2.3 串口通信

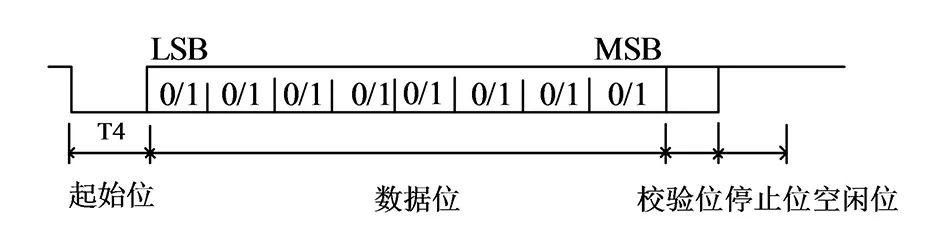

串口數據的接收相對于PC機而言,FPGA扮演從機角色,在固定的波特率下,捕獲主機發送的數據,根據 UART串口發送時序,串轉并得到發送的8位數據[9]。UART傳輸時序如圖4所示。從波形上可以看出起始位是低電平,停止位和空閑位都是高電平,利用這個特點可以準確接收數據,當一個下降沿事件發生時,會將進行一次數據傳輸。

圖4 UART傳輸時序圖

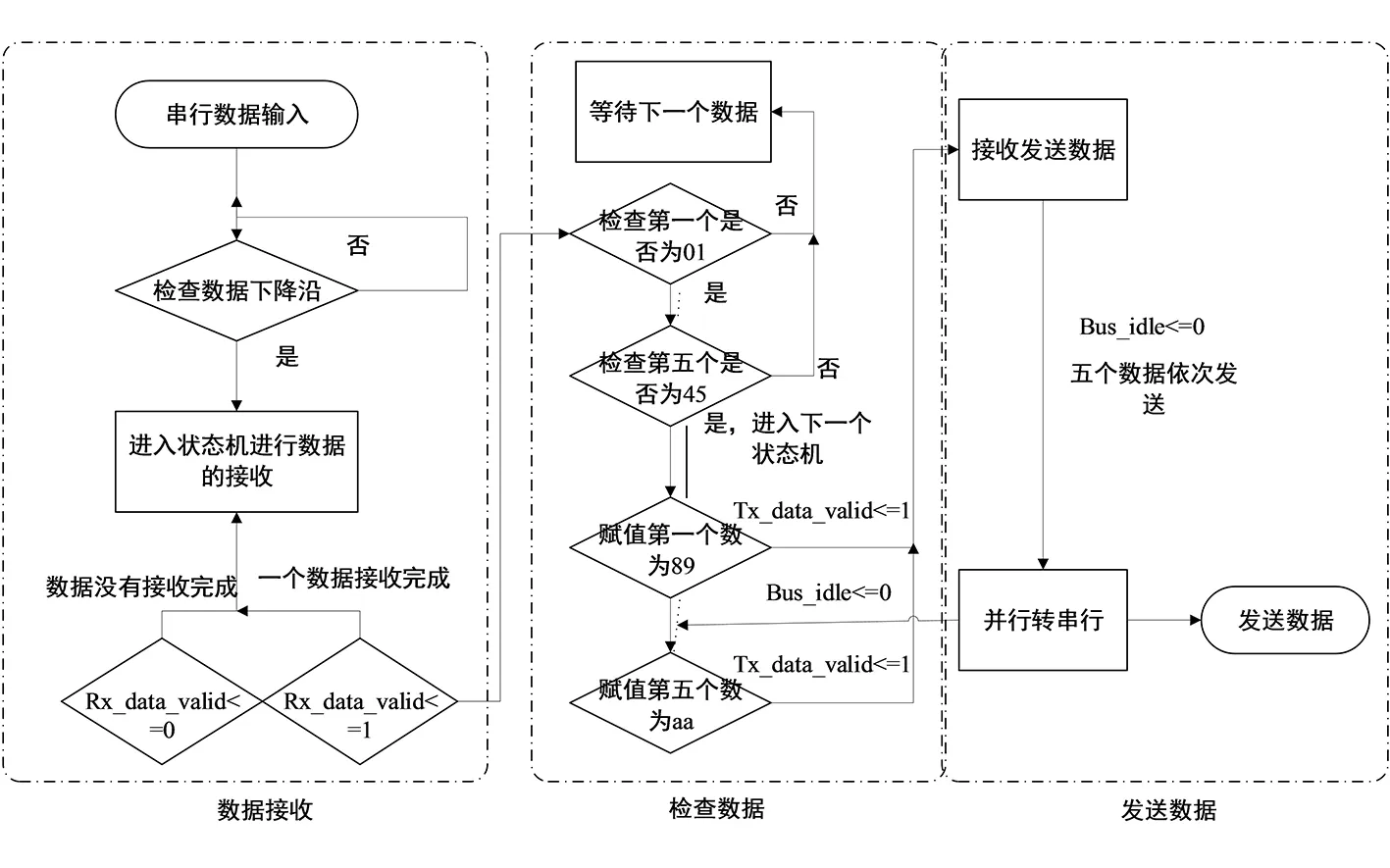

通信串口pool_ic模塊主要分成3個部分:接收數據、檢查核實接收的數據是否正確、發送數據。當接收模塊檢測到數據的下降沿時會進入狀態機,這是串口的起始位置,等起始位結束后進入數據位的接收狀態。狀態機的作用是接收數據,并將串行數據轉為并行數據送入下個模塊進行使用。為避免數據出錯并滿足采樣定理,設置一個關于波特率的計數器cycle_cnt,保證在接受數據時每個數據都在波特率計數器的時間中點進行采樣。當檢查數據的模塊檢測到使能信號rx_data_valid的值為1時,開始接收上一個模塊的數據。檢查傳來的數據值是否為01,直到接收到5個正確的數據就進入下一個狀態機。將要發送的第一個數據賦值為89,并且拉高使能信號tx_data_valid,將數據傳入發送模塊。發送模塊的邏輯設計和接收模塊一樣。其具體流程框圖如圖5所示。

圖5 通信串口流程框圖

常見的串口通信波特率有2 400 bps 、9 600 bps、115 200 bps 等,發送和接收波特率必須保持一致才能正確通信,波特率的大小會影響數據的傳輸速率。本研究使用115 200 bps的波特率,代表一個數據位的時間長度是1/115 200 s。且不設置奇偶校驗位,發送端發送數據分別是01、02、03、56、45,接收端返還的數據為89、67、55、23、aa。如果發送其他的數據和順序時,FPGA將不返還數據。

3 仿真結果與分析

調用Modelsim仿真軟件進行測試,其仿真結果如圖6所示。由仿真結果可以看出,時鐘分頻和倍頻的結果符合設計要求,clk_txg和clk_txio是同相位,且clk_txio是clk_txg的7倍。串口通信模塊接收到了測試文件發送的01、02、03、56、45這5個數據,并且不存在缺少數據和錯誤數據的情況,其輸入的方式是串行輸入。并且經過檢查后,輸出89、67、55、23、aa這五個數,并沒有出現順序上的錯誤。根據串口的協議,最后并不是8位數據并行發送,而是串行的形式傳輸出去,說明UART串口的收發模塊通信正常。圖像傳輸模塊由于數據過于龐大,會有折疊,但可以清晰地看出與上述邏輯相同。傳輸一行有效數據需要25 μs,每一行包含1 250個像素點。傳輸一幅圖所需要的時間為78 ms,在1 s中可以傳輸12幅圖。過程中均無缺少像素點的情況發生,每一行之間時鐘周期的間隔較大,不會產生干擾。且并轉串的過程中沒有發生錯誤,說明圖像傳輸收發模塊正常。

圖6 仿真結果圖

4 結語

本研究主要根據Camera Link標準協議,基于FPGA設計了3個模塊來實現Camera Link接口設計,分別為時鐘模塊、圖像傳輸模塊、通信串口模塊。根據所設計的方案,FPGA設計的圖像信號結構簡單,實現方便,而且具有很強的可擴展性。通過Camera Link接口和相機連接,可以從相機獲得高分辨率的實時圖像,并傳輸到FPGA中進行實時圖像處理并輸出,實現采集卡和計算機之間的通信,用于相機功能參數的設置。這種簡單可靠的設計對FPGA在的Camera Link開發中具有較強的可操作性和應用價值,為正在研制的實時高速圖像采集卡奠定了基礎。