基于FPGA的IEEE488接口協議實現及驅動程序開發

劉 陽,羅顯志,周楊羅,李 政

(湖北大學 計算機與信息工程學院,武漢 430062)

0 引言

在自動測試系統中,IEEE488總線扮演著重要的角色。它是一種面向儀器設備的通用總線接口,也被稱為GPIB總線[1-2]。該接口最早由HP公司提出,經過幾十年的發展,已經形成了一套行業標準。且該接口能滿足設備之間互相通信的功能,實現信息共享的需求。

近年來,國內在自動化控制、精密儀器研制等領域發展迅猛,在醫療、軍工等領域,對測試系統的需求越來也越大。GPIB作為業界使用最廣泛的測試總線,不僅成本低,而且傳輸穩定,在未來的一段時間內,國內市場仍然有一定的需求量。

市面上的GPIB轉換器基本都采用專用接口芯片來設計,此類芯片連接微處理器,通過讀寫寄存器等操作能很

方便的實現GPIB接口的所有功能。目前,能自主生產基于IEEE-488協議的專用GPIB接口芯片的公司僅NI、TI、NEC、Intel幾家[3],但該類芯片都已停產,可供購買的成品GPIB轉換器如NI-GPIB-USB-HS價格在3 000元以上,對國內龐大的用戶群體來說成本過高。國內在測試接口領域的研究較少,僅有電子科大等幾個團隊,且市面上國產轉換器占有率不高。隨著ASIC技術的飛速發展,FPGA在嵌入式領域得到了廣泛應用,它靈活、穩定、可移植性強,所以能夠用來替代一些專用芯片。

基于以上因素,本文詳細闡述使用FPGA芯片來實現IEEE488總線協議的方案及實現流程,為相關開發人員提供可行性參考。

1 總體設計

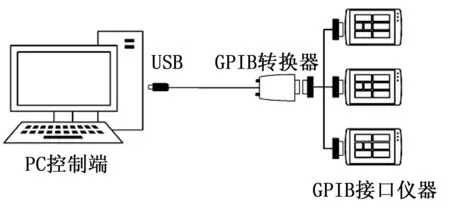

基于FPGA的IEEE488協議轉換器的設計主要包括硬件和軟件兩部分。硬件部分包括硬件電路設計與硬件控制程序設計;軟件部分主要是驅動程序開發,最后通過用戶程序與儀器通信。該方案組建一套完整的測試系統,其總體結構[4]如圖1所示。

圖1 總體結構框架

該方案的核心在于硬件控制程序設計,開發前需要對IEEE488總線協議做深入研究,同時剖析NI的NAT9914的內部結構,掌握其協議的工作原理。硬件控制程序的主要內容是模擬GPIB接口的十種功能,然后通過讀寫控制模塊控制數據準確無誤的傳輸,在PC與儀器之間搭建數據傳輸的橋梁。軟件驅動程序連接PC與轉換器,實時發送程控指令并接收返回的數據。

2 硬件電路設計

硬件電路設計主要包括電源模塊、USB-UART模塊、FPGA主控模塊及外圍電路、GPIB接口模塊。硬件設計框架如圖2所示。

圖2 硬件設計框架

2.1 電源模塊

電源模塊為整個系統提供穩定電壓。電源芯片使用MC34063,該芯片性能好,市場應用廣泛,可實現升壓和降壓功能,但其實現電路不同。本系統采用USB接口供電,其電壓大致為5.2 V左右,所以需設計降壓電路。FPGA芯片的不同BANK所需電壓不同,因此添加LM1084可調輸出線性穩壓器,提供3.3 V、2.5 V、1.2 V工作電壓。電源電路部分設計如圖3所示。

圖3 電源模塊

該芯片內部有恒定的1.25 V基準電壓,輸出電壓與R35和R36的阻值有關,其輸出電壓的計算公式為:

Vout=1.25*(1+R36/R35)

(1)

由公式(1)推出,為輸出5 V電壓,R36和R36的阻值分別為10 K和3K3。

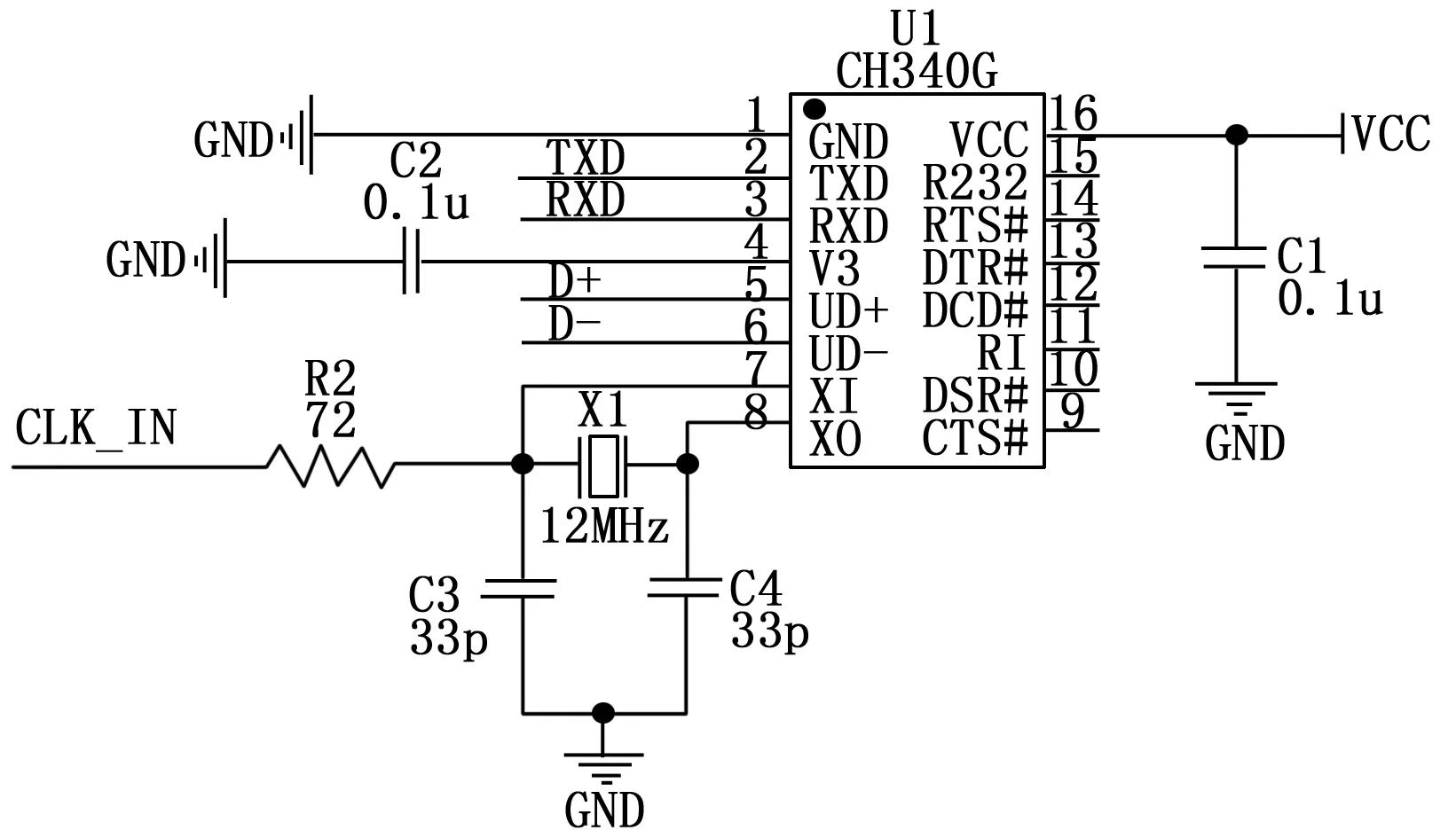

2.2 USB-UART模塊

USB-UART模塊建立PC端與主控芯片的數據通道。協議轉換芯片采用CH340G-USB轉串口芯片,該芯片外圍電路簡單,性能穩定,資料豐富。電路中將Rx與Tx引腳接入FPGA芯片進行數據交換,D+與D-接入USB接口數據引腳與PC端進行數據交換。該芯片工作時需外接12 M晶振,同時為保證系統時鐘的同步,引出時鐘輸入引腳與FPGA芯片相連。USB-UART模塊如圖4所示。

圖4 USB-UART模塊

2.3 FPGA主控模塊及GPIB接口模塊

FPGA主控芯片的選擇參考市場兩大主流FPGA芯片廠商,再結合本項目的設計要求,最終采用Xilinx的Spartan-6系列的XC6SLX4芯片,該芯片的引腳數和容量能滿足設計需求,且網絡資源充足,易上手。

主控芯片的差分引腳主要與GPIB接口的16根信號線和UART模塊的數據線連接,以實現接口的控制和數據傳輸。外圍電路還包括JTAG下載電路、SDRAM外部存儲模塊以及時鐘和復位電路。JTAG下載調試電路使用XCF01SVO20C-FPGA配置芯片,系統外部時鐘采用50 M晶振。此外,使用K4S511632B-TC75存儲芯片設計SDRAM外部存儲模塊,防止因FPGA芯片內部緩存不足造成數據丟失的現象。主控模塊還外接了LED小燈等外圍電路,用來作為數據讀寫的指示燈。

傳統的GPIB接口電路模塊一般由專用GPIB接口芯片和總線收發器組成。本方案使用FPGA芯片模擬GPIB接口功能,因此無需GPIB接口芯片和總線收發器。但GPIB接口工作電壓是5 V,而FPGA芯片的最高電壓為3.3 V,故在FPGA芯片與GPIB接口之間添加MOS-N模塊實現電平轉換。

3 硬件控制程序設計

硬件控制程序是設計的核心與難點。在設計之前,需要對IEEE488總線協議和GPIB接口芯片的內部結構做深入研究。

3.1 IEEE488總線介紹

IEEE488總線[5-6]自提出以來,一直被廣泛應用于測試、控制等領域。它由數據線、三根握手線、五根接口管理線以及地線組成。三根握手線配合工作,通知總線何時傳輸數據,何時接收數據,確保數據傳輸準確無誤。接口管理線ATN控制總線上傳輸的是數據還是指令,EOI提示總線何時傳輸結束等,IFC設置所有的設備于靜止狀態,REN使能設備進行遠程編程,SRQ提醒控制器是否需要服務。在工作時,測試系統存在3種角色,即控者負責發送各種命令,講者發送數據,聽者接收數據。

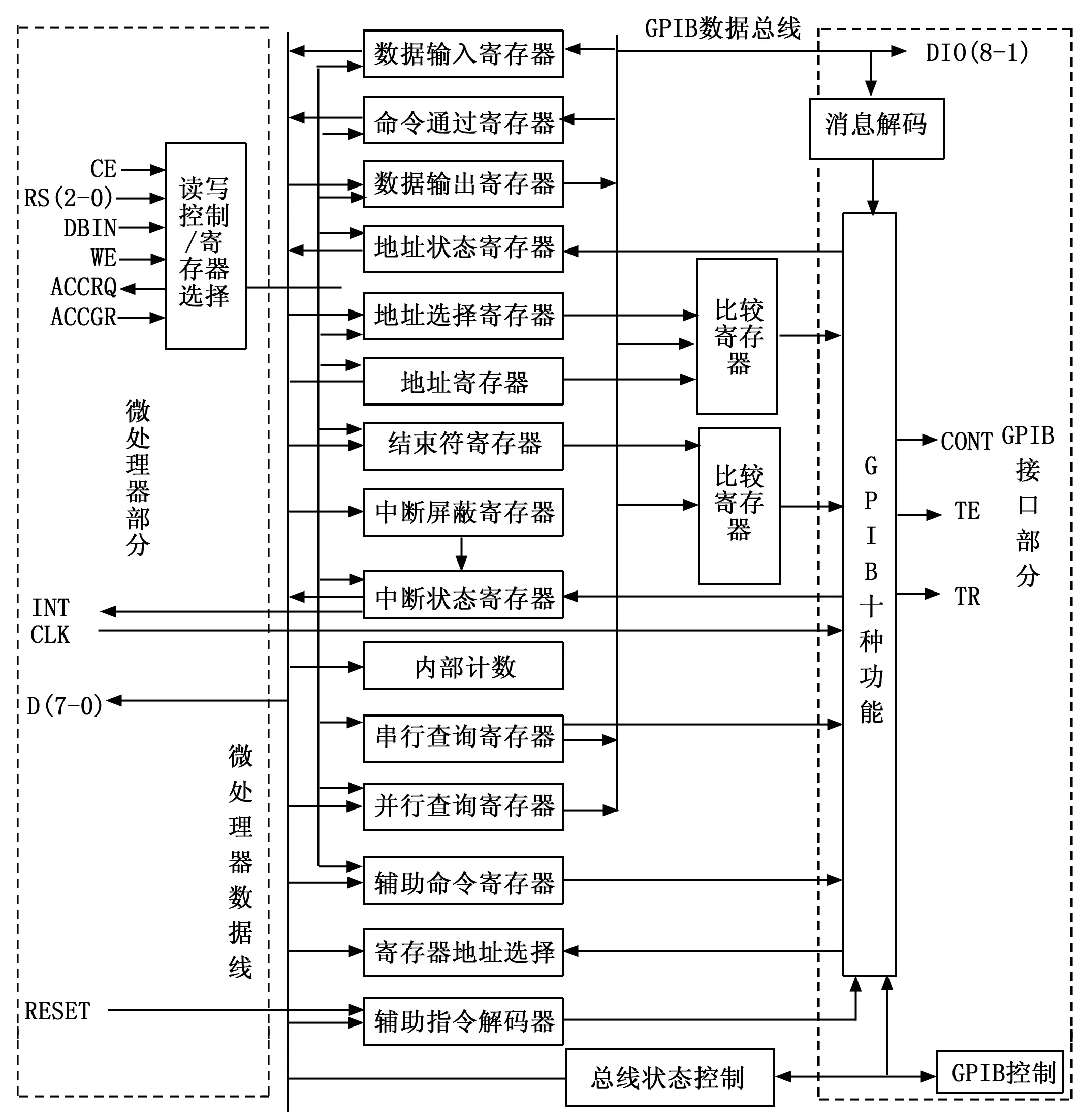

典型的GPIB專用接口芯片NAT9914的內部電路主要分為兩部分。一部分面向GPIB總線,主要包括GPIB接口的十種功能以及各種緩沖器和譯碼器。另一部分面向微處理器,通過編寫驅動程序讓微處理器訪問25個可尋址寄存器,其主要類型有數據類寄存器、中斷類寄存器、地址類寄存器。NAT9914的內部結構[7-8]如圖5所示。

圖5 NAT9914內部結構

GPIB接口共定義了10種接口功能,分別是源方和受方掛鉤功能、講者、聽者、控者、器件清除功能、服務請求功能、并行輪詢功能、遠控/本控功能、器件觸發功能。其中前五種是基本接口功能,后5種是輔助接口功能。基本功能是所有帶GPIB接口的設備必須具備的,保證測試系統中各儀器之間能相互通信,輔助功能讓測試系統更便捷、更智能。

3.2 GPIB接口功能的程序設計與仿真

該方案的硬件程序使用Verilog硬件描述語言進行開發,軟件采用Xilinx的ISE。整體設計采用自頂向下的設計思想,將整個系統拆分成若干個子功能模塊,其中包括串口數據收發模塊、數據讀寫控制模塊、中斷模塊以及GPIB接口功能模塊,每個子功能模塊又有不同的狀態,同一時刻只允許存在同一種狀態,不同的狀態又通過相互聯系的小狀態機進行切換,且狀態的改變與之前設備所處的狀態關聯,這樣就構成了一個相互排斥又相互聯系的狀態機。通過各模塊的接口功能狀態機的聯系,最總形成一個頂層GPIB接口功能狀態機。

GPIB接口功能的實現依賴于各個功能模塊的實現,由于篇幅有限,該章節主要對GPIB接口的講者(T)、聽者(L)功能、FIFO模塊的設計進行詳細描述,并利用Modelsim軟件進行仿真驗證。

3.2.1 講功能(T)設計

講功能[9-10]的主要作用是將用戶發送的程控指令或者數據通過總線發送到測試系統中的儀器中,或者將儀器自身的工作狀態以及參數等信息通過數據總線傳輸到PC端。只有當系統控者尋址講者或者設備通過ton指令將自身設置為講者時,才賦予這種功能。同一時刻,一個測試系統中只存在一位講者。

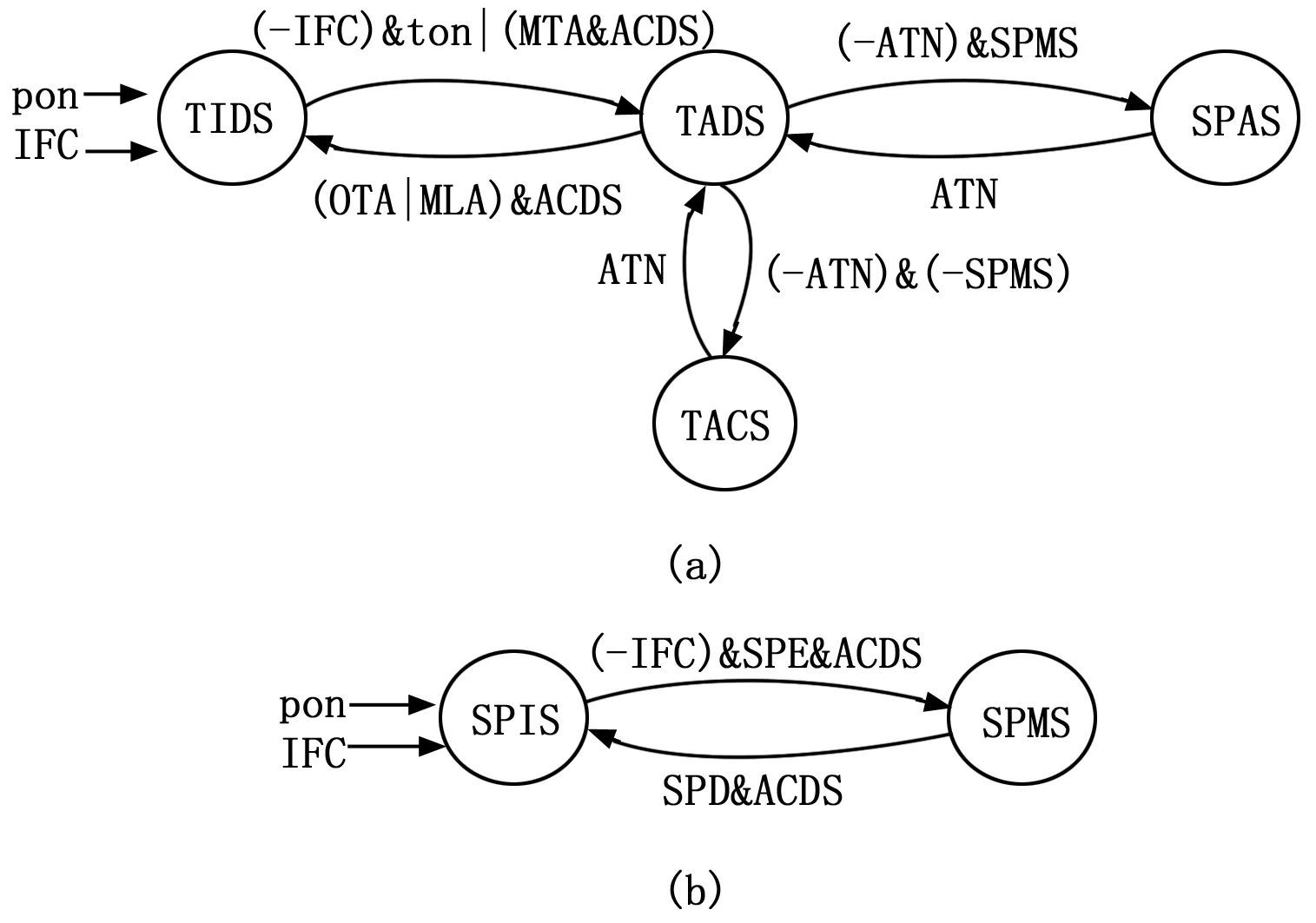

講功能的狀態分為TIDS(講者空閑態)、TADS(講者被尋址態)、TACS(講者活動態)、SPAS(串行活動態)、SPIS(串行空閑態)、SPMS(串行模式)共6種,按照協議功能又分為講者數據傳輸和串行輪詢兩組事件,分別如圖6(a)和圖6(b)所示。講者狀態圖如圖5所示。

圖6 講功能狀態圖

事件(a)中,在設備上電后,講功能同時進入TIDS和SPIS兩種狀態,此時不具備數據傳輸能力。當設備被尋址為講者(即MTA=1)或設備通過ton指令設置自身為講者,且ACDS為活動態時,講功能進入被尋址態,此時講者準備好發送數據。ATN信號線決定系統傳輸的數據類型,當ATN為假時,表示GPIB總線上傳輸的是數據,當SPMS是活動態時,設備進入SPAS狀態;當SPMS為假時,講者進入TACS狀態,此時配合SH功能將數據傳到GPIB數據總線。當設備處于SPAS或TACS狀態時,若ATN為真,說明系統控者發送命令,講功能返回尋址態。

事件(b)中,若SPE為真,即允許串行查詢,聽者進入串行輪詢模式狀態,并參與串行輪詢。當系統活動控者發送SPD命令,即禁用串行輪詢。聽者進入串行輪詢空閑狀態。

講功能的Verilog設計包括了圖5中兩組狀態,每種狀態的轉換都通過分析當前的狀態機來轉換,結合各狀態之間相互排斥又相互聯系的特征,TIDS和SPIS采用并行語句執行。(b)狀態的具體實現的核心部分代碼如下所示:

case (current_state_2)

T_STATE_2_SPIS :

if (event2_1)

current_state_2 <= T_STATE_2_SPMS;

T_STATE_2_SPMS :

if (event2_3)

current_state_2 <= T_STATE_2_SPIS;

else if (event2_2)

current_state_2 <= T_STATE_2_SPIS;

default :

current_state_2 <= T_STATE_2_SPIS;

endcase

assign event2_1 = SPE 1'b1 & ACDS 1'b1;

assign event2_2 = SPD 1'b1 & ACDS 1'b1;

assign event2_3 = IFC 1'b1;

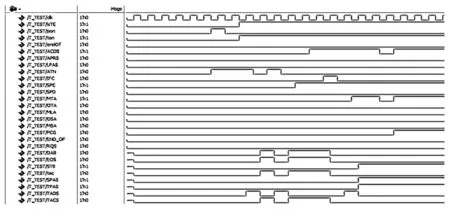

通過編寫Testbench仿真文件,使用Modelsim仿真后波形如圖7所示。根據分析可以看出,講功能的每個狀態嚴格按照狀態圖進行變換,且同一時刻只存在一種活動態。

圖7 講功能仿真波形

3.2.2 聽功能(L)設計

聽功能[11]的主要作用是接收儀器發送過來的狀態信息或者主控設備的指令。同一時刻,一個測試系統中可以存在多位聽者。

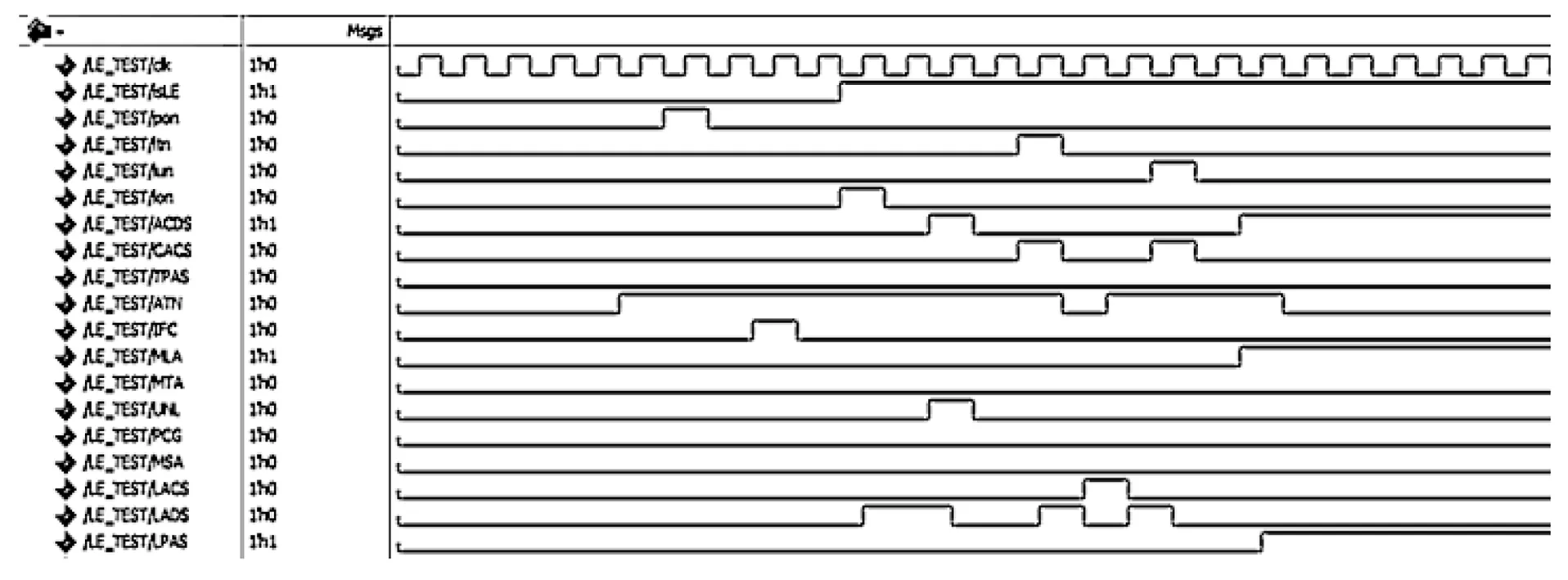

聽功能的狀態分為LIDS(聽者空閑態)、LADS(聽者被尋址態)、LACS(聽者活動態)、LPIS(聽者主空閑態)、LPAS(聽者主被尋址態),其中后兩種為擴展聽者(LE)狀態。聽者狀態如圖8所示。

圖8 聽功能及擴展聽功能狀態圖

狀態圖(a)是聽功能的狀態圖,當設備上電后,聽功能同時進入LIDS和LPIS兩種狀態。當設備被尋址為聽者(MLA=1)或者設備通過lon指令設置自身為聽者,且ACDS為活動態時,聽功能進入被尋址態,此時聽者準備好接收數據。若ATN為假,表示GPIB總線上傳輸數據,此時聽者變為LACS狀態,并且配合AH功能從數據總線上接收數據。若ATN為真,表示GPIB總線傳輸命令,聽者由活動態變為被尋址態。當控者發出unl命令,宣布測試系統內所有的設備取消聽者狀態,且ACDS為真時,聽者進入空閑態。

狀態圖(b)是擴展聽功能的狀態圖,在LPIS狀態下,聽功能可以識別它的主地址,但無法響應它的副地址。當聽功能被尋址且處于接收數據狀態時,聽功能進入被尋址主狀態,此時聽功能可以識別并響應它的副地址。

聽功能的Modelsim仿真波形如圖9所示。

圖9 聽功能仿真波形

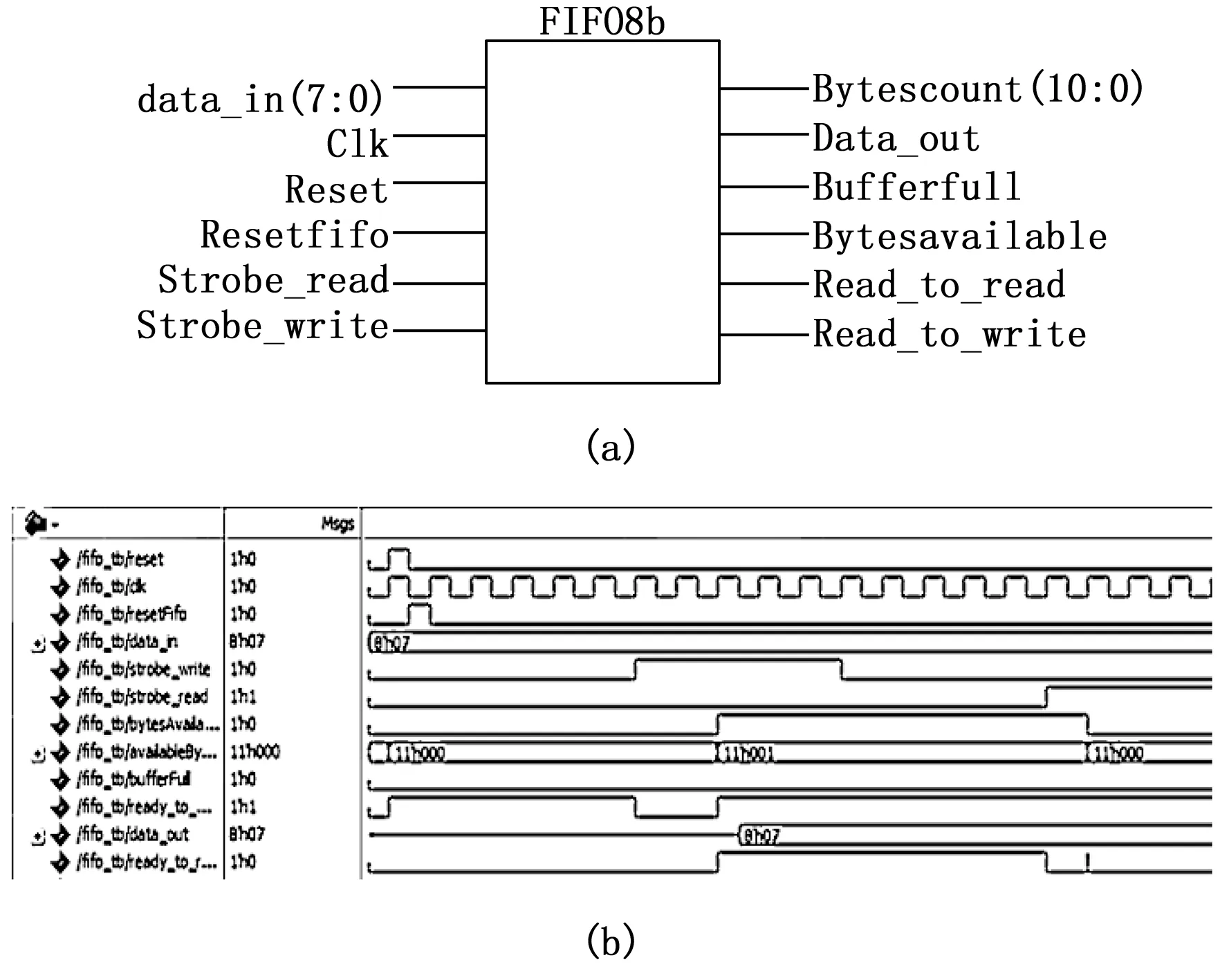

3.2.3 FIFO模塊設計

為提高系統傳輸數據的穩定性,避免因控制端和數據端傳輸速率差異造成的數據丟失現象,設計FIFO模塊作為數據緩沖區。

FIFO模塊連接讀寫控制端和數據總線端。讀寫控制部分由Clk、Reset_Fifo、Read、Write、Buffer_full組成,data_in[7:0]和data_out[7:0]連接數據總線。當轉換器身份為講者時,從FIFO中取數據放入總線,若FIFO數據為空,則讀寫控制端寫入準備發送的數據。當轉換器身份為聽者時,將總線上的數據存入FIFO,若FIFO存在數據,則通知讀寫控制端讀取數據。FIFO的RTL視圖如圖10(a)所示。Modelsim仿真波形如圖10(b)所示。

圖10 FIFO RTL視圖與仿真波形

3.3 內部寄存器設計

NAT9914芯片的工作主要通過配置內部寄存器來完成。設計中通過讀寫控制模塊對各個寄存器進行配置,從而控制接口的數據傳輸。

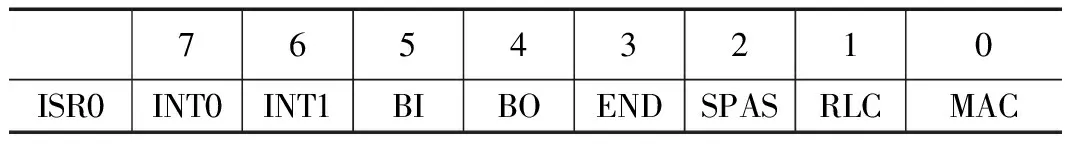

設計的寄存器主要有地址寄存器、GPIB總線寄存器、GPIB狀態寄存器、接口功能寄存器、GPIB控者寄存器、讀寫控制寄存器,中斷控制寄存器。其中,中斷寄存器ISR0與聽、講功能相關,其結構如表1所示。

表1 ISR0寄存器

ISR0可讀寄存器的BI、BO、END位分別代表數據接收位、數據發送位、數據傳輸結束位。當設備為系統活動控者或者講者時,BO位置1,此時可以向系統內其他設備發送命令或數據;當設備為聽者時,當數據接收寄存器接收到數據時,BI位置1;當接收到結束符0x0A時,END位置1,結束本次數據傳輸。

3.4 GPIB數據傳輸

數據傳輸是硬件控制程序的核心部分,也是該協議轉換器要實現的最主要功能。

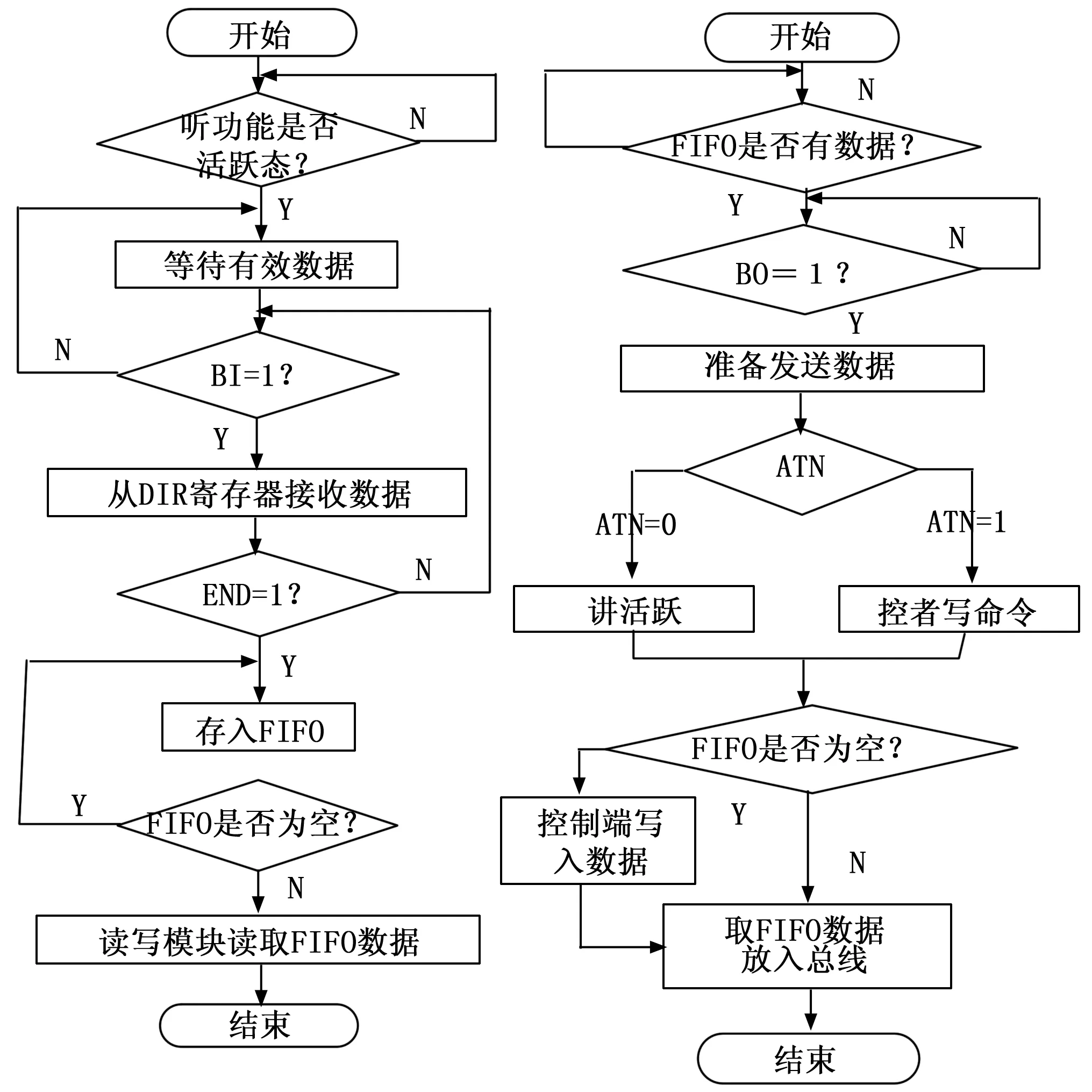

在各個子功能模塊完成的基礎上,構建從UART模塊到GPIB接口模塊的數據通道。數據的傳輸主要依靠設備的聽、講功能以及讀寫控制模塊,還有FIFO存儲模塊。聽講功能控制數據傳輸的方向,FIFO模塊控制數據的存取。讀寫控制模塊直接配置狀態寄存器,進而配置GPIB的接口功能,并配合FIFO模塊完成數據的存取。在程序中設計了GPIB_Read和GPIB_Write兩個資源文件,用來實現GPIB的讀寫操作。在GPIB_Read模塊中,輸入輸出端口名分為GPIB接口、外部接口、FIFO模塊3部分。GPIB接口部分用來判斷當時是否處于聽活躍狀態,外部接口模塊負責產生數據中斷等信號,FIFO模塊則提示是否存在數據以及數據的存取。GPIB_Write模塊的結構與GPIB_Read模塊基本類似。讀寫的邏輯結構如圖11所示。

圖11 GPIB讀/寫流程圖

4 軟件驅動程序設計

4.1 VISA簡介

VISA(virtual instrument software architecture),即虛擬儀器軟件結構[12-14]。VISA是一種通用的I/O標準,提供了一套完整的、易操作的函數庫,存在于計算機系統內,通過軟件層與儀器建立連接。

傳統的儀器,不同的接口需要開發不同的驅動程序來供用戶使用,這將耗費大量的人力物力來開發與維護。VISA獨立于接口、語言和操作系統,采用統一的操作函數,無論是串口、GPIB、LAN接口,都使用VISA函數來操作,體現了VISA的硬件無關性。統一的核心函數與其它無法合并的、與儀器類型相關的功能函數一起構成了自底向上的I/O接口模型,實現不同類型的儀器的互操作性與兼容性,這也是VISA的最大優點之一。

VISA的結構共分為五層,資源管理層主要主要負責資源的尋址、創建與刪除等功能的實現。I/O資源層提供了底層I/O函數,對硬件接口進行讀寫等操作,該資源與傳統的I/O函數相似。儀器資源層主要針對不同儀器的特定功能。用戶資源層是可變層,根據用戶自己定義資源。應用程序層提供用戶與儀器交互的窗口。

4.2 VISA驅動程序開發

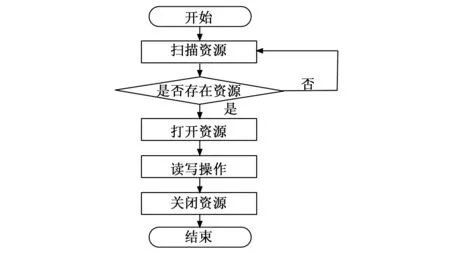

本設計采用NI公司提供的VISA庫,在開發之前需安裝NI-VISA。驅動程序的一般設計流程如圖12所示。

圖12 驅動開發流程

驅動程序具體實現流程[15-18]如下:

1)掃描資源:首先調用viOpenDefaultRM()函數來掃描系統中的接口和設備資源,此后才能調用其他VISA函數。當用戶需要查找特定的設備時,可以調用viFindRsrc()函數。

2)打開資源:通過viOpen()函數建立儀器之間的會話通道,其參數根據接口類型確定。如建立與主地址為2的GPIB接口的會話,則參數設置為GPIB0::2::INSTR。

3)讀寫操作:公用的VISA底層I/O函數有viRead()、viWrite()等;GPIB接口特殊I/O函數有的viReadSTB()、viClear()等,每個函數實現一種接口功能。本設計調用公用I/O函數與建立會話通道的接口進行通信。

4)關閉資源:調用viClose()函數關閉已建立的會話通道,并清除資源。

在VC++6.0環境下測試VISA驅動程序,將VISA.H和VISATYPE.H文件拷貝到工程中,使用C語言調用相關庫函數。核心代碼部分如下所示:

int main(void){

ViSession defaultRM;

....... //定義變量

status=viOpenDefaultRM (&defaultRM);

status=viOpen(defaultRM,"ASRL4::INSTR",VI_NULL,VI_NULL,&instr);

status = viSetAttribute (instr,VI_ATTR_TMO_VALUE,5000);

....... //參數配置

status=viWrite(instr,"*IDN? ",(ViUInt32)strlen("*IDN? "),&writeCount);

status = viRead (instr,buffer,100,&retCount);

if (status! printf ("

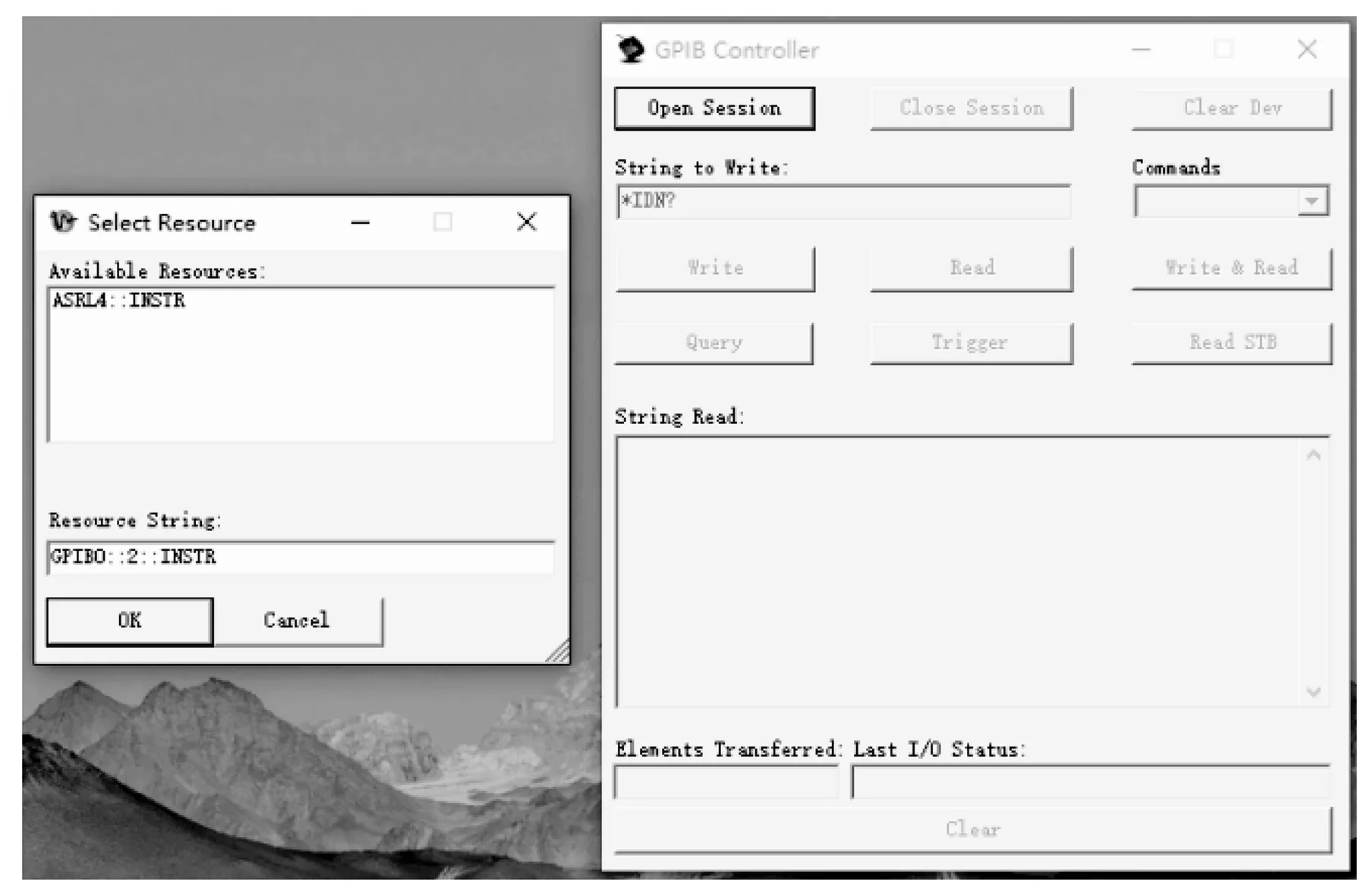

Data read:%*s

",retCount,buffer); } status = viClose (instr); status = viClose (defaultRM);} 將協議轉換器和Tek1002示波器連接,運行該程序生成的.EXE可執行文件,運行測試結果如圖13所示。 圖13 VC++下VISA測試結果 驅動應用層開發平臺為Visual Studio 2017,采用C#面向對象高級程序設計語言,它運行在.NET Framework框架上。.NET Framework包括3個應用程序模型,設計采用Windows Forms模型,它屬于.NET Framework中的GUI類庫,該模型采用控件式編程,開發難度較低。 NI-VISA提供了基于.NET的VISA函數庫,在項目中添加NI的NationalInstruments.Visa和Ivi.Visa函數庫可直接調用VISA函數。 應用層開發主要分兩部分,一部分為資源搜索界面,另一部分為基本讀寫操作界面。資源搜索界面通過ResourceManager.Find(“(ASRL|GPIB|TCPIP|USB”?*INSTR))函數來搜索系統中所有類型的設備,并將值返回ListBox列表框中。選中資源,點擊OK按鈕時,執行ResourceManager.Open函數與設備建立連接。操作界面主要由Button和TextBox兩大控件組成,讀寫等按鈕執行基本IO操作,在控件中調用RawIO.BeginWrite()和RawIO.BeginRead()函數,當點擊事件發生時,則執行讀寫函數,并將返回值發送到TextBox文本框中,此外還添加了Trigger和Read STB等功能型按鈕,通過調用接口功能函數對設備進行操控。 最終設計的用戶操作界面如圖14所示。 圖14 用戶程序界面 可編程儀器標準命令,簡稱SCPI[19-20]。它是一種控制儀器的語言規范,規定了一種標準的語言結構來控制儀器,采用ASCI字符串的形式與設備之間進行數據的交互。 早期的儀器設備,由于沒有統一的程控命令標準,不同的儀器在軟件上很難兼容。SCPI的出現,給整個行業提供了一套可參考的標準,完美解決了不同儀器的兼容性問題。且SCPI采用助劑符的方式,把復雜的指令縮寫成簡潔且容易記住的指令,便于用戶使用。 測試采用對比實驗,實驗設備使用Tek1002示波器。通過對基本指令以及示波器的數據采集等指令的測試,評估其性能。 5.2.1 公用指令測試 SCPI公用指令共39條,是所有帶GPIB接口的設備必須具備的。 公用指令測試使用自主研發的GPIB上位機和轉換器與NI控制面板和NI-GPIB-USB作比較,都發送*IDN?指令,查看其返回結果是否一致。測試結果如圖15所示。其中,圖(a)為自主研發設備返回結果,圖(b)為NI設備返回結果。 圖15 公用命令測試結果 5.2.2 性能測試 性能測試軟件采用NI公司的I/O Trace,該軟件能捕獲各函數的響應時間,通過在同一軟件下對比自研GPIB轉換器和NI-GPIB-USB轉換器來評估該設計的設備性能。測試結果如圖16所示。圖(a)自主研發設備響應時間,圖(b)為NI設備響應時間。 圖16 指令響應時間 從圖16中可以看出,自研設備在響應*IDN?和*TST?兩個指令的時間分別為958 ms和1 252 ms,NI的響應時間為982 ms和1 242 ms。經對比,自研GPIB轉換器性能優異,完全能滿足實際應用需求。 GPIB接口的重要功能是采集儀器的數據。數據采集實驗通過STM32F103開發板的DA模塊輸出波形,使用Tek1002示波器測量波形,將該設計的GPIB卡連接示波器,通過Tek公司的OpenChoiceDesktop上位機軟件連接示波器,首先發送:SELECT:CH1選擇示波器通道1,然后發送CH1:PROBE?等查詢指令查詢示波器的各種參數,最后發送:CURVE?返回曲線數據,并反饋到Tek公司的OpenChoiceDesktop上位機軟件上。測試結果如圖17所示。 圖17 數據采集測試結果 本文設計了一款以FPGA芯片為主控,通過硬件描述語言實現IEEE488接口的所有功能的協議轉換器。文中介紹了轉換器硬件設計、控制程序設計,還詳細介紹了基于VISA的驅動程序設計流程。該設計為解決當前市場GPIB專用芯片停產、轉換器價格昂貴等問題提供了一套完整的替換方案。經測試實驗表明,該轉換器性能穩定、體積小,完全滿足日常測試所需,為從事相關方面研究的開發人員提供了可行性的參考案例。

4.3 驅動應用層開發

5 SCPI指令測試

5.1 SCPI簡介

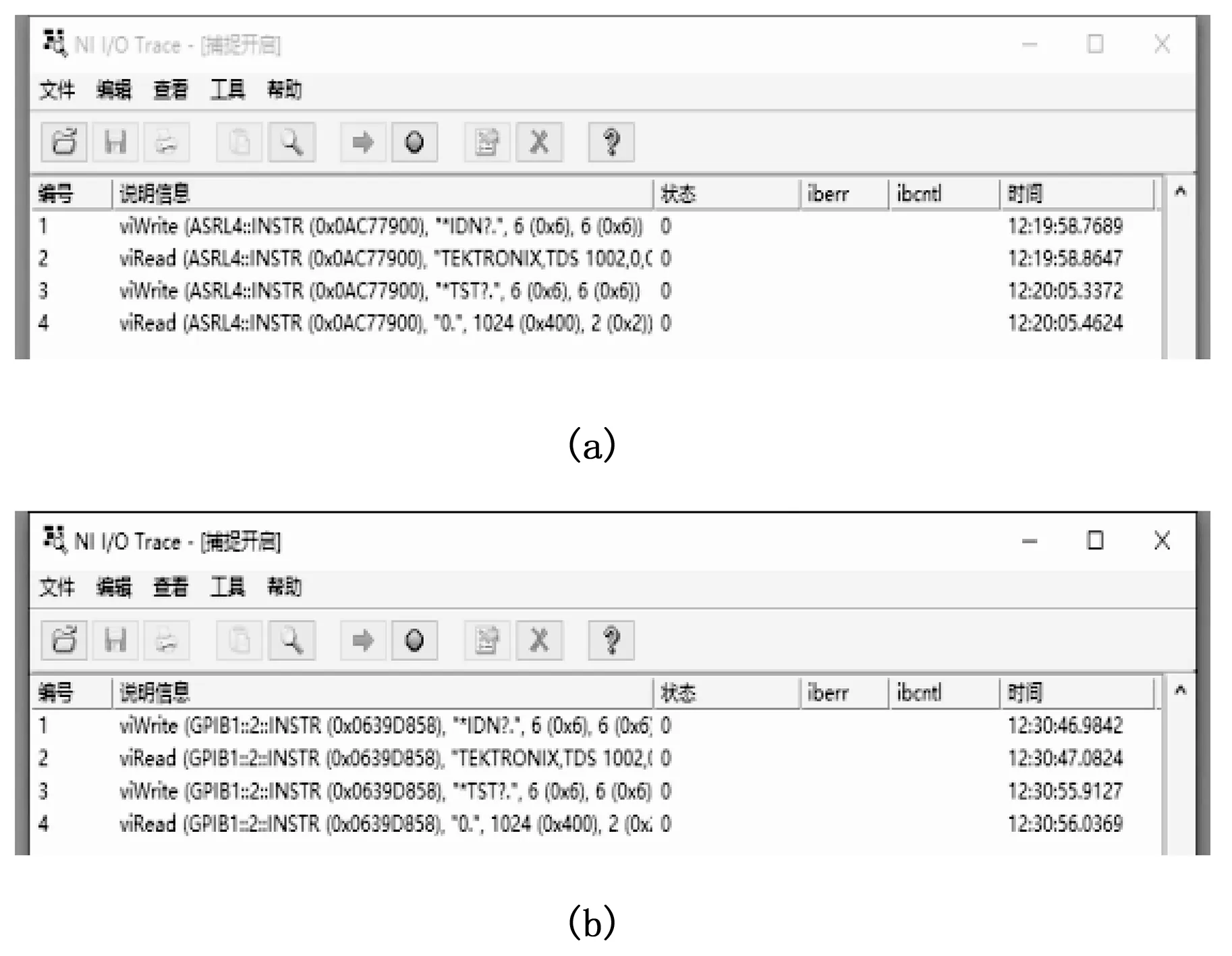

5.2 SCPI命令測試

5.3 示波器數據采集測試

6 結束語