Q波段氮化鎵功率放大器芯片

王海龍,崔 亮

(中國電子科技集團公司第十三研究所,河北 石家莊 050000)

0 引 言

毫米波段雷達系統受大氣成分的低衰減特性影響,廣泛應用在30 GHz以上的頻段,其射程主要取決于射頻(Radio Frequency,RF)功率放大器的輸出功率。先前系統中使用的砷化鎵(GaAs)功率放大器受材料的限制,工作電壓較低,輸出功率一般在幾瓦特,效率不高。近年來,氮化鎵(GaN)器件迅速發展,其性能遠遠超過砷化鎵器件[1]。氮化鎵功率放大器具有更高的工作電壓和輸出阻抗,使得匹配網絡的設計更容易,同時具有更高的效率[2]。而高輸出功率的毫米波段功率放大器作為毫米波段雷達系統的重要部件,其工作在發射通道的末級,主要對前級微小射頻信號進行功率放大和發射,用于微波通信和遙感測控等領域[3-5]。本文設計實現的GaN功率放大器芯片是在0.15 μm GaN 假態高電子遷移率晶體管(Pseudomorphic High Electron Mobility Transistor,pHEMT)單片工藝線上制作完成,采用有耗匹配、電感電容匹配網絡以及4級級聯放大等技術設計電路,利用仿真軟件進行電路優化、電磁場仿真以及芯片版圖設計。

1 功率放大器設計方法

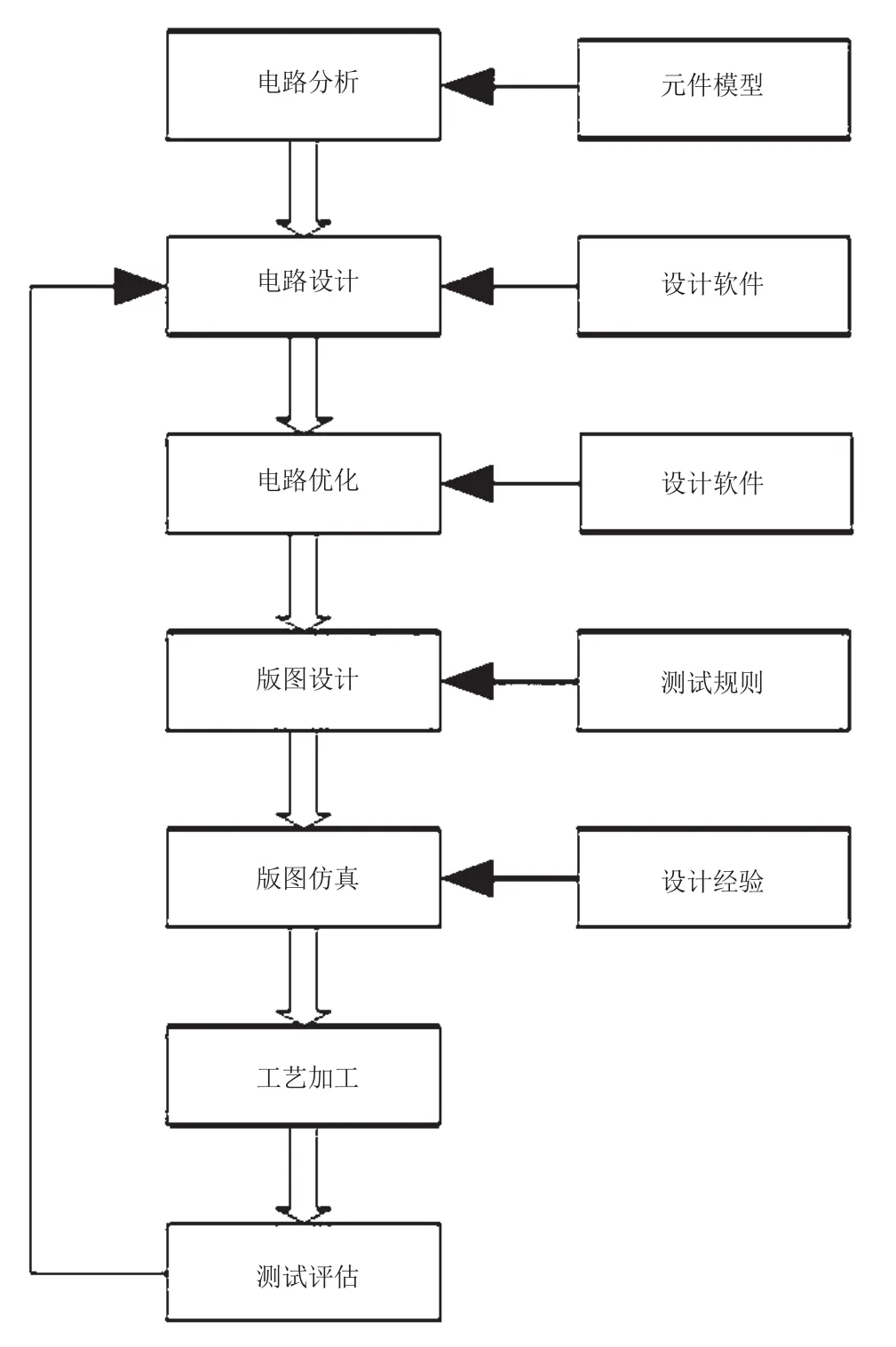

設計GaN單體微波集成電路(Monolithic Microwave Integrated Circuit,MMIC)功率放大器,整個電路設計的流程如圖1所示。

圖1 MMIC電路設計流程

(1)電路分析。在確定芯片工藝種類后,仿真該單片工藝下不同晶體管尺寸pHEMT器件的直流與射頻性能,確定晶體管使用的偏置條件,規劃芯片電路拓撲結構。

(2)電路設計。利用電路仿真軟件對所選擇的晶體管進行源級負載牽引與漏極負載牽引,仿真出晶體管的最佳源極阻抗與漏極阻抗后,用工藝庫中的器件模型設計晶體管之間的匹配網絡。通過改變匹配網絡中的各元器件參數值,確保電路在全工作頻帶內可以穩定工作。

(3)電路優化。搭建晶體管之間的匹配損耗電路后,綜合考慮級間增益、輸出功率及功率平坦度、功率附加效率(Power-Added Efficiency,PAE)、每一級電路的穩定性以及芯片面積等,優化仿真,使整個電路性能達到最優。

(4)版圖設計。完成芯片各項射頻性能指標仿真后,需要設計芯片版圖。繪制Layout時,在芯片面積達到最小的同時應盡量減少各無源器件之間的射頻耦合、微帶線和微帶線之間的耦合串擾以及加電微帶線可能交叉的問題,既要保證芯片的射頻性能指標,又要確保實際工藝加工上的可實現性。

(5)版圖仿真。完成最后的版圖排版后,需要對最終版圖進行仿真。電路仿真軟件有強大的電磁仿真能力,結合射頻電路設計師的設計電路經驗對版圖進行微調,進一步優化芯片射頻指標。

(6)工藝加工。當最終的版圖在仿真軟件中仿真完成后,設計師需要使用專業版圖軟件準確無誤地畫出最終的版圖,送到Foundry去加工并進行流片。

(7)測試評估。芯片流片回來后,在微波探針臺對設計芯片的每項射頻性能指標進行評估測試。一旦探針臺測試數據不符合設計要求,設計師就需要對芯片進行重新設計改進,直至流片測試數據符合最初的設計要求為止。

2 MMIC芯片設計

功率放大器在實際電路設計中采用4級級聯放大,前級選用1個300 μm(單指柵寬為50 μm)的單胞器件,第二級選用兩個300 μm(單指柵寬為50 μm)的單胞器件,第三級選用4個300 μm(單指柵寬為50 μm)的單胞器件,第四級采用8個360 μm的單胞晶體管來完成功率合成(總柵寬為2 880 μm),滿足10 W功率輸出指標要求。采取并聯方式可以合理分散晶體管熱源,從而降低芯片的熱阻,進一步提高器件的可靠性。設計芯片的最終拓撲采用對稱結構,芯片輸入級和第二晶體管、第三晶體管級間采用低通有耗匹配網絡,這樣可以擴展帶寬,提高芯片的小信號增益。芯片輸出級使用帶通濾波網絡,可以有效抑制2次諧波,在保證輸出功率滿足要求的前提下,提升芯片的工作效率。除此之外,為了提高本芯片的工作穩定性和小信號增益帶內平坦度,4級芯片均采用有耗匹配方法。

3 芯片加工與測試

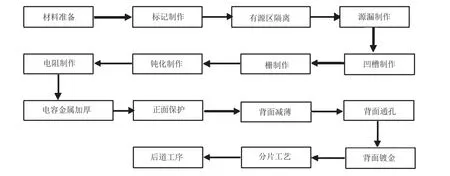

根據產品性能指標要求,本文設計的Q波段功率放大器芯片采用0.15 μm GaN pHEMT芯片工藝,具有功率密度大、批產一致性高等特點。MMIC的主要加工工藝流程如圖2所示。

圖2 MMIC加工工藝流程

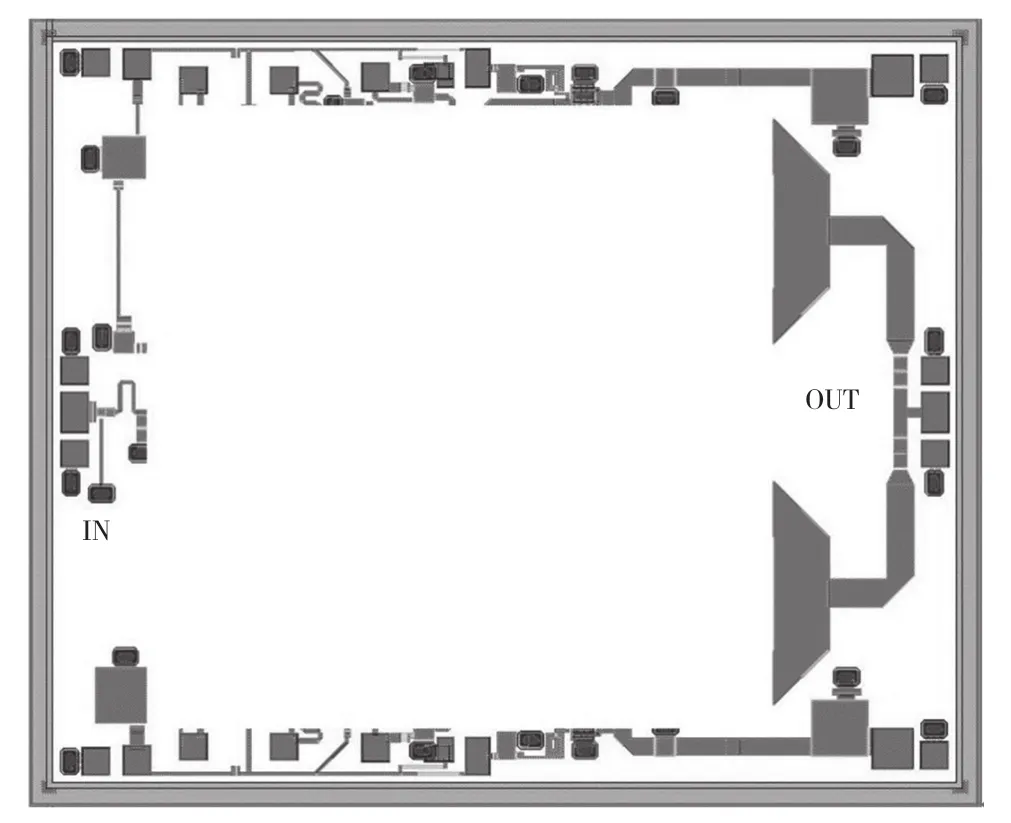

對材料結構進行分析和研究,加強通用工藝能力建設,對器件的制造工藝進行嚴格控制,通過優化設計生產兼顧線性的高效率、高功率密度GaN HEMT材料,從而獲得良好的器件性能。最終的電路版圖如圖3所示。

圖3 芯片最終版圖

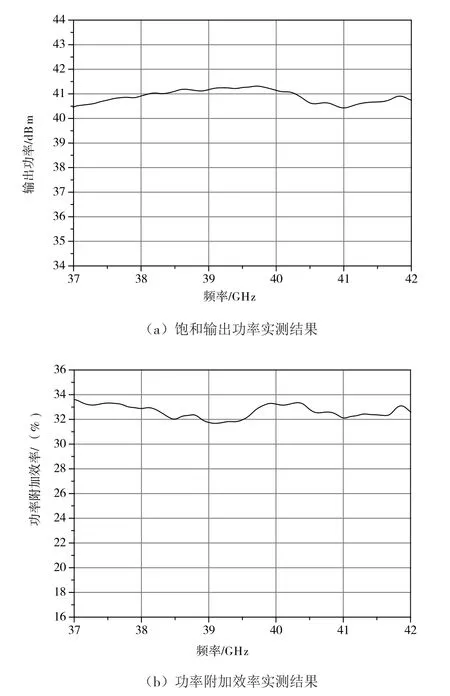

基于GaN pHEMT工藝制作電路,采用氮化硅進行鈍化隔離保護。制作電路中使用的芯片電容,對晶圓背面和地孔電鍍Au完成元器件接地,降低源電感。設定工作電壓為20 V、脈沖寬度為100 μs、占空比為10%、測試頻率為37~42 GHz,芯片飽和輸出功率實測結果如圖4(a)所示,功率附加效率實測結果如圖4(b)所示。

根據圖4可知,本文研制的功率放大器芯片實測的飽和輸出功率大于40 dBm、功率效率大于30%,符合預期目標,應用效果較好。

圖4 芯片性能測試結果

4 結 論

基于0.15 μm GaN HEMT單片工藝設計了一款適用于37~42 GHz的波段功率放大器芯片,電路使用4級級聯放大的拓撲形式,利用微帶線、到地電容實現芯片射頻輸入級、輸出級以及其他各級間的阻抗匹配。該放大器的實際測試結果符合預期,具有一定的參考意義。