氮化鎵功率器件塑封工藝技術研究

熊麗萍 饒錫林 馮學貴

(1.東莞職業技術學院,東莞 523808;2.廣東氣派科技有限公司,東莞 523330)

近年來,半導體技術發展迅速,集成電路產業規模不斷擴大。5G 時代的到來,對射頻器件所用半導體材料提出了新要求。氮化鎵(GaN)由于其大禁帶寬度和高飽和電子遷移率成為該領域的新興材料,在大功率、射頻、高頻微波等應用領域具有良好的應用前景[1]。

集成電路產業是當前全球高新技術產業的核心,是發展戰略性新興產業的基礎,對信息化發展與綜合國力提升具有重要的戰略意義。GaN 射頻功放技術對5G 通信意義重大。5G MIMO 架構基站GaN 功放及射頻芯片95%的市場,被CREE、博通等射頻巨頭壟斷[2]。5G 產品的變頻較高,GaN 器件工作時電流大、功率高,溫度可達250 ℃,因此封裝結構的散熱設計非常重要。此外,GaN 功率器件采用金屬或陶瓷封裝,成本較高。因此,在保證性能和可靠性的條件下,采用塑封技術實現產品成本降低是其商用的前提條件。

本文將以一款GaN 雙邊扁平無引腳封裝(Dual Flat No-lead,DFN)的開發為例,圍繞GaN 器件的封裝結構設計、塑封材料選擇、封裝工藝優化、封測中常見的問題分析與解決進行闡述。

1 封裝結構設計

5G 宏基站超大功率GaN 射頻功放電路在工作狀態下的管芯溫度可達160 ~230 ℃,功耗達80 W,損失功耗可達500 W[3]。對于塑封封裝來說,如果不能及時釋放過高的熱量,塑封體內溫度會進一步上升。溫度變化會影響導體的導電性,從而影響射頻信號的穩定性。同時,熱量積聚,溫度會持續上升,導致封裝材料受熱膨脹。不同材料的膨脹系數會有所差異,如銅材膨脹系數為0.167×10-4/℃,樹脂的膨脹系數為10-6/℃。膨脹系數差異會產生熱應力,當熱應力超出芯片能承受的最大彈性模量時,會發生芯片開裂[3-4]。為了提高功率器件的熱可靠性,需要分析器件的熱源集中區域,并通過優化設計及時散發器件產生的熱量,避免燒毀芯片,提升器件橫向和縱向的散熱通道和能力,快速降低器件核心發熱區域結溫。

1.1 異構封裝設計

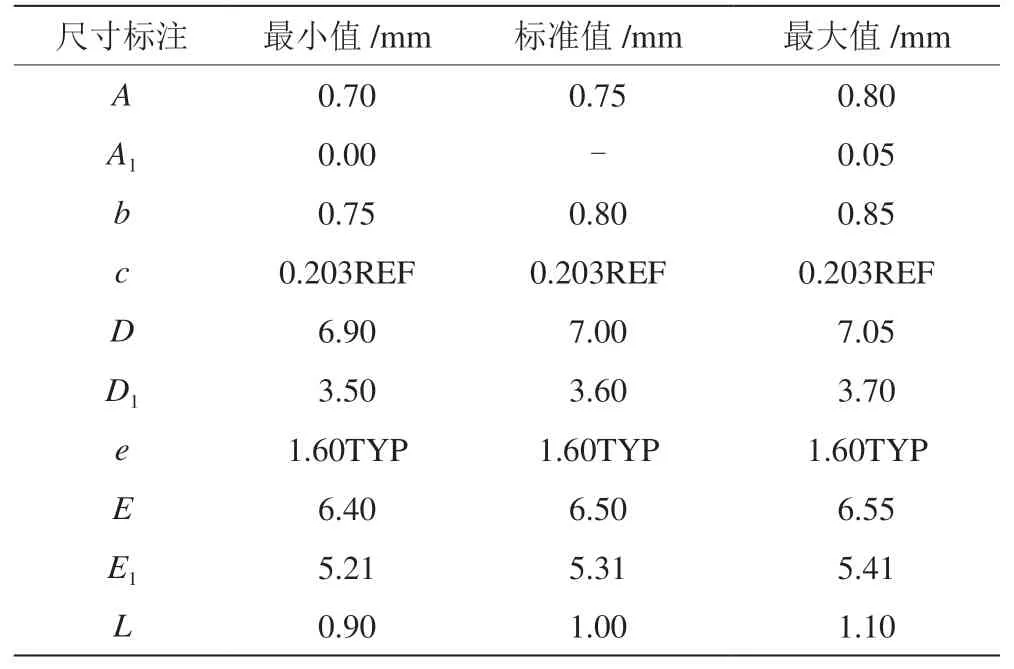

方案中的GaN 塑封結構如圖1 所示,尺寸如表1所示。采用異結構材料進行封裝,實現器件內部發熱單元高熱導率散熱結構的異構集成,保證器件封裝過程中內部核心發熱單元與封裝散熱單元建立良好的散熱通道。以厚銅板作為散熱片,薄銅材作為引線管腳通過鉚接技術實現互聯形成穩定的結構。保證良好的散熱性,同時能進行熱吸收。芯片與散熱片連接材料選用具有高導熱性的燒結銀膠。

表1 DFN6.5×7-6 塑封尺寸

1.2 防潮結構設計

在塑封封裝器件中,潮氣侵入會導致電路發生化學腐蝕,從而導致封裝失效。為了提高該封裝的潮敏等級,防止水汽的侵入,散熱片底面設置多臺階,散熱片正面設計有鎖定溝槽。這樣不僅能防止水汽侵入,而且可以加大底部散熱片與樹脂的結合力。

1.3 棕化設計

使用塑料封裝替代原有的金屬陶瓷封裝,成本低,可推廣性好,且能實現國產替代。但是,由于氮化鎵器件高功率密度的特點,其工作溫度高,對產品可靠性要求高。因此,在引線框架上使用特別設計,增加棕化工藝,提高表面粗糙度,增大框架與環氧樹脂的接觸面積,達到提高產品可靠性的目的。

2 塑封材料及工藝

集成電路塑封工藝是指將高溫熔融的環氧樹脂填充到特定的模具中,對芯片進行包覆。集成電路塑封封裝與金屬或陶瓷封裝相比,成本低,適于自動化生產。但是,由于塑封封裝屬于非氣密或半氣密封裝,抗潮濕性較差,且熱穩定性不佳。

隨著塑料封裝的模塑材料、引線框架和生產工藝已經不斷完善和改進,塑封封裝在集成器件中得到了廣泛采用。環氧樹脂模塑料(Epoxy Molding Compound,EMC)是一種熱固性材料,由環氧樹脂、固化劑、固化促進劑、填料以及其他改性成分共同組成,在塑封封裝材料中應用最廣泛,具有絕緣性良好、耐腐蝕性強、粘接強度高以及力學性能良好等優點[4]。

2.1 高玻璃化溫度Tg 低應力的環氧樹脂的優化

GaN 射頻功放塑封器件工藝要求高,飽和功率輸出達到200 W,器件核心溝道溫度達到200 ℃以上,而常規塑封料Tg溫度只能達到130 ℃。為了滿足GaN 器件高溫工作條件,應對塑封料材料成分、比例、固化條件和固化應力釋放等多種參數進行研究和優化設計,保證高溫條件下材料良好的散熱。材料成分穩定,且高溫材料間應力控制在正常水平,器件內部不出現分層現象[5]。同時,為了滿足背部應力要求,選用低應力高Tg的塑封樹脂,并在散熱片正面做凹槽,減少塑封應力。使用的環氧樹脂Tg高達160 ℃,通過熱分析技術對不同模塑料的聚合程度、熱膨脹系數、玻璃化溫度Tg以及剪切模量等進行測量優化。結合封裝過程參數,優化塑封后集成芯片翹曲程度和塑封流道,以適應高頻高功率的氮化鎵器件的使用需求。

2.2 塑封工藝

在注塑工藝過程中,塑封料的組分不僅決定塑封料的性能,還決定塑封器件的可靠性。此外,塑封料的注塑工藝對塑封后器件的翹曲變形和鍵合絲的偏移有直接影響。因此,需要結合塑封料和注塑工藝對塑封器件的可靠性進行整體分析并進行優化設計,以提高塑封器件的可靠性。

3 GaN 封裝工藝流程及異常處理

3.1 塑封工藝流程

GaN 器件DFN 塑封工藝流程如圖2 所示。先是晶圓通過劃片工藝后被切割為小的晶片(Die),然后將晶片安裝到引線框架上。GaN 裝片前先進行了一次裝片和固化,待GaN 裝片固化完成后進行等離子清洗,接著引線鍵合,以保證芯片端子與框架引腳的電通路與信號通路,再對獨立的晶片用環氧樹脂塑封。塑封后還要進行電鍍、打印以及切割等步驟,封裝完成后進行測試和檢查,最后包裝出貨。

3.2 GaN 裝片膠空洞問題分析

空洞會影響產品導電性能和散熱性能,特別是產品溫度較高點出現銀膠空洞會嚴重影響器件性能甚至損壞器件。GaN 大功率器件具有超高的能量密度,對產品空洞提出了極為嚴苛的要求。設計中的GaN 產品裝片后發現裝片膠空洞,如圖3 所示。GaN 芯片位置淺色不規則形狀為裝片膠空洞,空洞面積率超過30%。裝片膠空洞會影響產品的電性能和熱性能,需要改善解決。

抽取空洞產品,測量產品的膠厚(BLT)和芯片傾斜度,發現空洞產品的膠很薄,平均厚度約在8 μm,芯片傾斜度無異常。通過與裝片膠供應商的技術人員確認材料屬性后,判斷裝片膠厚度太薄造成產品出現空洞。選取不同裝片膠厚進行實驗,對比空洞結果得出增加膠厚到30 μm 以上可以明顯減少空洞的結果。

考慮膠中溶劑的揮發性,參考供應商推薦的固化溫度曲線,設定固化烘箱的溫度曲線,可將GaN 裝片膠空洞面積率控制在5%以內。GaN 芯片膠厚越大,芯片的傾斜會相應增加,需要適當放松對芯片的傾斜度控制。可見,在GaN 塑封工藝中,選用燒結銀膠替代傳統銀膠,同時優化裝片工藝參數,設置合適的固化曲線,可大幅降低空洞風險。

3.3 分層問題分析

在GaN 塑封DFN6.5×7-6 產品開發過程中,打樣后基島邊緣和切割道邊緣的外管腳有分層現象,如圖4 所示。

觀察分層情況,基島邊緣都是裸銅,中間鍍銀,分層都在裸銅框架那一圈,由此可推測造成分層的原因在于裸銅氧化和銅剝離。根據IQC 來料檢驗的高溫銅剝離實驗,可排除銅剝離問題,因此裸銅氧化應該是基島邊緣分層的根本原因。

優化設置烘箱程序,并將切割刀片尺寸和轉速調整到最佳,解決了烘烤后的銅氧化問題,但切割后仍然存在基島邊緣分層和切割外管腳分層現象。經分析,可能是鍵合溫度太高導致框架氧化,且該產品38 根線,焊線速度比普通的DFN/QFN 焊線速度慢一半,因此同一單元的產品在加熱塊上加熱的時間會比普通的DFN/QFN 產品多一倍。因此,改用單列壓板鍵合,減少產品在加熱塊上加熱時間;將鍵合溫度由200 ℃調整到180 ℃,盡量減少框架的氧化;塑封、電鍍后產品掃描無分層問題,切割后除了切長邊的第1 刀有6 粒外管腳分層外,其余部位無分層現象,如圖5所示。

4 結語

以一款GaN 射頻功率器件DFN 封裝工藝為例,給出其異構結構設計、塑封材料選擇、封裝制造流程、空洞和分層問題的討論和分析。然而,GaN 作為第三代半導體材料的代表,在封裝制造領域仍有許多技術有待進一步探究。今后需針對GaN 裝片作業高精度要求進行工藝和平行線弧的間距、精度高要求的制程工藝設計,以優化大功率GaN 芯片的高熱導和高電導要求的裝片工藝。