VSC型電力擾動發生裝置的設計與實現

齊 磊,趙 舒,張寧欣,曹軼男,韓 錚

(1.遼寧省安全科學研究院,遼寧 沈陽 110004;2.國網遼寧省電力有限公司資金集約中心,遼寧 沈陽 110004;3.華電能源股份有限公司齊齊哈爾熱力分公司,黑龍江 齊齊哈爾 161000)

近年來由于科技飛速發展,電力系統的負荷結構發生了較大變化。大量非線性負荷引發了電網電壓的波動、畸變、失衡等電能質量問題。隨著我國工業自動化水平的提高,很多精密自動化設備對電能質量非常敏感,而電能質量問題的出現在不同程度上引發這些設備的運行障礙。因此,電能質量的監測、分析與治理已成為電能供應與利用領域的重要課題[1]。在檢驗電能質量分析理論的正確性或者研發電能質量治理裝置時,都需要電力擾動發生裝置來提供擾動信號源,電力擾動發生裝置還可以對電力設備在擾動工況下的工作特性進行測試。目前,國內外電力擾動發生裝置的研究趨勢正在向靈活性、可調節性、高精度等方向發展。

國內傳統晶閘管可控電抗器型電力擾動發生裝置存在大量吸收無功的問題且擾動類型較少。國外電力擾動發生裝置多采用移相電路調節變壓器抽頭的方式來產生擾動,這類裝置具備成本低、工作穩定等優點,但是存在設置不便、擾動類型單一等問題。如美國亞利桑那大學的George Karady博士研發的電力擾動發生裝置[2],利用模擬移相電路控制線路開關與變壓器抽頭,裝置只能實現電壓暫降波形,無法做到連續調整。同步調相機可較為方便的實現電力擾動發生,但是質量與體積限制了其應用范圍。隨著電力電子技術發展,電力電子變流裝置的靈活性強、可靠性高等優勢日益凸顯出來。華北電力大學電能質量實驗室采用不可控電壓源型逆變器(voltage source inverter,VSI)實現了電力擾動發生[3],擾動裝置具備控制靈活、類型豐富等優點。但是,整流單元不可控一方面降低了直流電壓的穩定度,另一方面還向電網注入了諧波電流。

本文針對以往電力擾動發生裝置存在的不足,提出了將電壓源型變流器(voltage vource converter,VSC)應用于電力擾動發生裝置的構想。首先介紹了主電路參數的選擇方法,對基于直流電壓穩定的功率控制器進行討論;最后經仿真與試驗驗證結論。結果表明,該裝置工作性能良好且穩定,具備工程應用的潛力。

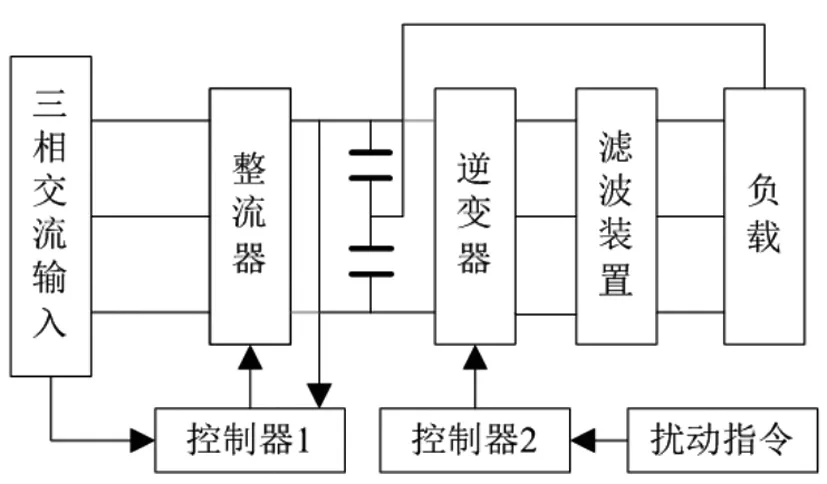

1 裝置結構

VSC型電力擾動發生裝置的結構如圖1所示,可控整流器將交流電壓變換為高精度直流電壓源,逆變器控制產生指定擾動電壓波形作用于負荷。

圖1 裝置結構

1.1 三相靜止abc數學模型

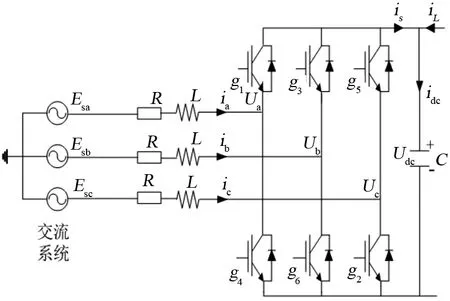

首先做出假設:①三相無窮大電源理想對稱;②理想功率開關,忽略開關延遲。單側VSC拓撲結構如圖2所示。

圖2中:Esa,Esb,Esc為交流電源電壓;ia,ib,ic為交流輸入電流;Ua,Ub,Uc為變流器交流測出口電壓;is為整流器側直流電流,idc為直流電容電流;iL為負載電流;R為等效電阻;L為交流濾波電抗;C為直流側電容;Udc為直流電容電壓;g1-g6為功率開關觸發脈沖信號。

圖2 單側VSC拓撲結構

變流器的數學模型為[4]

(1)

1.2 交流側電感設計

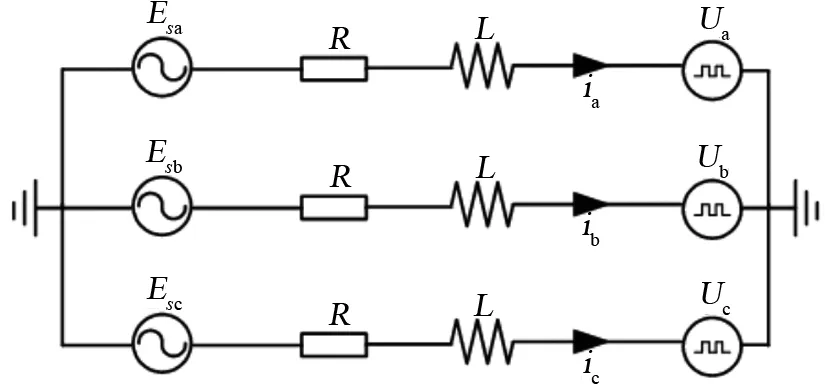

由式(1)得出交流側等效電路如圖3所示。由于濾波電感對高頻電流分量存在抑制作用,因此變流器出口只考慮其基波分量;濾波電感存儲了無功功率,無功功率在三相間流動,在裝置容量一定時,大量的無功會減小有功功率向負荷的傳輸,降低了裝置的效率,因此濾波電感的選擇存在上限;濾波電感也起到抑制電流突變的作用,以防止濾波電感過壓,因此濾波電感的選擇存在下限。

圖3 交流側等效電路

濾波電感取值限制定義如下[5]。

a.穩態有功傳輸能力指標。電感電壓一般不大于交流電源額定電壓的10%,這反映了直流電容電壓的穩定能力。

b.暫態運行性能。一個控制周期內電流變化量小于交流側額定電流的10%,這反映其暫態工況約束。

c.濾波性能電流畸變率(total harmonic distortion,THD)≤5%,以減小裝置對電網的諧波污染。

按上述指標得到電感選擇為

(2)

式中:PL為指標與裝置容量;Ts為控制周期;cosφ為功率因數;ω為角頻率。

1.3 直流側電容設計

式(1)表明增大直流側電容C可以減小電壓的波動,但是限于裝置的體積與研發的成本,C又不能選擇過大。引起直流側電壓波動的主要原因是整流器與逆變器瞬時功率差,在測試設備時,功率變化最大時刻發生在加載的瞬間,直流側電容的功率突然由零變為P;而在實驗室進行電能質量問題研究時,還有可能出現功率倒灌的情況,即逆變器由吸收最大功率-Pmax突然變為回饋最大功率Pmax,由此引起直流側電壓波動最為劇烈。定義在一個控制周期內直流側電壓波動率在10%的指標,根據電容元件的特性,電容C的取值為

(3)

1.4 擾動負荷選擇的約束

在保持直流側電壓穩定的前提下,擾動負荷的選擇是有局限的。當負荷容量超出裝置容量時,直流側電壓將不再穩定,出現電壓跌落。此外,電流大小也不應超過功率開關的最大允許電流,否則會燒壞器件。因此,負荷的最小值受到上述2方面的約束,如式(4)所示。

(4)

式中:Smax為交流電源的容量;Imax為功率開關通過的最大電流。

2 裝置控制器設計

2.1 dq坐標系下動態數學模型

對于三相對稱電源,令d軸與空間合成矢量重合,q軸超前d軸π/2,則Esd=Um,Esq=0,得到整流器在dq旋轉坐標系下的基爾霍夫方程與功率方程分別如式(5)、式(6)所示。

(5)

(6)

式中:id,iq為dq軸電流;md,mq為dq軸功率開關函數。

整流器以控制直流側電壓穩定為目標,其本質是控制電源向直流側電容注入的有功功率。按照式(6)設計功率控制器,交流側電源注入VSC的有功功率與無功功率分別與dq軸電流成正比,由此確定直接電流控制方案。

2.2 狀態反饋線性化解耦方法

由式(5)可知,id與iq之間存在耦合,即P與Q之間存在耦合,這樣給控制器設計帶來了極大的不便。非線性狀態反饋線性化理論是解決這一問題的強有力工具[6-7],反饋線性化通過坐標變換和狀態反饋使非線性系統在大范圍內實現線性化,在多輸入多輸出系統實現線性化的同時,滿足解耦控制的需要。

解耦可控線性系統狀態方程與輸出方程為

(7)

狀態量z1,z2分別等于id,iq。根據最優控制理論,確定新的輸入變量υ1,υ2與狀態變量存在的關系為

(8)

由式(7)、式(8)可以看出,給定一組dq軸電流的參考值idref與iqref,即得到一組輸出變量id和iq,進而達到直接控制電流的目的。由此推導出功率開關函數md和mq如式(9)所示,其通過正弦脈寬調制(sinusoidal pulse width modulation,SPWM)技術作用于功率開關。

(9)

2.3 控制器動態性能優化

由式(7)可知,電流閉環傳遞函數為一階慣性環節,具有良好的動態性能。在實際裝置中,由于數字化處理器的參與,延遲效應是不可避免的;此外,交流側等效電阻在裝置運行中也會產生變化。上述2點都會對控制器性能帶來影響,本文采用PI校正環節來提高控制器的動態性能。

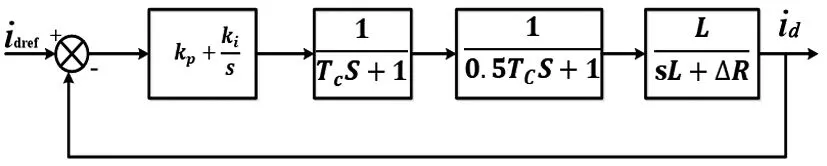

計及電阻參數擾動與系統延遲環節的電流控制動態結構如圖4所示。

圖4 電流環動態結構

忽略高次項,得到其開環傳遞函數為

(10)

采用零極點對消的方法,利用PI校正環節的零點消去由電阻參數擾動引發的極點,以抵消其帶來的影響,并取最佳阻尼比ξ=0.707,得到電流環PI校正環節整定為

(11)

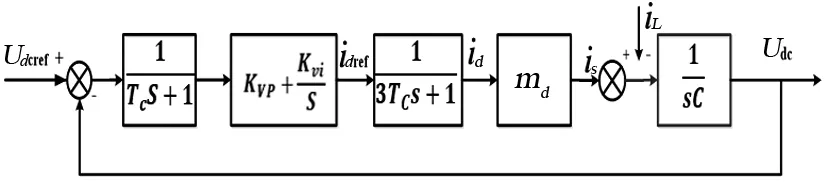

直流側電容電壓與交流電源注入VSC的有功功率有關。根據式(6)在d軸電流環外加直流側電壓環控制并附加PI校正環節,構成雙閉環系統。其動態結構如圖5所示。

圖5 電壓環動態結構

系統包含了給定直流側電壓和負載干擾電流2部分響應。根據終值定理,該系統的穩態誤差為

(12)

由此可見,系統穩態誤差不受負載干擾電流影響,穩態時無靜差。電壓閉環特征方程為

(13)

對于高階系統,為了得到所需要的動態性能和穩態性能,在工程上通常的處理方法是將其中2個極點配置為1對共軛極點,另外2個極點配置在距虛軸很遠的地方(一般n取10)[8]。系統期望的特征方程為

(14)

對比式(13)與式(14),得到電壓環PI校正環節整定后參數為

(15)

3 仿真算例分析

3.1 仿真算例參數

經過主電路參數設計和PI控制器整定計算,裝置主電路參數如表1所示,控制器仿真參數如表2所示。

表1 主電路參數

表2 控制器仿真參數

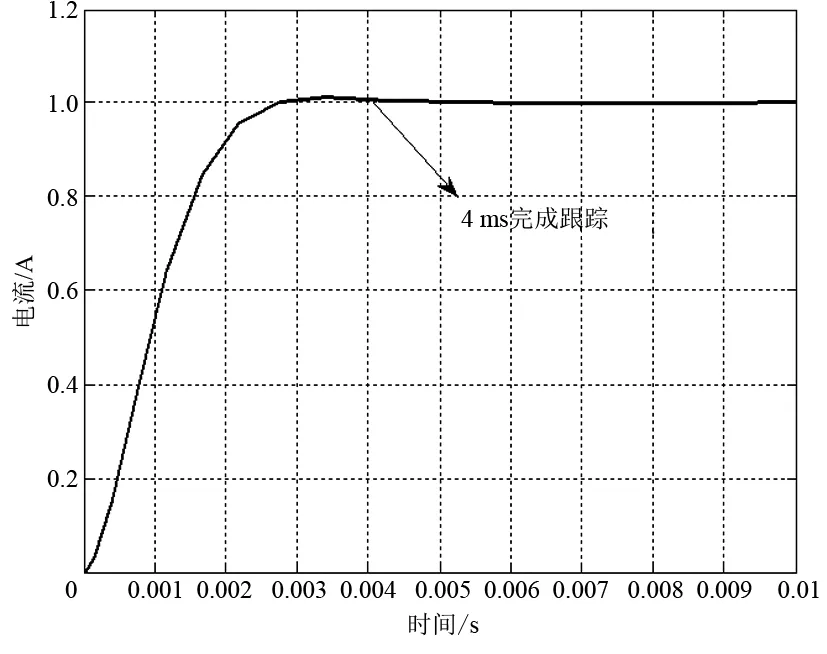

3.2 控制器性能驗證

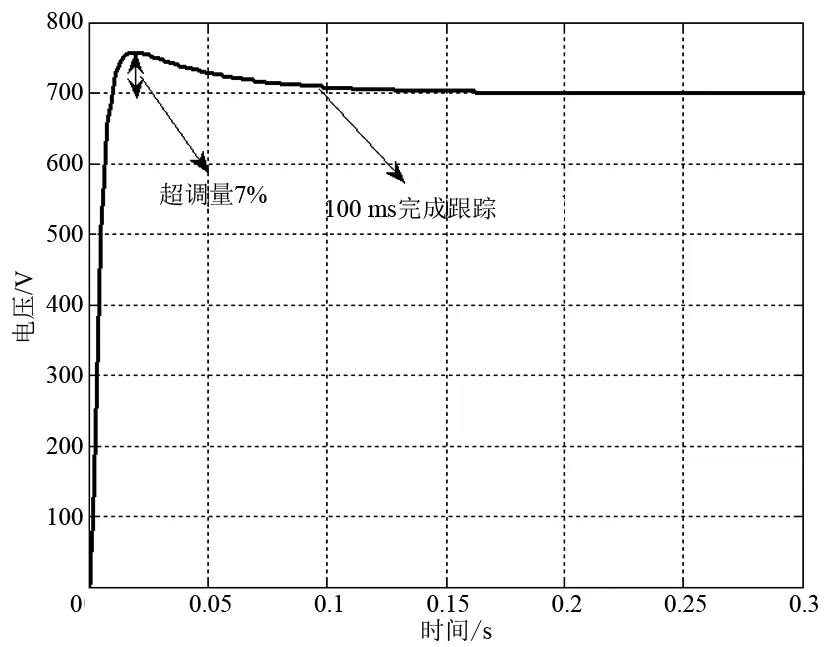

在MATLAB/Simulink環境下搭建雙閉環控制系統,電流和電壓的單位階躍響應波形如圖6所示。電流經過4 ms完成跟蹤,與理論值基本一致,超調很小且穩態時無靜差;直流側電壓經過100 ms達到穩態值700 V,且穩態時無靜差,超調量7%。動態性能滿足指標,仿真結果驗證了控制器設計的正確性。

(a) 電流環單位階躍響應波形

(b) 電壓環單位階躍響應波形圖6 控制器性能驗證

3.3 裝置仿真研究

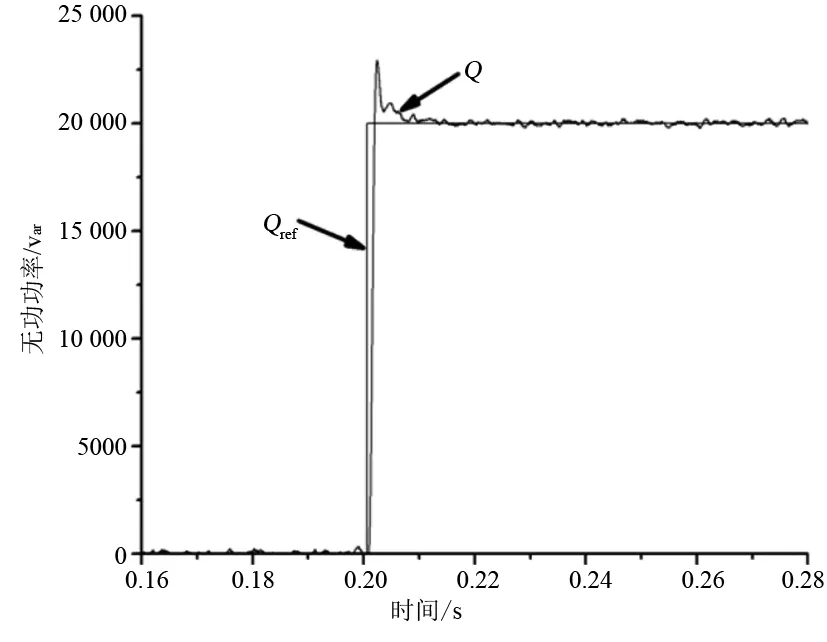

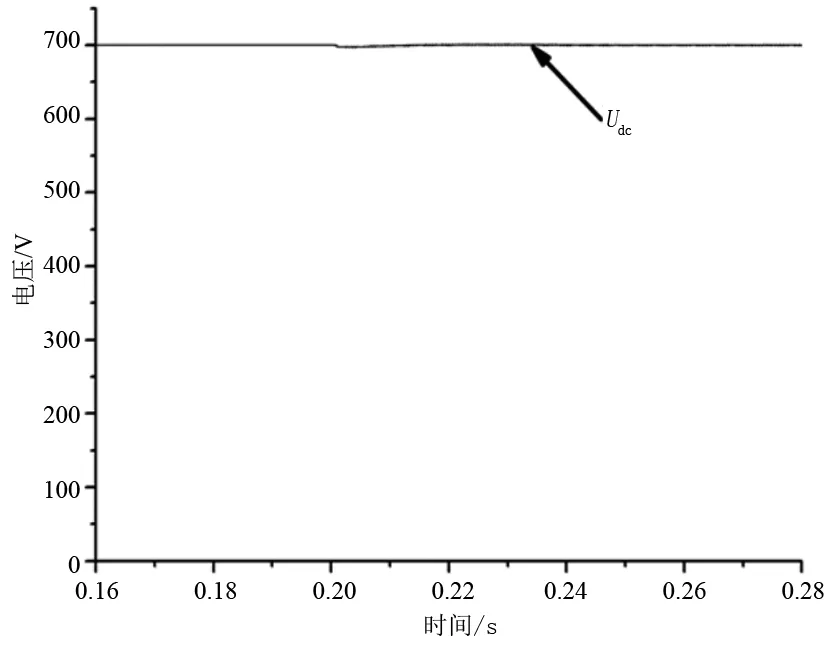

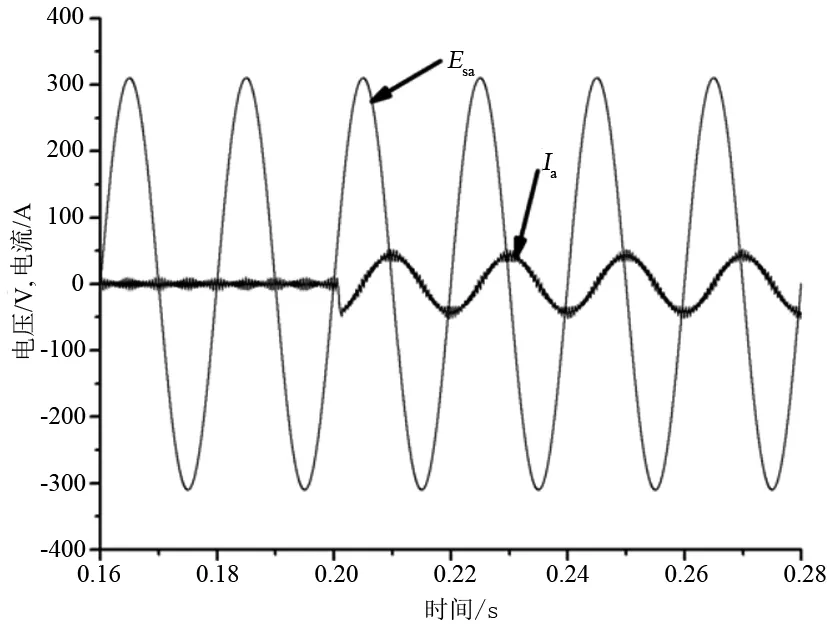

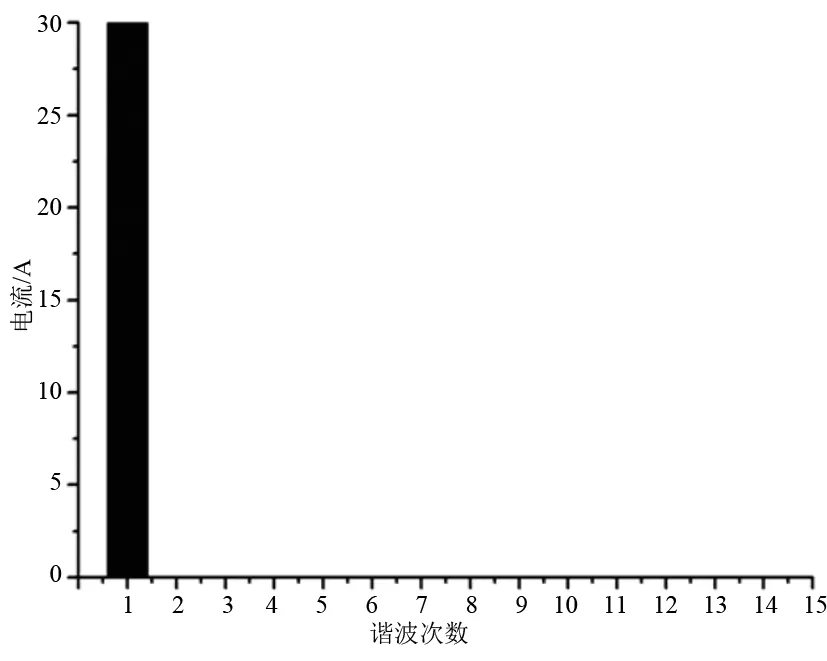

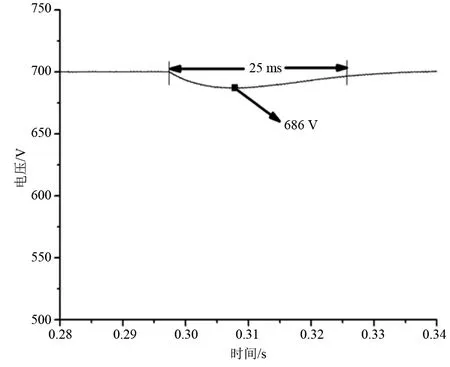

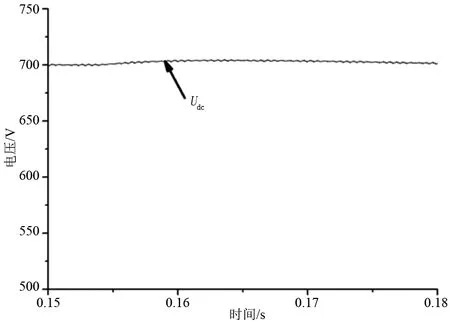

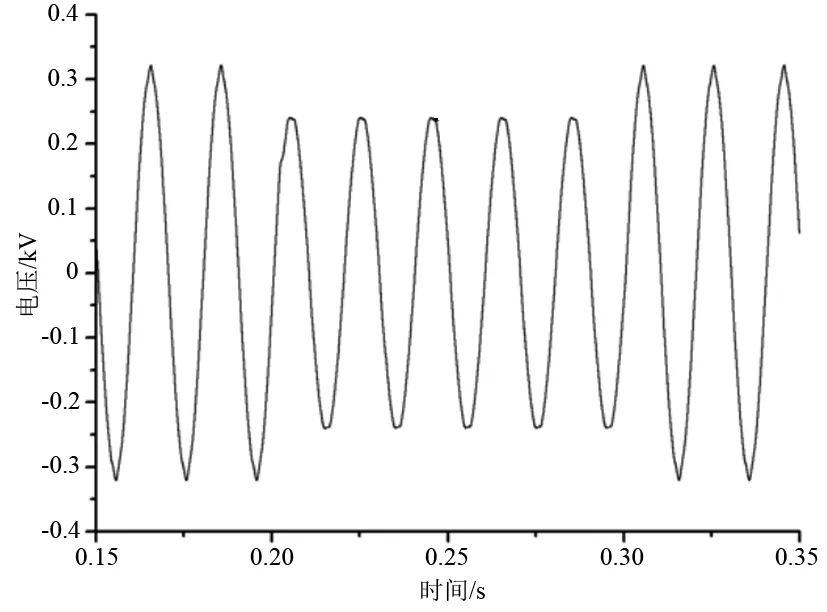

圖7驗證了整流器的工作性能。整流器空載運行工況下,在0.2 s時控制交流系統流入整流器的無功功率由0躍變至20 kvar,即Qref=20 kvar,經5 ms左右功率完成跟蹤,如圖7(a)所示;無功功率躍變并未對直流側電壓穩定造成影響,如圖7(b)所示;圖7(c)為交流側電壓電流波形,可以看出其相差90o的相位關系;圖7(d)為交流側電流頻譜圖,可以看出無低次諧波成分,不會對電網造成污染;圖7(e)為突然加載時直流電壓波形,經過1個周波左右恢復,最大變化率為2%,控制器抗外擾特性良好;圖7(f)為交流側等效電阻增大0.1 Ω時,直流側電壓基本無變化,說明控制器抗內擾的性能良好。

(a)無功階躍響應

(b)直流電壓

(c)交流電壓與電流

(d)電流頻譜

(e)直流電壓抗外擾

(f)直流電壓抗內擾圖7 整流器工作仿真波形

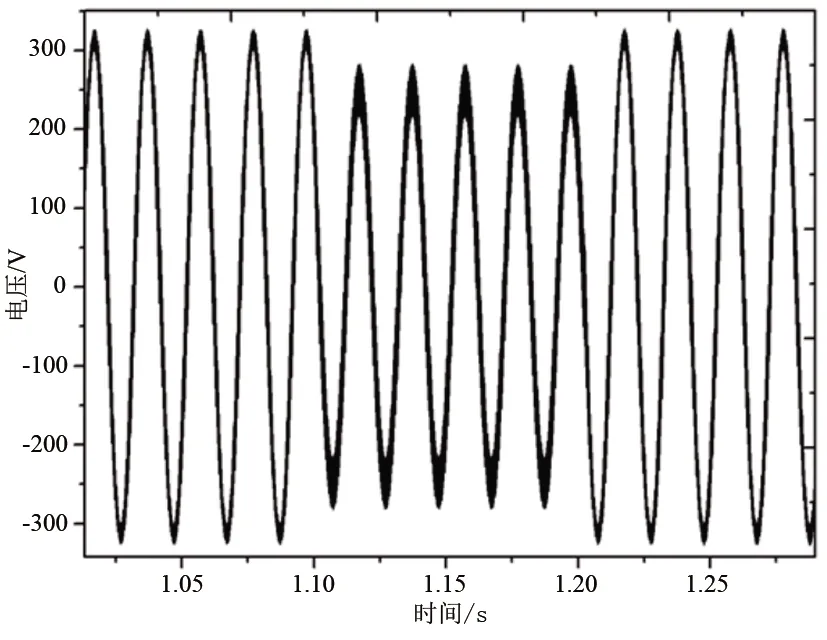

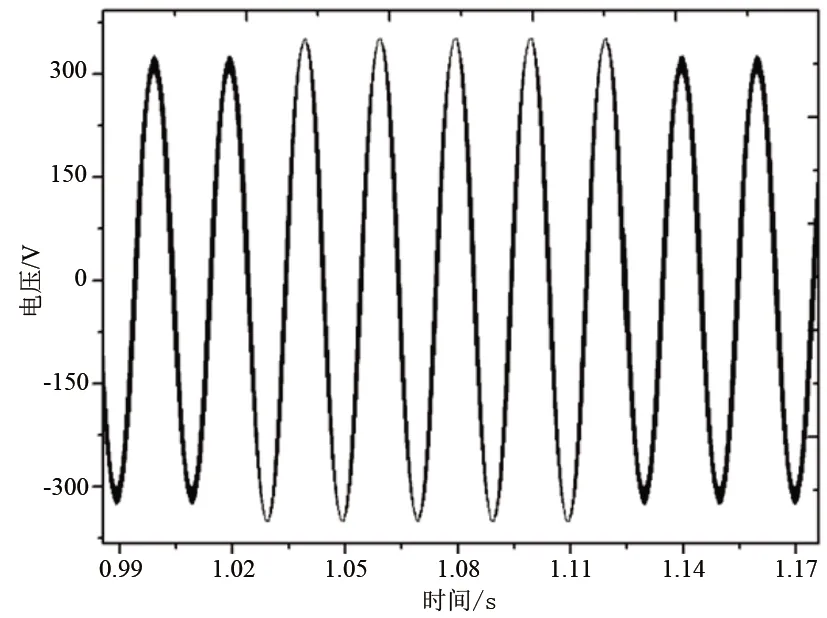

根據規則采樣法SPWM得到的幾種典型擾動波形如圖8所示,驗證擾動發生方法的可行性。圖8(a)為電壓暫降波形,降幅10%,持續4個周波;圖8(b)為電壓中斷波形,中斷4個周波;圖8(c)為基波電壓注入0.5基值的三次諧波波形;圖8(d)為三相電壓不平衡波形。

(a)電壓暫降

(b)電壓中斷

(c)諧波注入

(d)三相不平衡圖8 電力擾動仿真波形

4 試驗結果分析

4.1 擾動電壓波形輸出試驗

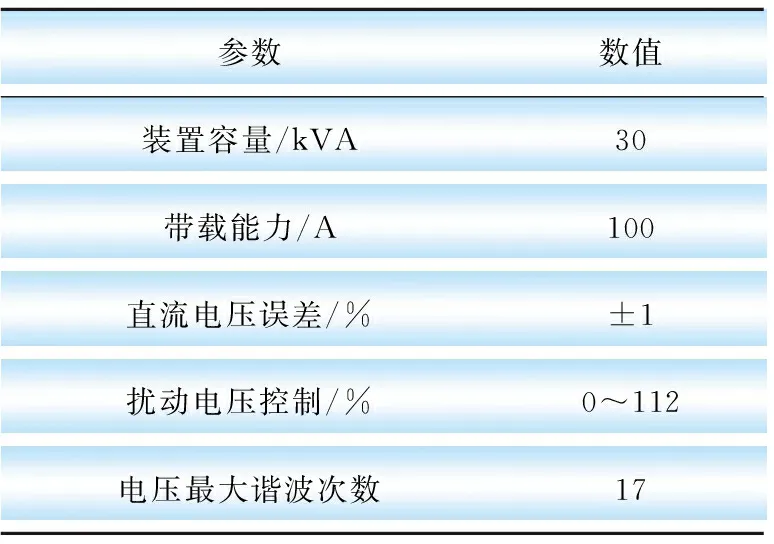

利用30 kVA背靠背變流器物理樣機進行試驗,控制芯片采用美國德州儀器(TI)公司的TMS320LF2812,該裝置技術指標如表3所示。

表3 裝置技術指標

該裝置實現如下幾種擾動波形。

a.電壓暫降。電壓暫降試驗波形如圖9所示,相電壓由220 V跌至173 V,跌落21.4%,持續時間為100 ms。

圖9 電壓暫降試驗波形

b.電壓暫升。電壓暫升試驗波形如圖10所示,相電壓由220 V升至232 V,升高5.5%,持續時間為100 ms。

圖10 電壓暫升試驗波形

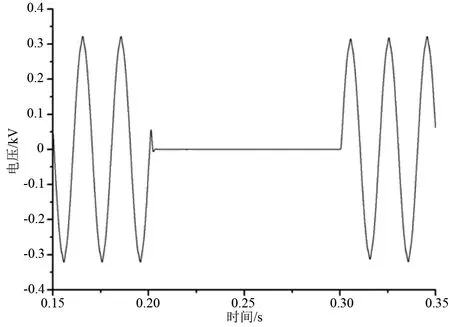

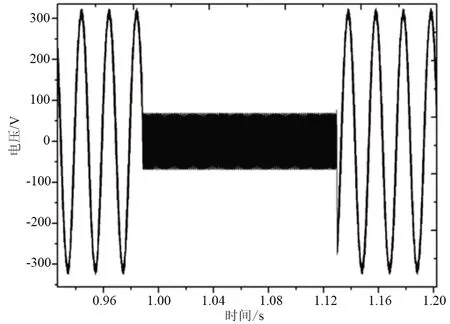

c.電壓中斷。電壓中斷是最為嚴重的電能質量事件,電壓中斷試驗波形如圖11所示,持續中斷時間為120 ms。

圖11 電壓中斷試驗波形

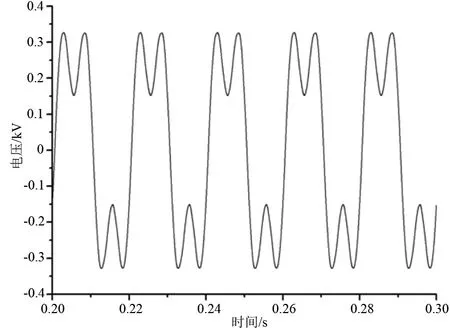

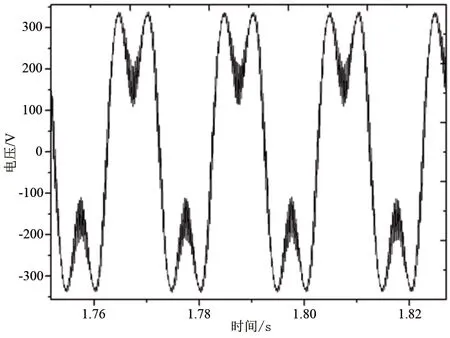

d.諧波注入。向基波調制波電壓疊加0.5基值的三次諧波電壓,如圖12所示。

圖12 注入三次諧波試驗波形

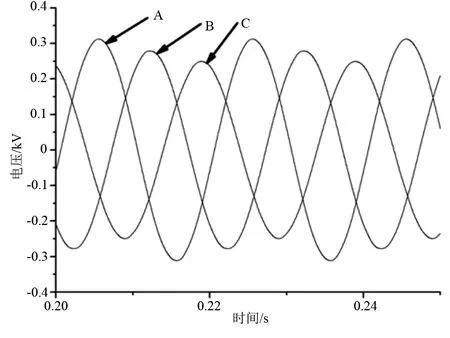

e.三相不平衡。通過控制三相調制波幅值不同來實現三相不平衡電壓輸出,不平衡度為32.5%的三相電壓試驗波形如圖13所示。

圖13 三相不平衡電壓試驗波形

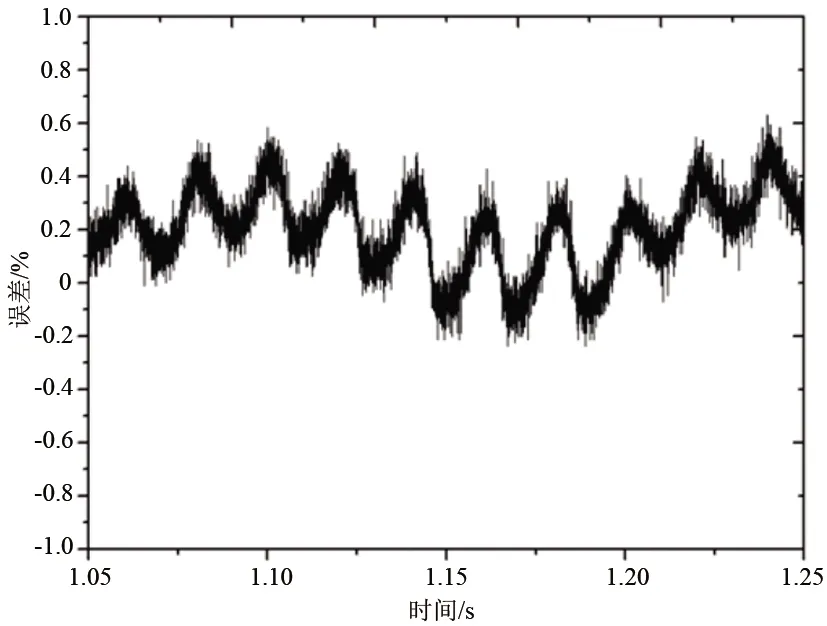

直流電壓的穩定性保證了輸出擾動波形的質量,圖14為在發生電壓暫降事件時的直流側電壓偏差。可以看出偏差為-0.2%~0.6%,電壓最大波動為6 V,滿足裝置指標。

圖14 暫降過程的直流電壓誤差

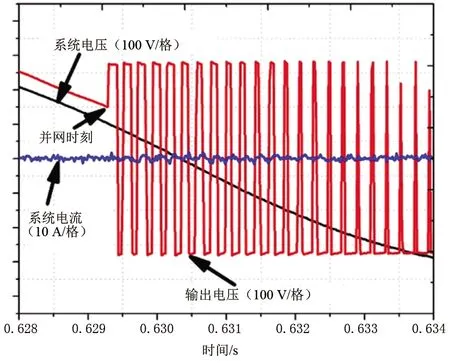

4.2 并網運行試驗

將該裝置負荷側通過50 Ω電阻接入電網并進行并網試驗。本文采用單相電壓過零并網方法,通過相鄰時刻采樣電壓相乘,當乘積為負數時即檢測到過零點。并網過程的試驗波形如圖15所示,結果顯示并網過程的電流波動較小。

圖15 并網過程試驗波形

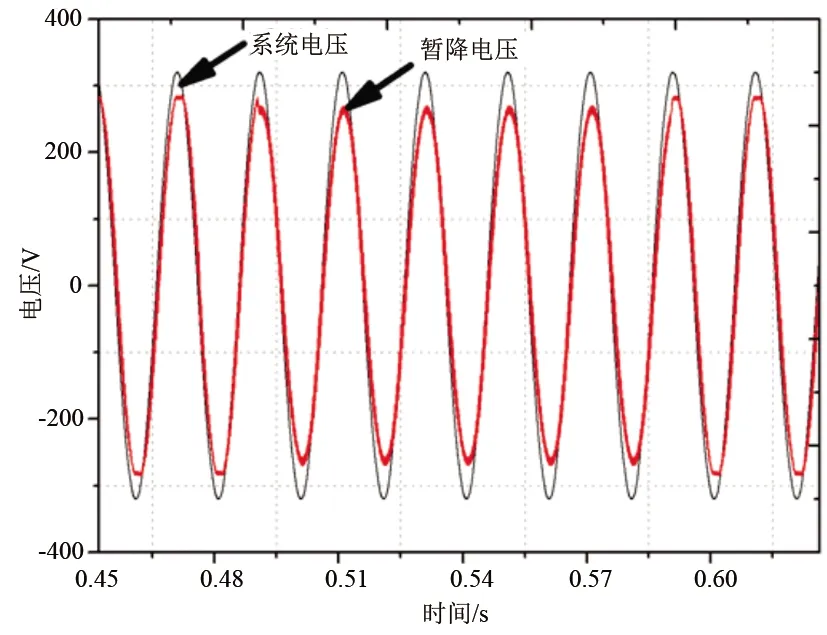

設定輸出電壓相位與電網電壓一致,輸出電壓幅值由280 V跌至265 V(跌落5.4%),持續時間為100 ms。并網后電壓暫降試驗波形如圖16所示。試驗結果表明,該裝置在并網運行后依然能穩定輸出電力擾動波形。

圖16 并網后電壓暫降試驗波形

5 結論

a.根據運行工況與功率控制理論設計裝置主電路與控制器的方法不僅正確且具備通用性。

b.仿真與試驗結果表明,VSC型電力擾動發生裝置具備諧波污染小、電壓精度高、擾動類型靈活等優點,具備工程應用的潛力。