國產化中頻接收模塊可靠性設計

張康雷,王彥革,殷鵬程,張 博,鄭榮磊

(上海航天電子技術研究所,上海 201108)

0 引 言

隨著國內集成電路技術的快速發展,國產高可靠性器件在航天工程中得到了普遍應用。目前,進口元器件在實際使用中存在諸多問題,如采購周期長、停產、部分無法進行性能參數、可靠性篩選等。空間電子設備所處軌道不同,受到的輻射影響也不同,空間輻射環境中的帶電離子會導致電子系統發生單粒子效應,嚴重影響航天器的可靠性和壽命[1]。空空通信機主要用于航天器之間的交會對接,不同型號運載火箭發射時,空空通信機所處的輻射環境和力學環境相當復雜,其中的頻接收模塊使用國產化抗輻器件進行設計,并為現場可編程門陣列(Field-Programmable Gate Array,FPGA)主芯片增加了力學加固工裝,加強了模塊可靠性。

1 硬件方案

空空通信機采用層疊式的安裝方案,中頻接收模塊安裝在最頂層,通過通信處理FPGA軟件和相應硬件后實現數據收發的雙向功能[2]。除完成數據收發功能以外,中頻接收模塊還需要具備遙控、遙測的功能,其遙控包括根據指令切換功率、工作模式等,遙測用于監測發射功率、單機溫度、當前工作模式等狀態以及實時監控模塊解碼功能、軟件功能、同步信息等是否正常[3]。

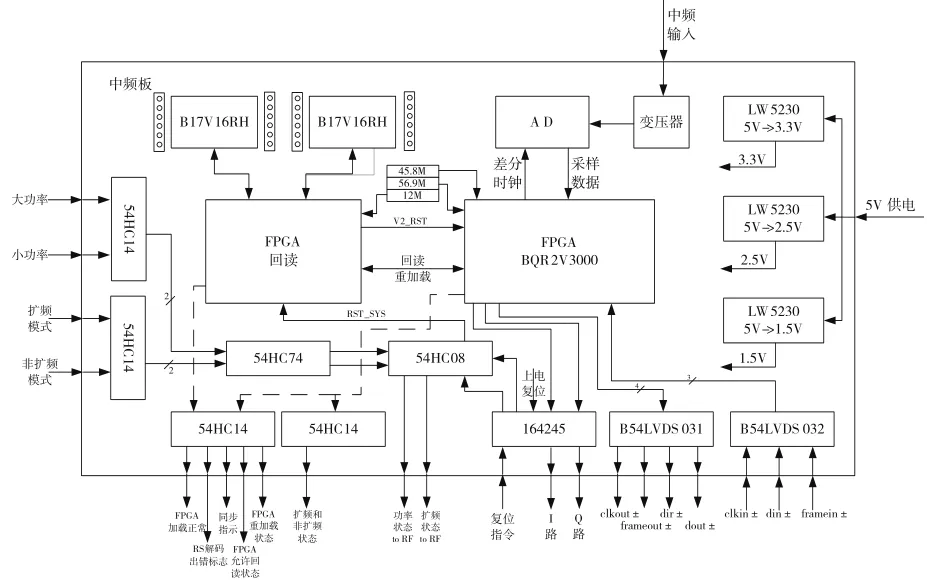

結合宇航產品的可靠性要求,中頻處理模塊盡可能選取成熟且具具備宇航工作經歷的元器件。綜合中頻接收模塊的功能需求,硬件設計主要從二次電源、內部信號處理以及對外接口3方面展開,硬件方案如圖1所示。

圖1 中頻接收模塊硬件方案

1.1 二次電源

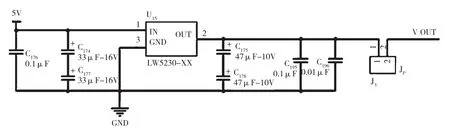

中頻處理模塊使用5 V電壓對模塊進行供電,內部元器件需使用的電壓分別為3.3 V、2.5 V、1.5 V。本模塊選用了國產的3款LW5230系列線性穩壓器,分別設計了電壓轉換電路以得到所需要的輸出電壓。LW5230系列穩壓器輸出電壓變化≤±0.1%,線性調整率≤±0.1%,負載調整率≤±1%,輸出電壓精度高,且具備過壓、過流、輸出短路等保護功能。一款LW5230系列器件的電壓轉換電路如圖2所示,并在電路中設置輸出電壓測試點,可利用萬用表對轉換后的電壓進行測量,滿足設計預期后再對后端電路進行加電,保證后端電路及器件的安全性。

圖2 電壓轉換電路

1.2 內部信號處理

根據實際資源使用需要,中頻接收模塊中使用了1片FPGA芯片,BQR2V3000作為主芯片,是等效系統門數為300萬門的SRAM型FPGA,在中頻接收模塊中的作用是完成中頻信號解擴、解調和基帶信號的編碼組幀輸出。電源需求為3.3 V和1.5 V,加載方式為slave SelectMap,上電時所有引腳配置為高電平。FPGA把組幀、編碼和擴頻之后的數據分成I路和Q路,送至I路接口和Q路接口。

空空通信機有擴頻與非擴頻兩種數據傳輸模式,信號處理硬件配置如圖3所示[4]。中頻接收模塊采用兩片PROM存儲芯片(17V16),用于存儲兩種傳輸模式下的軟件程序,程序之間的切換由外部遙控指令控制,反絨絲FPGA根據遙控指令讀取PROM存儲芯片中的軟件,并加載到主芯片中[5]。

圖3 信號處理硬件框圖

1.3 對外接口

中頻接收模塊輸入輸出采用差分信號,需完成4組差分信號輸出、3組差分信號輸入,因此選用了B54系列B54LVDS031、B54LVDS32兩片國產LVDS芯片。這一系列芯片可支持處理400 Mb/s(200 MHz)頻率的信號,采用低功耗的CMOS工藝,340 mV標準差分輸入/輸出電壓,最大4 ns的數據傳輸延時[6]。

2 抗輻射和力學加固設計

2.1 抗輻射設計

中頻接收模塊中使用的FPGA主芯片是SRAM型FPGA,易受空間單粒子影響而產生單粒子翻轉。FPGA主芯片本身抗電離總劑量能力為100 krad(Si),以中頻接收模塊為壁厚3 mm硬鋁等效屏蔽后軌道輻射總劑量385.0 rad(Si)為基準,可計算輻射設計裕度為258.7,具備高抗輻能力。在設計時選用PROM來存儲程序,不存在單粒子翻轉風險,所以當FPGA內部程序區數據被打翻時,芯片中程序可以通過重新加載得到恢復[7]。此外,中頻接收模塊利用反熔絲FPGA完成對FPGA主芯片進行實時程序回讀比對以及重加載等功能,在設備開機即為回讀允許狀態,如果發生單粒子翻轉進而造成功能中斷,則對程序進行重載,并不斷重復這個流程,以抗單粒子翻轉[8]。

二次電源設計中使用了LW5230系列器件,對外接口使用了B54系列國產LVDS芯片,以中頻接收模塊為壁厚3 mm硬鋁等效屏蔽后軌道輻射總劑量為385.0 rad(Si)為基準,可計算輻射設計裕度(RDM)分別為129.5、776.7,均具備高抗輻能力。

2.2 力學加固設計

FPGA主芯片BQR2V3000是中頻接收模塊的關鍵器件,底部是高鉛含量的焊柱陣列,中部為陶瓷基板,集成芯片置于基板頂部。在防護不足情況下進行大量級的力學試驗,可能會產生晃絲現象,從而造成不可逆的損壞甚至功能喪失。

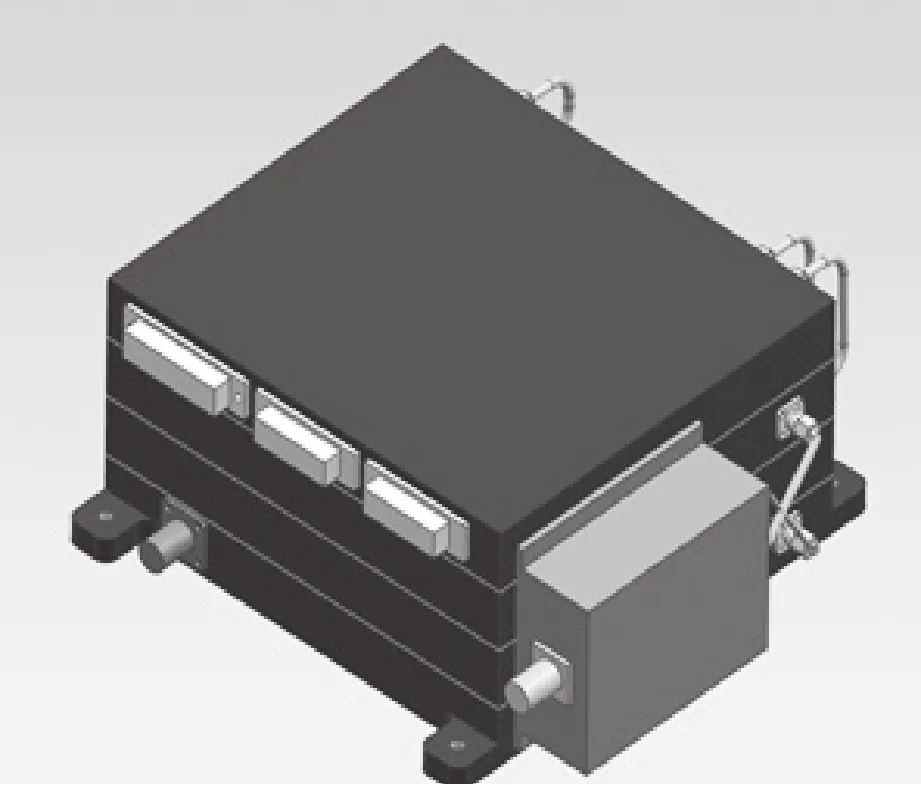

空空通信機采用了模塊式設計,結構上采用層疊安裝,其中中頻接收模塊位于空空通信機最頂層,最底面為安裝面,整機結構示意如圖4所示。力學試驗過程中,位于頂層的中頻接收模塊受到的力學響應最大[9]。

圖4 整機結構示意

在FPGA主芯片BQR2V3000實物的四周增加了力學加固工裝,并在工裝與器件實物四角銜接處加注環氧膠防松,如圖5所示。

圖5 FPGA四周擋塊示意

在FPGA主芯片BQR2V3000增加力學加固工裝后進行力學試驗,經過驗證,中頻接收模塊可以承受隨機振動總均方根加速度為9.68 grms、正弦振動為12 g、沖擊試驗為1 500 g量級的試驗條件[10]。

3 結 論

本文介紹了基于國產化器件的中頻接收模塊硬件方案,介紹了模塊二次電源、內部信號處理、對外接口3個方面的元器件選型方案,從器件抗輻能力及增加的力學加固措施進行闡述,具體指出國產器件對于中頻接收模塊的適用性及力學加固工裝的作用,對后續實現空空通信機中頻接收模塊國產化及工程使用具有實際意義。