高性能FPGA核電壓的數字電源設計

陸 駿,唐 勇,王 朋

(中國電子科技集團公司第58研究所,江蘇 無錫 214072)

0 引 言

隨著科學技術的發展,得益于更高制程能力下,從百萬門、千萬門,到當代數億門的高性能FPGA處理器廣泛應用于通信、醫療、航天、航空等領域。從28 nm、20 nm、16 nm到7 nm,內部集成的門電路也急劇增多,對應需求配套的核電壓也越來越低,電流越來越大,同時需要滿足2%的輸出電壓精度,在大電流的負載高速突變下也要保證輸出電壓的穩定性[1]。數字電源具有的高控制精度和電源管理的優勢,能很好地應用于高性能FPGA供電設計。

1 高性能FPGA的性能指標要求

XILINX和Intel公司的高性能FPGA占據了全球90%的市場份額,其中XILINX的產品系列最為豐富,應用較為廣泛。圖1展示了XILINX公司系列產品的制程發展。目前已量產的最先進7 nm制程下產品需要的核電壓低至0.72 V,供電電流高達150 A甚至更高。且FPGA的工作特點是大電流的負載瞬變特性下要求的輸出電壓交流值變化量在5%以內。這對核電壓電源設計充滿了挑戰。

圖1 賽靈思系列產品

2 數字電源方案設計

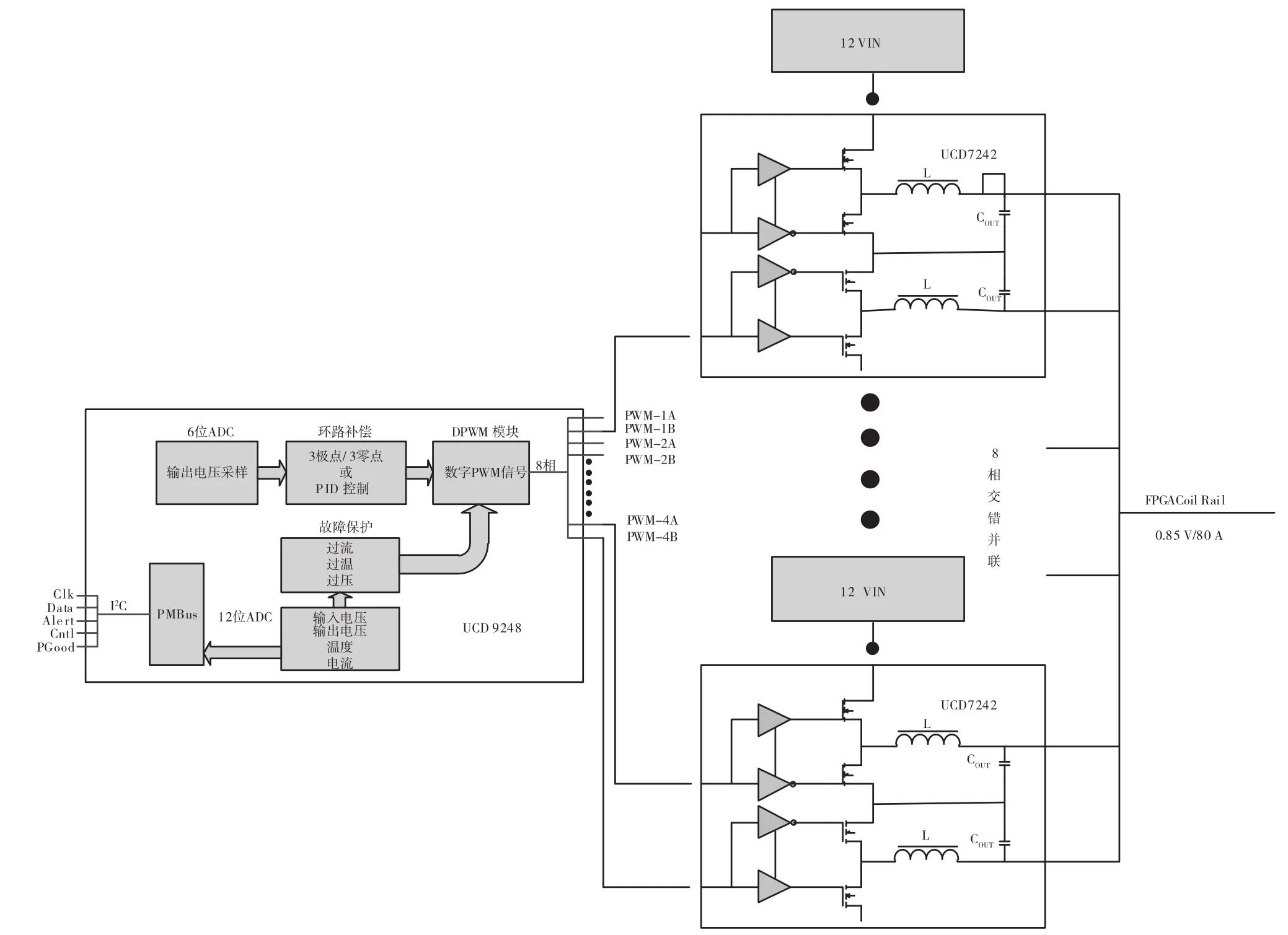

本文介紹的數字電源方案包含主控電路和驅動電路兩部分。主控電路采用德州儀器的UCD9248,最大支持4個電源軌8相并聯工作,UCD9248內部具有一個基于I2C通信協議的PMBus(電源管理總線)可以將電源輸入電壓、輸入電流、各相輸出狀態、溫度信息等上傳主機系統并獲得管理。數字環路控制支持3極點、3零點或數字PID控制,且最小1 mV的閉環控制精度,非常契合高性能大型FPGA的供電需求。驅動電路采用UCD7242,該驅動電路內部集成MOSFET,單通道最大輸出10 A,尺寸小,功率密度高。通過8相交錯并聯,可以實現最大80 A的輸出,設計滿足表1的應用需求,設計方案框圖如圖2所示。

圖2 電源方案框圖

表1 應用需求表

2.1 電感量設計

開關頻率的取值與電感量的設計緊密相關,開關頻率一般設計在100 kHz~2 MHz,通常較小的開關頻率可以減少電源的開關損耗、電感的磁損和鐵損,但需要的電感量和磁芯尺寸都將增大,較低的帶寬也不利于瞬態響應。相反,較高的頻率能提供良好的瞬態響應,較小的電感尺寸,但會增加開關損耗。平衡整體性能,選擇開關頻率fsw為500 kHz。單相輸出紋波電流ΔI目標值為單相輸出電流的35%,選取常用電感量330 nH。對應ΔI為4.787 A。占空比D與輸入電壓UIN以及輸出電壓UOUT之間的關系為:

每相的電感量為:

2.2 輸入電容和輸出電容設計

與單相輸出電源相比,更多的相位交錯并聯能降低流經去耦電容的有效輸入電流,從而降低輸入電壓上的直流紋波。由于實際電容存在等效串聯電阻,電容內部發熱的效應也可以減小,多相并聯輸出的設計能減少輸入輸出電容[2]。

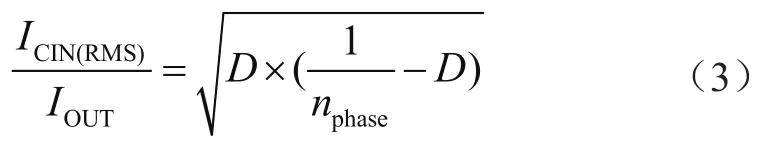

每相上的輸入有效電流與相位數和占空比的關系為:

從式(3)和圖3比較出,8相并聯的有效輸入電流約為單相的25%,4相的55%。根據每相輸入電容電流,計算出需要的輸入電容值為:

圖3 輸入電流有效值與占空比和相位數的關系

圖3考慮陶瓷電容的溫度和電壓降額,每相采用兩個輸入為22 μF的陶瓷電容并聯。

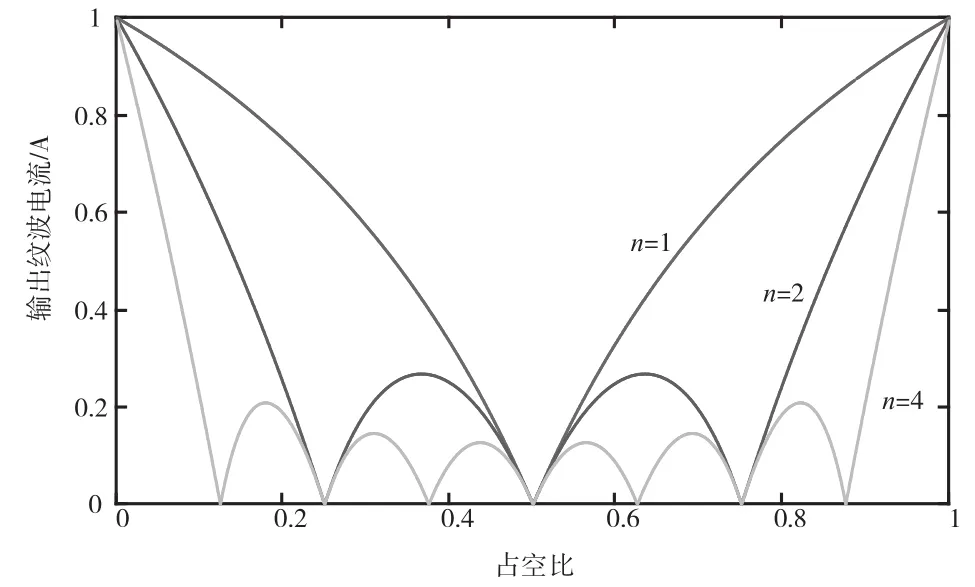

單相輸出電源在上管開通、下管關斷時,負載電流需要從輸出電容提供,在上管關閉、下管開通時,電感給輸出電容續流,整個過程產生了三角形的紋波電流和紋波電壓。使用多相錯位并聯的電源,上管開通、下管關斷時,可以由其他相的電感給輸出電容續流,從而降低輸出紋波電流和電壓[3]。多相輸出的紋波電流IOUT_Ripple_Multiphase和單相輸出的紋波電流IOUT_Ripple_Singlephase與相位數和占空比的關系如圖4所示。

圖4 輸出紋波電流與占空比和相位數的關系

式中,nphase為相位數;m等于floor(nphase·D)。

輸出電壓直流紋波要求為輸出電壓的±1%,需要的輸出電容值為:

需要至少兩顆47 μF的電容才能滿足輸出電壓直流紋波要求。但是該電容通常不能夠滿足輸出負載動態變化時輸出電壓的交流變化量(ΔUOUT(AC))。尤其是像現代FPGA這種要求內核供電電流大、變化速度快的負載特性,供電電源的輸出電容往往需要進一步計算。

在負載突然上升時,輸出電容優先供電流給負載,需要增大電感電流,電感給電容充能增大,輸出電壓出現下沖。在負載突然下降時,需要減小電感電流,在電感電流調節過程中,電感給輸出電容的充電量過多,導致輸出電壓出現過沖,如圖5所示。

圖5 負載動態變化輸出電壓波形圖

由于設計的電源是8相并聯,因此等效的輸出電感LEQ為:

下沖時間為:

下沖時間輸出端需要的電量為:

上沖時間為:

上沖時間輸出端增加的電量為:

滿足下沖電壓跌落需要的電容為:

滿足過沖電壓需要的電容為:

計算滿足負載動態變化的輸出電容為11 411 μF,每相用330 μF的電容5個。

2.3 環路補償設計

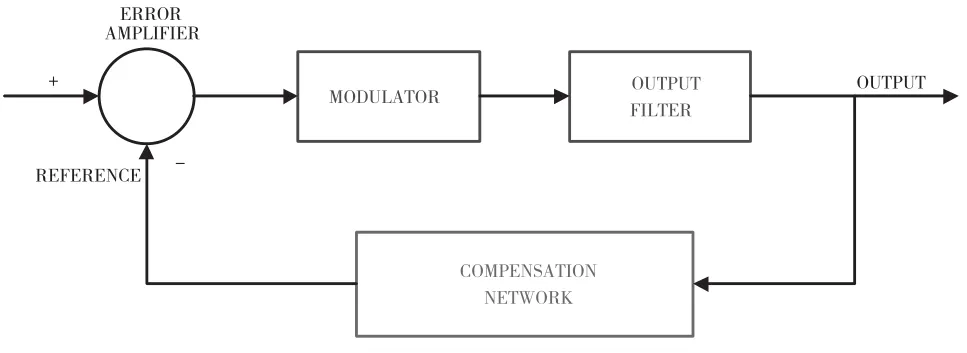

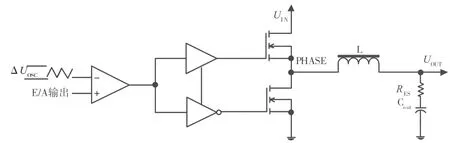

電壓型控制的同步降壓電路由調制器和輸出LC濾波器組成的開環系統,加上環路補償網絡組成穩定輸出的閉環系統如圖6所示。

圖6 同步降壓電路的閉環系統框圖

誤差電壓輸出與振蕩器比較產生PWM信號驅動電路的上下管,振蕩器波形是一個與開關頻率相同峰峰值電壓為1 V的鋸齒波。調制器的增益由輸入電壓UIN與振蕩器的峰峰電壓ΔUOSC確定,計算公式為:

如圖7所示的降壓電路的開換系統,輸出濾波器包含電感,所有輸出電容和電容的寄生電阻RES,輸出的LC濾波器是一個二階帶阻尼的系統,相關計算為:

圖7 電壓型控制的同步降壓電路的開環系統

電壓型降壓電路的開環傳遞函數為:

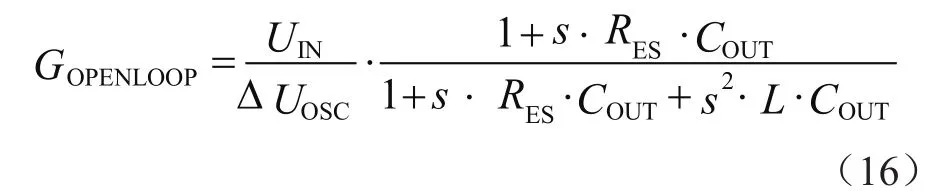

利用Mathcad數學軟件制作波特圖如圖8所示,在LC諧振頻率上存在一個雙極點,RES產生的一個零點。FLC與FESR頻率之間,幅值增益在雙極點作用下以40 dB每十倍頻速度減小,而且有一個非常高的峰值點,相位也在該位置發生陡峭的180°的變化。在FESR處ESR零點的作用下,幅值增益以20 dB每十倍頻速度減小,相位提升了90°[4]。

圖8 開環系統傳遞函數波特圖

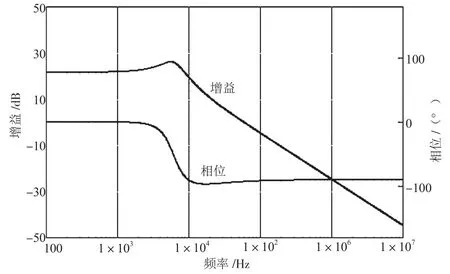

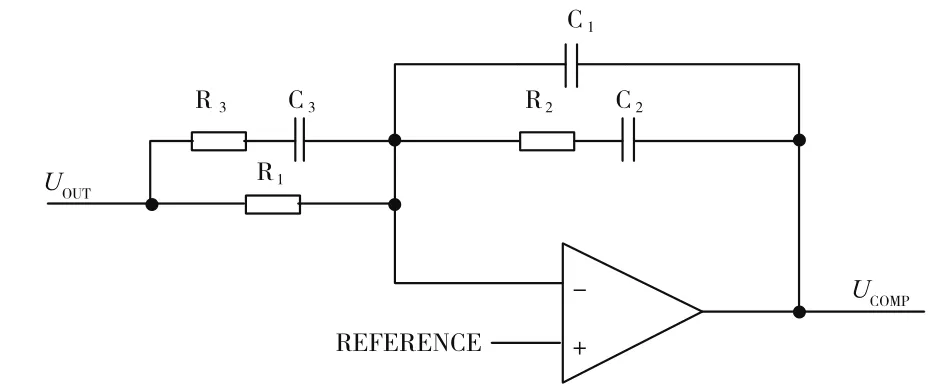

為使系統穩定,在雙極點位置需要額外增加零點來提升相位,保證閉環系統的穩定性。一般而言,通過環路補償的降壓電路理想的波特圖是幅值下降速度20 dB每十倍頻,幅值裕量20 dB,相位裕量大于45°,帶寬是開關頻率的20%~30%。在模擬電路設計中,通常采用TypeⅢ型電路進行補償,示意如圖9所示。

圖9 TypeⅢ型電路示意

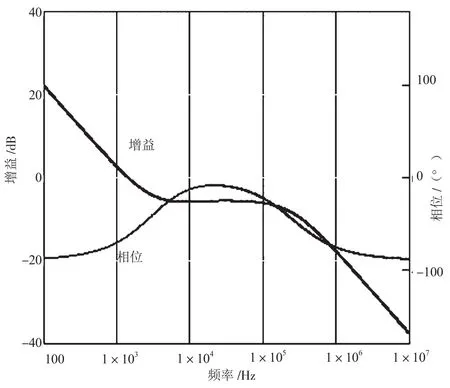

TypeⅢ電路可以提供兩個零點,3個極點補償。兩個零點可以提供180°的相位提升,將兩個零點合理地設置在輸出LC諧振頻率附近,可以抵消雙極點的影響。TypeⅢ電路的傳遞函數如式(17)所示,對應波特圖如圖10所示。

圖10 TypeⅢ型電路波特圖

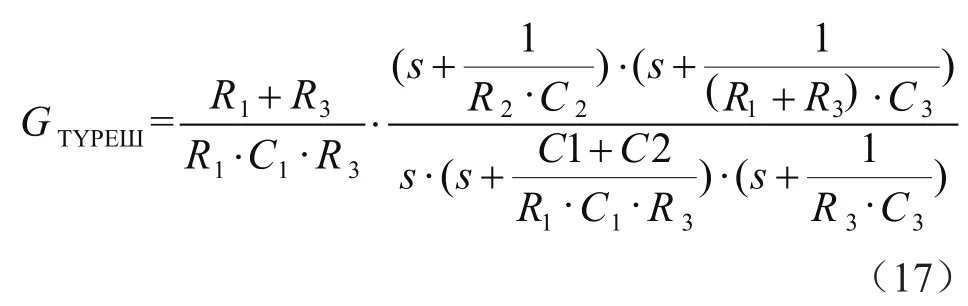

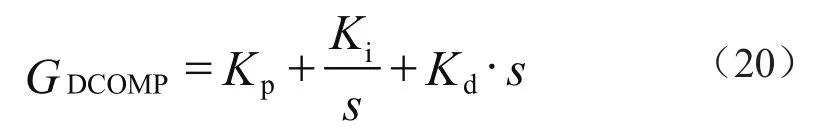

閉環系統的傳遞函數為:

通過環路補償后的閉環降壓電路系統,能夠穩定地產生固定輸出電壓。根據閉環系統的傳遞函數公式(18)可以得出系統的穿越頻率、相位增益和幅值增益如圖11,圖12所示。一般而言,穿越頻率越大,系統的響應速度越快,但由于香農采樣定理,穿越頻率必須小于開關頻率的一半,否則輸出將會有很大的開關紋波,工程上通常取穿越頻率為開關頻率的1/10到1/5[5,6]。理想條件下,通過補償電路零極點的設計,需要將系統的相位裕量大于45°,相位裕量低于60°時,會增大負載瞬態變化時的電壓過沖[7]。

圖11 閉環系統增益圖

圖12 閉環系統相位圖

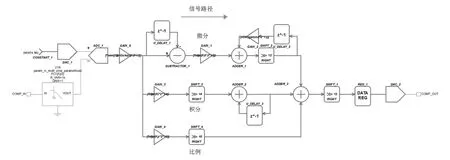

采用數字控制的UCD9248通過多個功能模塊產生PWM信號,由于數字控制信號時鐘高達4 GHz,分頻到每相的斜坡比較器時的時鐘信號最大有250 MHz,遠遠大于幾百千赫茲開關工作頻率,因此可以認為誤差放大器的輸出信號是連續的電壓值。數字可調放大器可以設置1倍到8倍的增益。誤差信號通過9位A/D轉換,為防止高頻噪音干擾,需要經過一個低頻增益64的數字濾波器(Anti-Saturation)。整個數字閉環控制系統框圖如圖13所示。

圖13 數字控制同步降壓電路的閉環系統框圖

以上模塊組成了數字PWM信號(DPWM)的固定增益,即:

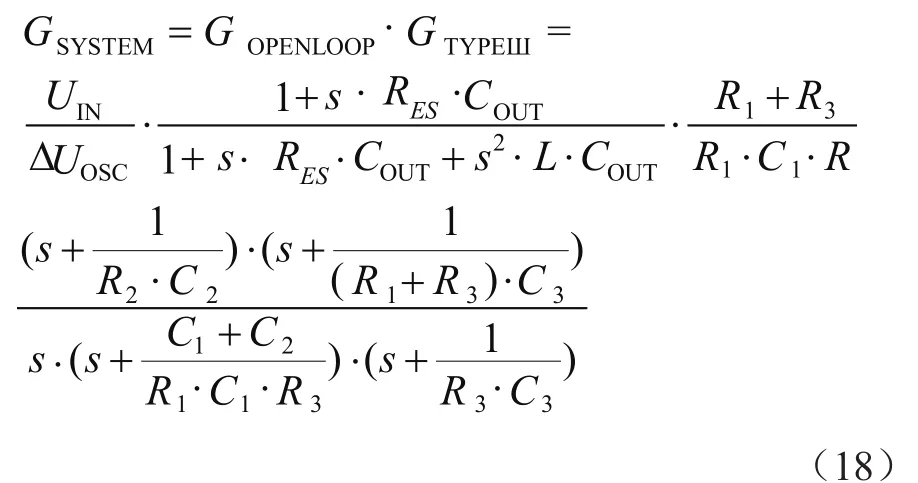

類似模擬電路的環路補償傳遞函數,數字控制部分的環路補償傳遞函數為:

對數字PID控制進行離散化對比,可得模擬PID控制器參數離散化公式為:

式中,T為最小采樣時間;Kp為比例控制參數;Ki為積分控制參數;Kd為微分控制參數。

數字電路的系統傳遞函數為:

數字電路的環路補償可以模擬3個極點、3個零點,或者模擬PID算法,方便設計系統的環路。

3 數字電源仿真

SIMetrix/SIMPLIS軟件能夠快速地對開關電源進行頻率響應分析,在電源設計中應用廣泛。根據上述的理論分析和芯片參數,建立由UCD9248數字芯片控制的8相BUCK降壓電路[8]。其中,每相降壓電路的功率電路部分和PID控制補償部分仿真原理如圖14和圖15所示。

圖14 功率級單相仿真電路原理圖

圖15 數字PID控制部分仿真原理圖

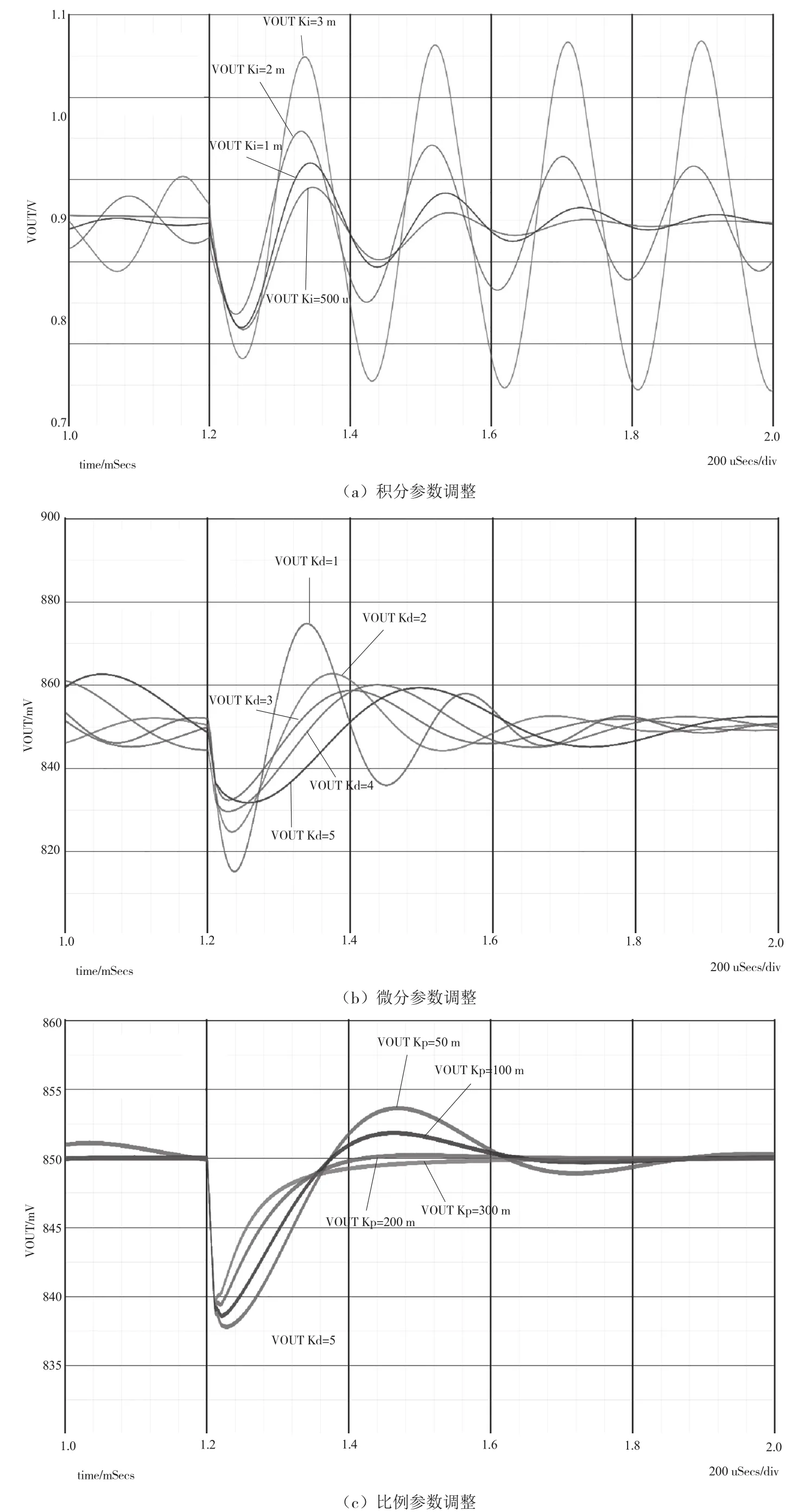

數字PID控制可以采用3個步驟進行調整:

(1)單用積分控制。逐漸增大Ki直到系統收斂。單積分控制輸出電壓可能存在振鈴,需增加微分、比例控制來減小振鈴。當Ki增大到4×10-3時,系統不收斂,如圖16(a)所示。

(2)增加微分控制,逐漸增大Kd,直到Kd值的增加不能減小振鈴振幅。Kd從1增加到4時,振幅逐漸減小。繼續增大Kd時,振幅不變。如圖16(b)所示。

圖16 數字PID控制

(3)通過調整Kp進一步減小振鈴。Kp從5×10-2增大到0.3時,系統由過阻尼變為欠阻尼,當Kp=0.2時,系統接近臨界阻尼狀態。

最后調試采用的參數如表2所示。

表2 調試參數

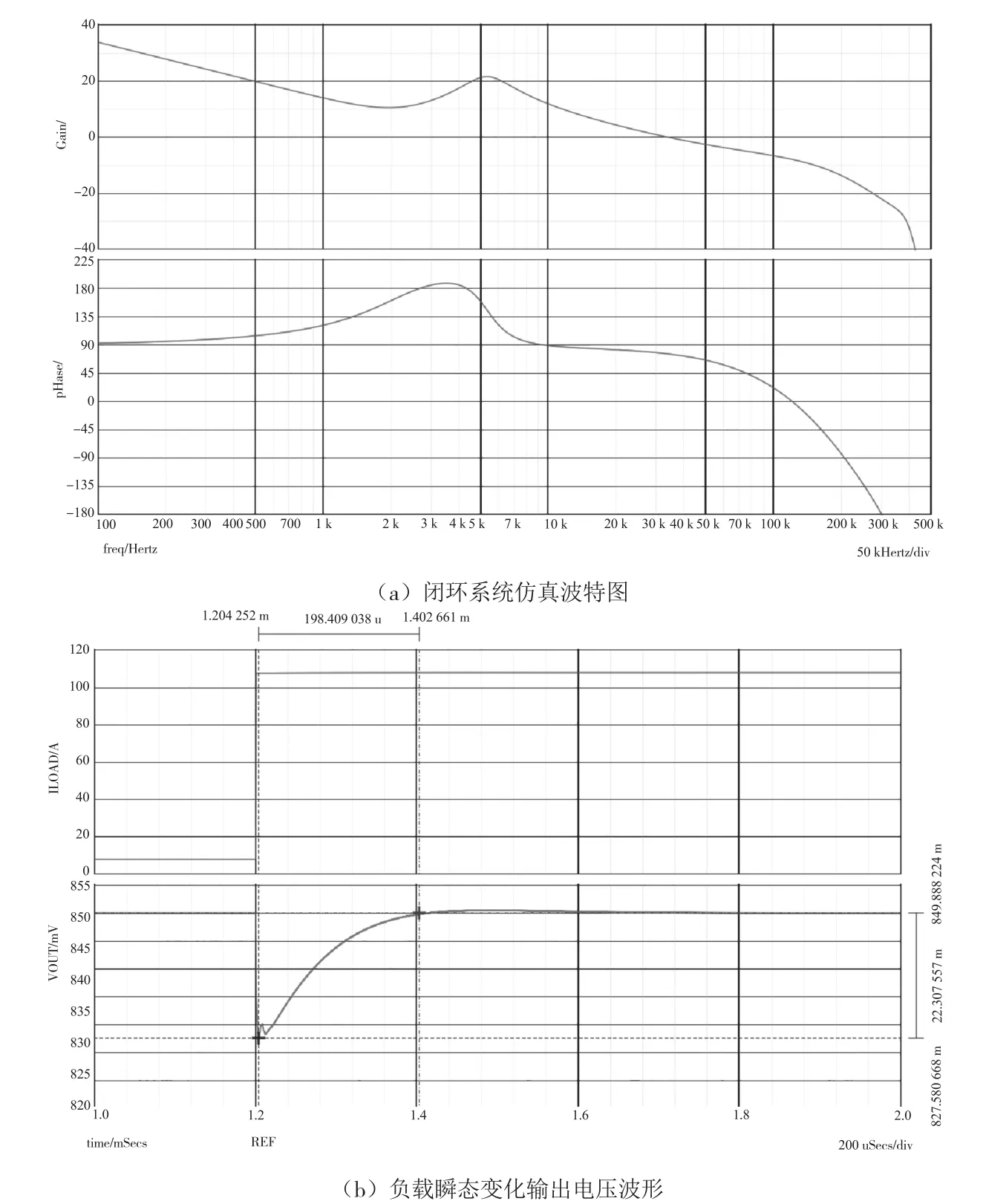

仿真結果,穿越頻率37 kHz,相位裕量78°。仿真輸出負載從100 A/μs速度從10 A增大到100 A,電壓跌落了22 mV,如圖17所示。

圖17 仿真結果

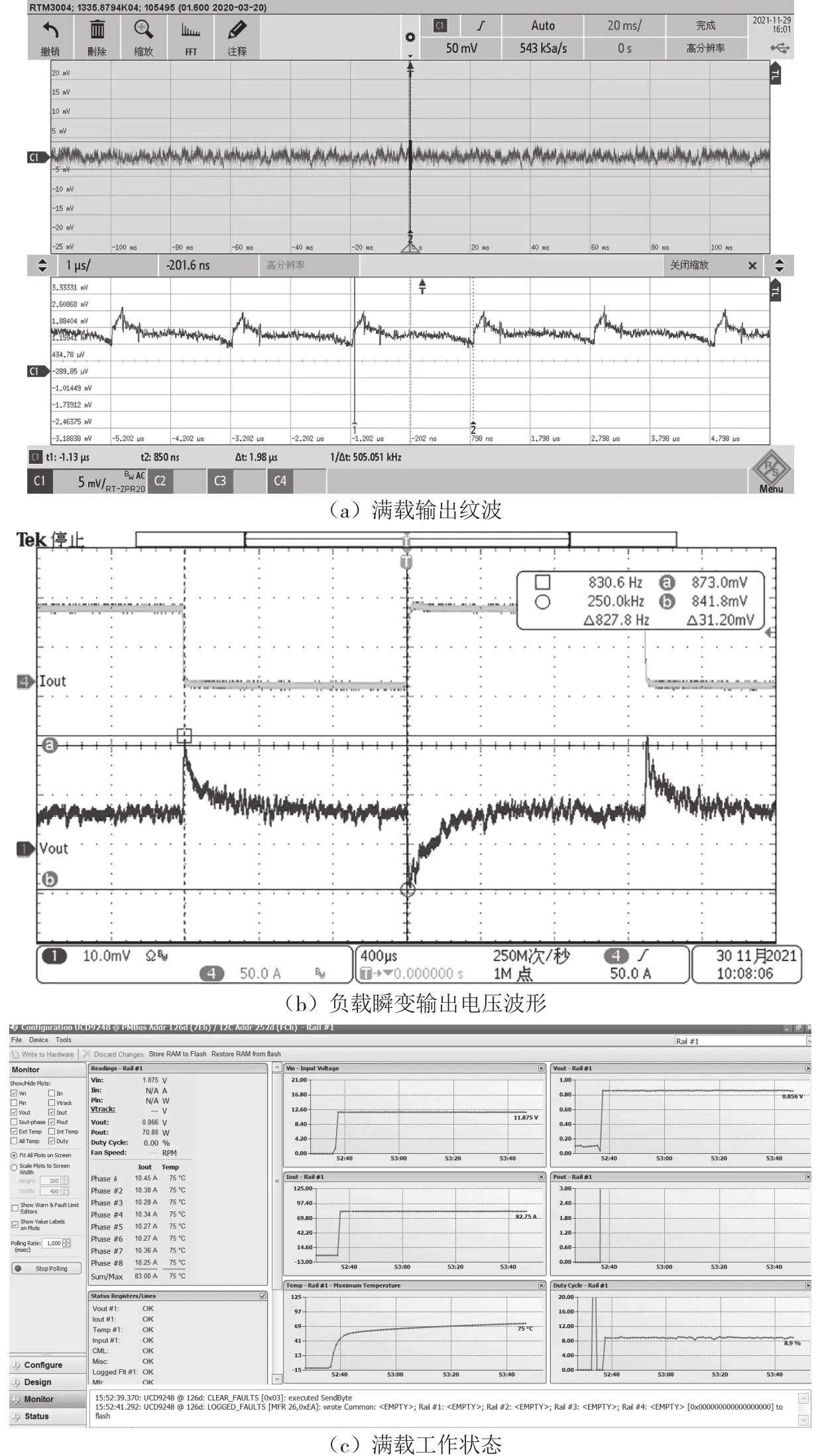

4 實驗結果

根據上述設計,制作了基于UCD9248數字控制的8相交錯并聯降壓電路驗證板,并進行了測試,性能滿足表1要求。在滿載80 A輸出電壓下,輸出電壓紋波10 mV,如圖18(a)所示。測試負載從10 A到80 A以100 A/μs變化時,輸出電壓峰值為31.2 mV,如圖18(b)所示。通過UCD9248的PMBus電源管理總線系統,可以監測電源每相的輸出電流、溫度、輸出功率、輸出電壓等信息,如圖18(c)所示。

圖18 實驗結果

5 結 論

本文提出的應用于高性能FPGA核電壓的數字電源設計,基于UCD9248設計了8相交錯并聯,數字PID控制,實現了輸出電壓在穩態和瞬態負載電流條件下,都有非常高的精度,并能與主機系統實現PMBus通信,仿真和實驗結果表明設計的數字電源能夠滿足高性能FPGA核電壓的供電要求。