漫談蘋果M1全系列:半導體新時代!

林亦

在2022年的春季發布會上,蘋果公司發布了M1系列芯片的新成員——M1 Ultra。一直講究命名獨創性的蘋果,這回跟三星的Ultra手機&平板系列撞了個結結實實。當然三星也沒錯過這個機會,不到一個小時就發了條推特說自己贏了,現在全世界都知道三星的運營部門上班時間看蘋果發布會了。

說完這個小插曲咱們回到正題,M1 Ultra是一張意義深遠的芯片,對蘋果乃至整個半導體產業,都是如此。雖然大部分人用不上這張芯片,但這不影響我們對它臺前幕后的故事感興趣。

對蘋果來說,這標志著第一代M系列芯片全部發布完畢。這一點在發布會上,得到了蘋果負責硬件工程的高級副總裁John Ternus的確認。作為最后也是最強大的一張M1,M1 Ultra走在了半導體產業先進封裝這個新方向的前列。對整個半導體產業來說,這也是一張有里程碑意義的芯片,率先為我們勾勒出了摩爾定律2.0時代的輪廓。

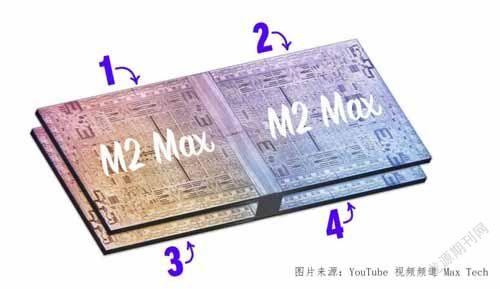

關于半導體新時代,我們先從M1 Ultra芯片談起。這張芯片的特點是由兩塊M1 Max縫合出來的,M1 Ultra最大能達到20個CPU核心、64個GPU核心,128GB統一內存。對比M1 Max的參數剛好翻倍。

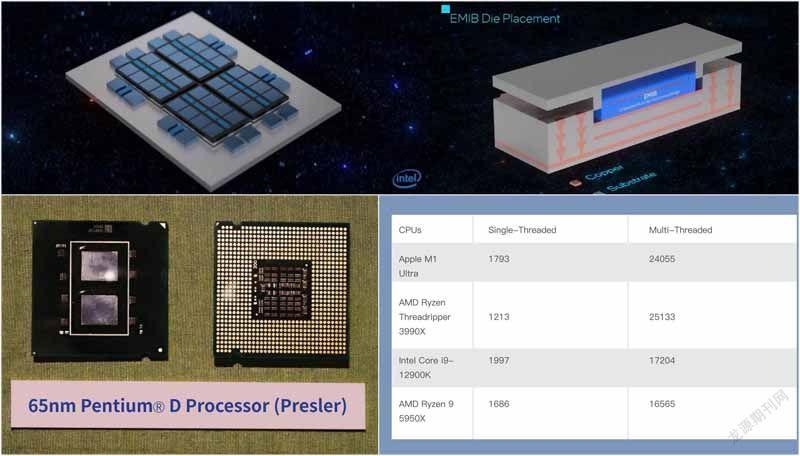

芯片縫合參數翻倍這種事,以前也有,比如05、06年英特爾的奔騰D處理器,然而實際效果欠佳——雖然兩晶片被縫合在一起,但兩者卻不能通信。大家小時候應該都經歷過這種情況,就是跟好朋友鬧翻了,誰也不跟誰講話,所有事呢,都得靠一個共同的朋友來傳話。當年奔騰D的兩個晶片就是同樣的情況,所以雖然參數翻倍了,但性能提升主要還是靠用戶對自己進行心理暗示,我稱之為“精神超頻”。因此這種方案不僅沒有發展成主流,反而衍生出了“膠水雙核”這么個梗,專指這類騙自己的多晶片方案。所以今天常見的多核處理器、都是把CPU核心刻在同一塊晶片上,保證核心與核心之間的高速通信。

不過這次兩塊M1 Max縫合出來的M1 Ultra又有了新變化,關鍵就是UltraFusion。UItraFusion的通信速度達到了2.5TB/s,而且這個TB的B是大寫的、不是小寫的。筆者十多年間收集的影視資源也就區區4個T,UltraFusion不到兩秒就能給傳完,這個速度是PCIe4.0 x16插槽的78倍、入門級M1統一內存的36倍。M1 Max的內存通信速度達到了400 GB/s,不到UltraFusion的1/6。實際上M1 Ultra自己的內存通信速度是800 GB/s,也不到UltraFusion的1/3。

這是一個值得討論的話題。首先M1 Ultra內存800 GB/s這個數,是很說明問題的。MI Ultra里面有兩個M1 Max,每個M1 Max的內存帶寬是400 GB/s,假如上半部分一個CPU核心同時訪問所有內存,它享受的帶寬就應該是上面這塊M1 Max的帶寬、加上下半部分的內存被UltraFusion卡了一下之后剩下來的帶寬。現在這個800 GB/s剛好是上下兩部分加起來,400加400,所以這就側面反映出UltraFusion的帶寬確實是給夠了,至少沒耽誤內存。

有國外博主提出另一種看法,他認為根據這個數字來說,應該還會有一款兩塊M1 Ultra兩層疊起來的設計,總共四塊M1 Max縫合到一起,原因就是UltraFusion這個2.5 TB/s的帶寬是M1 Ultra內存800GB/s的三倍多,給兩個M1 Ultra用也是足夠的。

對此,筆者持懷疑態度。按蘋果在發布會上的描述,M1 Ultra在軟件實際調用的時候會被識別為一塊單一芯片,不需要程序員額外注明任務怎么分配,兩塊M1 Max自己就能協調好,對外表現是一整塊20核的處理器,而不是兩塊10核處理器。實際跑分結果也印證了蘋果的這個說法。M1 Max的Geekbench多核跑分是1.2萬,M1 Ultra是2.4萬,實際性能上確實是翻倍效果。想要把融合效果做到這種程度,兩張M1 Max之間的信號傳輸就不能只限于內存了。CPU、GPU、緩存,還有神經引擎、媒體引擎這些元件之間應該都要有信號傳輸,到極限情況M1 Ultra一起工作,2.5 TB/s可能也只是剛好夠用而已,所以我對這套通過帶寬反推新芯片結構的邏輯表示懷疑,但大家可以對四塊M1 Max縫合這個事留個印象。

言歸正傳,回到M1 UItra本身。上文我們提到M1 UItra里兩塊M1 Max,可謂珠聯壁合,宛若一體。再回看更早英特爾奔騰D的“膠水雙核”,理念還是一個理念,但實際效果是天壤之別。從目前的Geekbench跑分來看,M1 Ultra超過了Mac Pro中英特爾的28核至強處理器,甚至接近了AMD 64核的線程撕裂者3990X,同時功耗卻比這兩者低得多。那為什么同樣的理念,今天的效果卻突飛猛進?答案就是半導體產業這些年的一個新動向:先進封裝。

什么是封裝呢?半導體工藝流程分前段制程和后段制程。顧名思義,前段就是前面在晶圓上刻晶片、做電路的這些步驟,后段就是后面的步驟,封裝就屬于后段制程。這一步簡單點講,就是把前段制程里切下來的小晶片裝到電路板上,扣上蓋子,做成咱們日常能買到的比如英特爾i5、i7這些CPU。

這幾年封裝技術進步特別快,舉個側面的例子,就是“CPU”這個名詞都開始有歧義了,像以前我們說CPU指的就是這一整塊芯片,但是現在隨著封裝技術的進步,芯片這個蓋子里集成的功能越來越多,CPU反而只是其中的一塊了。尤其是像M1 Ultra,你說CPU具體指M1 Max里的CPU區域,是M1 Max,還是整個M1 Ultra呢?

這就是人類語言追不上技術的一個典型例子,也側面反映了先進封裝技術對半導體產業的顛覆性。先進封裝,就是把今天復雜、大型的晶片封成一塊芯片的技術,也是半導體產業的一條新賽道。長期以來,半導體產業的主要精力都在前段制程上,通過縮小晶片上的晶體管尺寸來提高晶片性能,但晶體管越小,再往下縮面臨的物理限制就越多,難度可以說是指數級上升。當年英特爾就是因為低估了問題的難度,高估了自己的能力,在加號地獄里無限輪回,最終導致了蘋果的跑路,如今換了一個技術出身的CEO才終于又有了起色。不過從整個半導體產業來看,晶體管尺寸的物理限制是所有人都要面對的難題。無論英特爾、臺積電還是三星,近年的制程升級節奏都在變慢。所以前段卡住,發力后段做先進封裝,就成了行業的共識。除了今天的這張M1 Ultra,英特爾也在做EMIB和Foveros 3D封裝,而AMD的3D封裝芯片、R7 5800X3D將在4月20日面世。

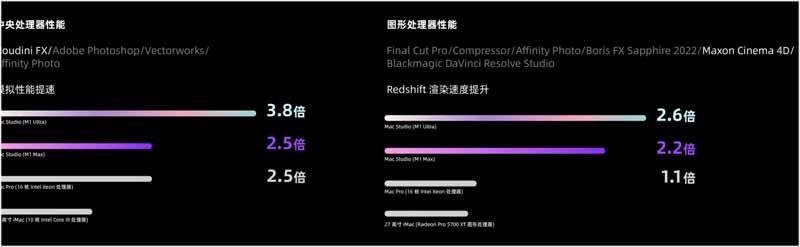

M1 Ultra芯片由兩塊M1 Max強強合體,給你磅礴動力,處理各種龐大艱巨的工作。運行復雜的粒子模擬,或是執行過去難以實現的大型三維場景渲染,現在都得心應手。M1 Ultra的媒體處理引擎資源也同樣翻倍,可支持同時播放多達18條8K ProRes 422視頻流,這在個人電腦上是極具顛覆性的。

其實摩爾定律本來就是說每18個月芯片上的晶體管數目翻一番,就沒提過晶體管尺寸。今天的晶片已經很小很小了,借助先進封裝技術擴大芯片面積,從而增加晶體管數目,同樣可以維持摩爾定律,支撐半導體產業的發展,因為不同于長期以來縮小晶體管尺寸的思路,所以封裝產業將這個新方向稱作是摩爾定律的2.0階段,今天的M1UItra,包括即將開賣的AMD 5800X3D,都在證明這個方向的可行性,而這兩款產品的制造企業其實是同一家,就是臺積電,包括摩爾定律2.0這個概念,也是臺積電的工程人員提出來的。

講先進封裝,一定繞不開臺積電。臺積電在先進封裝技術上是起步最早的企業之一,這背后也有段故事。

2011年,重新執掌臺積電剛剛兩年的張忠謀,宣布要做先進封裝。2011年的時候英特爾還在32納米制程上,那時提到先進封裝大家想到的也是拉胯的膠水雙核,所以老先生的這句話很多人想不通。封測大廠日月光的財務長董宏思就評價說“這種技術只會被用在極少數的特定高端產品中,影響有限”。當時在臺積電負責先進封裝研發的人,是今天的臺積電副總經理余振華,他就回擊說“先進封裝這個技術,以后所有高階產品都會用,市場很大”,說自此專注于先進封裝的研發。

到了2013年,FPGA廠商賽靈思成為了臺積電先進封裝技術的第一個客戶。一年之后,英特爾正式進入14納米制程,開啟了一場以加號為主題的奇妙旅程,制程困局的倒計時,正式開始。今天回頭來看,張忠謀可謂慧眼如炬。再看看蘋果的M1 Ultra、AMD的5800X3D,余振華當年的話也在逐漸成為現實。

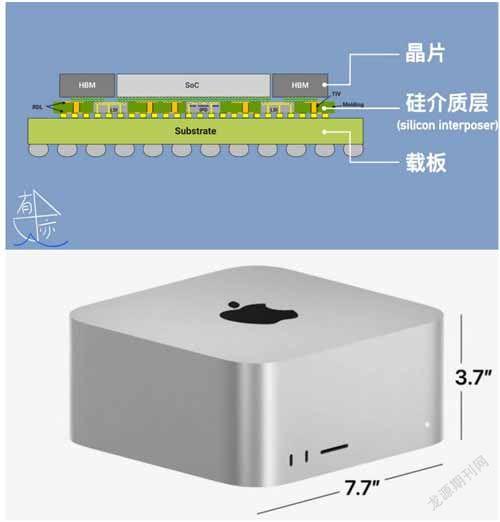

話說回來,臺積電的先進封裝在M1 Ultra的制造上,到底干了啥?根據當年電子時報的報道,UltraFusion使用的大概率是臺積電的CoWoS-S技術,也有可能是成本更低的InFO-LSI、類似英特爾的EMIB。這里我們以CoWoS為例解釋一下,這幾個技術主要區別是材料的用量不一樣,相應地成本也不一樣,但原理相通。CoWoS的全名是chip 0n Wafer on Substrate,名字很直白,描述的就是這么個三層結構,Chip是晶片,在最上面,Wafer指的是硅介質層,夾在中間,英文叫Silicon Interposer。蘋果發布會上Johny Srouji講UltraFusion的時候,左一個interposer、右一個inte rposer,說的就是夾在中間的這個硅介質層。最下面一層就是Substrate——載板,通俗點叫電路板。這三層里面最創新的是中間這層。它的作用是縮體積、降功耗。硅介質層和晶片的材料一樣都是硅,內部電路結構可以比下面的電路板更細、更密,電路寬度可以做到1/10甚至更細。M1 Ultra有大量的功能電路和通信電路,晶片放不下的就可以由中間這個介質層來分擔,但如果沒有介質層,讓電路板來分擔,那體積和功耗都要成倍增加,因為電路板的線太粗了。形象點說,如果沒有這種先進封裝技術,那MI Ultra根本放不進Mac Studi0這個小盒里,如果硬要把這些信號通道刻在電路板上,M1 Ultra的尺寸可能比蘋果的27寸顯示器還大,耗電量可能超過家用空調和冰箱的用電之和。所以這就是臺積電先進封裝的意義,因此M1 Ultra才成為了可能。

那么問題來了,即使是有臺積電的先進封裝,但M1 Ultra上面有1140億個晶體管,為了讓兩塊M1Max珠聯璧合,宛若一體,這些晶體管之間又要有無比復雜的通信電路。若干晶體管和電路的故障是大概率事件,就算有冗余設計,像M1 UItra這么復雜的晶片,良品率也有限。生產成本這么高、再加上新芯片巨大的設計成本,售價必然高不可攀。不過不用擔心,咱們看看蘋果的CEO是誰?Tim Cook,工業工程出身,資源優化大師。1998年3月臨危受命來到蘋果,七個月后把產品庫存量從30天減少到6天,到1999年又進一步減少到驚人的兩天。“庫存克星”這個稱號對庫克是一種羞辱,因為有庫存才需要克星,而庫克的目標是“沒有庫存”。當年庫克在lBM學的就是JIT制造模式,“Just in Time”,需要多少做多少,不留庫存。有這樣一個領導者,你可以相信蘋果能解決M1 Ultra的成本問題。

接下來,咱們就來講一講蘋果的20210217702A1號專利,全名是“晶片連接的系統與方法”,這里面有UltraFusion的結構描述,也有上文提到的成本問題的解決思路,更有下一代大型芯片的預先規劃,我稱之為“蘋果自研芯片全面劇透”專利。

這篇專利公開于2021年7月15日,相比M1 Ultra的發布提前了半年多。芯片投產前就做專利保護是很正常的,但為什么提前這么多?聽我慢慢道來。

首先關于ultraFusion的具體結構方面,專利書第31段、第37段,第42到48段,以及結尾部分的20條專利主張都進行了描述。首先兩塊M1 Max晶片在分界線兩邊各有一條信號緩沖帶,M1 Max上需要通信的元件,比如CPU、GPU、內存都與信號緩沖帶連接,信號從這些元件走到緩沖帶,再經由緩沖帶上的通道穿過分界線,到達對面的緩沖帶,最后到達目標元件。

搞清楚結構,我們就可以講前面的成本問題了。根據專利書上的描述,芯片生產過程中,工廠會先在晶圓上排滿M1Max晶片,然后逐一檢查,把相鄰且內部電路完好的晶片找出來,在這些晶片之間搭建信號通道、填充電介質,連上之后,一對對兒切下來,M1 Ultra就成了。剩下的晶片,如果只是負責跨晶片通信的電路有問題,就單獨切下來,當M1 Max來賣,這就是為什么去年的M1 Max芯片下面,全都額外有一條信號緩沖帶,這個并沒有什么用的結構,我稱之為“庫克的微笑”。這也是為什么蘋果去年七月就要公開專利,因為10月M1 Max就要發布了,生產M1 Max其實就是在生產M1 Ultra,所以要提前保護。不過降成本這條路走到這兒還沒完,M1 Max的結構也挺復雜,萬一也做壞了呢?沒關系,庫克也做了預案。如果生產缺陷是在下半部分,橫著來一刀,它就變M1 Pro了,照樣賣。這些都是很優秀的成本控制設計。這樣一來呢,良品率變高,生產成本和設計成本卻被攤薄了。再進一步,設計成本其實還能往下攤。雖然M1 Pro沒法直接砍成M1,但是像CPU、GPU核心、雷電控制器等,很多元件都可以在M1上原樣復用,每賣出去一張M1,同樣也是在分攤整個M系列芯片的設計成本。如此來看,我們可以理解為M1 Ultra才是整個系列的主角,其余產品都是為了它的誕生而服務。順著這個思路,iPad Pro和iPad Alr為什么上M1芯片,也就終于有答案了。我之前覺得蘋果上M1是想用iPad取代電腦,現在我覺著我判斷錯了,至少是因果關系反了。對蘋果來說,只要iPad散熱壓得住,上M1之后都是好事。性能強、有噱頭、有關注度,還能分攤M系列芯片的設計成本,而且還省了設計iPad芯片的成本,所以對蘋果來說沒什么理由不給iPad上M1。讓iPad取代電腦,最多就是有了上M1這個打算之后的想法,或者干脆就沒有這個想法。照這個思路,未來基礎版iPad、甚至iPad mini,只要散熱壓得住,很可能都會上M系列芯片。再往外推一步呢,蘋果的長期目標,很可能就是把手機、平板和電腦的芯片都統一到同一個芯片產品線上,理論上來說這樣可以最大程度地減少浪費,還能增加生產線運營的靈活性。比如說某段時間iPad Air的銷量遠高于MacBook Air,那就把給MacBook準備的M1芯片,調給iPad Air,這種極致的優化,剛好是今天的蘋果CEO庫克最擅長也最喜歡的事。假如真有那么一天,蘋果就會變成一個運營效率極高的科技工業體,能不能做出改變世界的產品要靠運氣,但每年的財報絕對會非常好看。那時,蘋果就真的是庫克的蘋果了。

這件事到底有沒有可能呢?我們再回到蘋果的專利書。專利書的本質就是通過公開來換取保護,把你想做的和有可能會做的事都寫上去,寫得越全,獲得的專利保護才能越全面。蘋果這篇專利書的第39段(找原文標記)介紹了這套晶片縫合方案的潛力。這套方案并不局限于兩塊晶片,任何數量都可以,比如三塊、四塊。晶片的縫合邊也不必局限于一條,最多可以給四條邊都加上信號緩沖帶,這樣四條邊都可以與其他晶片縫合。這就是明確說了四塊晶片合體是可行的,而且合體方式不是疊放、也不是通過插槽中轉,而是多邊縫合。有了這個信息,首先可以確認M1 Max不可能四塊合體了,因為M1 Max上只有一條信號緩沖帶,如果想四塊晶片合體,按照蘋果專利書里的方案,每塊晶片至少要有兩條緩沖帶,明顯M1 Max就不行了。然后就是剛才說的手機、平板、電腦全線芯片統一,這事的可能性是存在的。今天手機跟電腦芯片的性能差距已經沒那么懸殊了,未來手機用單晶片,平板和輕薄本用雙晶片,專業本和臺式機用四晶片,好像也不是不可以,那就真成摩爾定律2.0了,但是在這種縫合方案的成本降下來之前,這都只是猜想。

今天我們從M1 Ultra的參數談起,先追溯了老一代封裝方案“膠水雙核”的黑歷史,然后就M1 Ultra的實際性能結合半導體產業的現狀,講了封裝技術的“老樹開新花”,那講到了先進封裝,就不能不提臺積電和摩爾定律2.0,以及臺積電先進封裝如何讓M1 Ultra成為了現實。翻閱蘋果的UltraFusion專利書,從M1 Ultra的成本控制出發,梳理了M系列全產品線的關系,展望蘋果未來,我們一起等待時間驗證。