一種基于FPGA 的萬兆以太網控制器

2022-05-12 07:42:36吳震霖

廣東通信技術

2022年4期

關鍵詞:信號

[吳震霖]

1 引言

隨著以太網技術的快速發展,利用以太網承載各種業務的需求也日益增強傳統的千兆以太網已不能滿足網絡對傳輸帶寬的要求[1,2],因此,需要運用更高速率的以太網技術解決傳統以太網帶寬不足的問題。萬兆以太網遵循的標準是IEEE 802.3ae,傳輸速率可達10 Gbit/s,性能相比千兆以太網有了很大的提高[3]。萬兆以太網控制器是協議層與傳輸媒介之間的橋梁,是實現萬兆以太網技術的基礎。

本文介紹了萬兆以太網控制器主要完成的功能以及萬兆以太網數據幀格式,并提出了一種基于FPGA 的萬兆以太網控制器,該控制器包括萬兆以太網MAC 模塊和萬兆以太網PCS/PMA 模塊,進一步說明了該控制器的用戶接口時序要求。最后,將設計的萬兆以太網控制器在硬件平臺上進行測試驗證。

2 萬兆以太網相關協議

2.1 萬兆以太網控制器與OSI 參考模型的關系

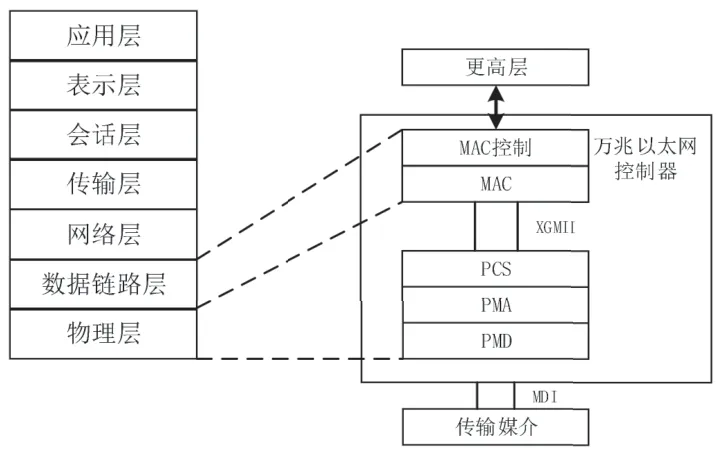

萬兆以太網控制器主要完成了OSI 參考模型中的數據鏈路層和物理層的功能[4],如圖1 所示。

圖1 萬兆以太網控制器實現的功能示意圖

數據鏈路層包括MAC 子層和MAC 控制層子層,MAC 子層負責萬兆以太網數據成幀和數據錯誤判決,MAC 控制層子層負責實時提供流量控制機制。

物理編碼子層(PCS)負責對來自MAC 子層的數據進行64B/66B 編碼和解碼。物理介質附屬子層(PMA)在發送方向負責將并行數據串行化,在接收方向負責串行數據流的時鐘恢復,同時進行數據的串并轉換。物理介質附屬子層(PMD)負責信號的調制、放大、整形。介質相關接口(MDI)定義了不同的物理介質和連接器類型。……

登錄APP查看全文

猜你喜歡

鴨綠江(2021年35期)2021-04-19 12:24:18

考試與評價·高一版(2020年6期)2020-11-02 02:45:24

媽媽寶寶(2019年10期)2019-10-26 02:45:34

中國生殖健康(2019年3期)2019-02-01 06:12:26

鐵道通信信號(2018年11期)2019-01-19 01:15:08

電子制作(2018年11期)2018-08-04 03:25:42

鐵道通信信號(2018年2期)2018-04-18 12:18:10

鐵道通信信號(2016年11期)2016-06-01 12:11:32

鑿巖機械氣動工具(2016年3期)2016-03-01 04:00:25

中國病理生理雜志(2015年8期)2015-12-21 12:38:06