sCMOS 相機(jī)系統(tǒng)設(shè)計(jì)

王伶杰,楊世洪

(1.中國(guó)科學(xué)院光電技術(shù)研究所,四川成都 610209;2.中國(guó)科學(xué)院大學(xué),北京 100049;3.中國(guó)科學(xué)院 空間光電精密測(cè)量技術(shù)重點(diǎn)實(shí)驗(yàn)室,四川成都 610209)

相較于普通場(chǎng)合使用的相機(jī),科學(xué)相機(jī)往往面臨更加惡劣的工作環(huán)境,并且承擔(dān)著重要的探測(cè)任務(wù)[1]。因此,人們對(duì)科學(xué)相機(jī)提出了更高的要求,包括高動(dòng)態(tài)范圍、高靈敏度、低噪聲、低功耗等[2]。

早期的科學(xué)相機(jī)大都使用CCD 圖像傳感器,這是因?yàn)樵诋?dāng)時(shí)的制造工藝下,CMOS 圖像傳感器的各項(xiàng)指標(biāo)都沒(méi)有CCD 優(yōu)秀,無(wú)法滿足高質(zhì)量的成像系統(tǒng)需求[3-4]。近年來(lái),隨著CMOS 傳感器技術(shù)的不斷發(fā)展,CMOS 器件的性能得到了很大的提升,尤其是科學(xué)級(jí)的CMOS 圖像傳感器,其成像質(zhì)量甚至可以媲美CCD[5],這為研制高性能的科學(xué)級(jí)CMOS 相機(jī)奠定了良好的技術(shù)基礎(chǔ)。

針對(duì)國(guó)內(nèi)對(duì)于科學(xué)成像系統(tǒng)的開(kāi)發(fā)需求,文中選擇了國(guó)產(chǎn)科學(xué)級(jí)CMOS圖像傳感器GSENSE6060BSI,設(shè)計(jì)了相機(jī)系統(tǒng)的硬件電路和FPGA 功能模塊,并編寫了相機(jī)的控制軟件。

1 圖像傳感器簡(jiǎn)介

GSENSE6060BSI 是長(zhǎng)光辰芯光電研制的一款國(guó)產(chǎn)背照式sCMOS 圖像傳感器。在傳統(tǒng)的前照式CMOS 器件中,光線在到達(dá)光電二極管之前,需要穿過(guò)多個(gè)介質(zhì)層和金屬布線層,造成器件量子效率和靈敏度的降低。而在背照式器件中,光線可以從沒(méi)有布線層阻檔的襯底背面直接進(jìn)入光電二極管,相比于前照式的CMOS 器件,其量子效率和靈敏度都得到顯著提升[6]。該相機(jī)系統(tǒng)使用GSENSE6060BSI 芯片,其峰值量子效率可以達(dá)到95%,且動(dòng)態(tài)范圍高達(dá)90 dB,是天文和科學(xué)成像應(yīng)用的理想選擇。

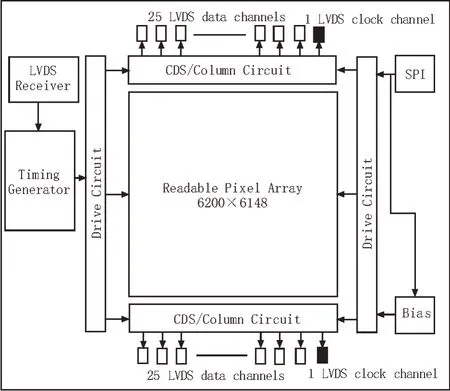

圖1 是GSENSE6060BSI 的結(jié)構(gòu)框圖,該傳感器的有效像素是6 144×6 144,像素尺寸為10 μm×10 μm,圖像數(shù)據(jù)通過(guò)50 個(gè)LVDS 數(shù)據(jù)通道輸出。在STD 模式下,頂部和底部的數(shù)據(jù)通道分別輸出一幅圖像的奇數(shù)行和偶數(shù)行數(shù)據(jù);在HDR 模式下,頂部的25 個(gè)通道輸出一幅低增益的圖像,底部的25 個(gè)通道輸出一幅高增益的圖像。

圖1 GSENSE6060BSI結(jié)構(gòu)框圖

2 硬件電路設(shè)計(jì)

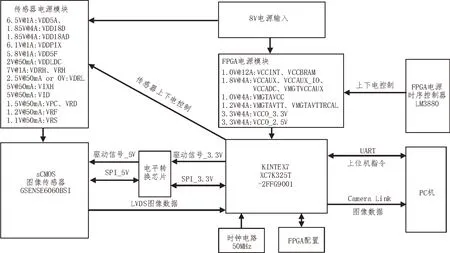

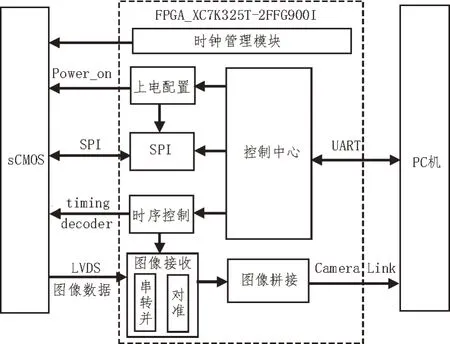

基于GSENSE6060BSI 設(shè)計(jì)的相機(jī)電路如圖2 所示,其中FPGA 是整個(gè)相機(jī)系統(tǒng)的控制核心,傳感器的所有輸入、輸出信號(hào)都需要由FPGA 進(jìn)行控制和處理[7]。因此,該相機(jī)選擇了XILINX KINTEX-7 系列的FPGA 芯片XC7K325T-2FFG900I。該芯片具有大量的IO 引腳和豐富的邏輯資源[8],不僅可以滿足當(dāng)前相機(jī)系統(tǒng)的基本成像需求,還能為后續(xù)的相機(jī)功能完善,比如非均勻性校正、圖像算法移植等提供足夠的硬件資源。

圖2 相機(jī)電路結(jié)構(gòu)

相機(jī)硬件電路包括傳感器電源、FPGA 電源、FPGA 配置、UART 接口、電平轉(zhuǎn)換、Camera Link 接口等,由于相機(jī)整體電路較為龐大,因此文中只選取了其中較為關(guān)鍵的兩點(diǎn)進(jìn)行介紹。

2.1 電源控制

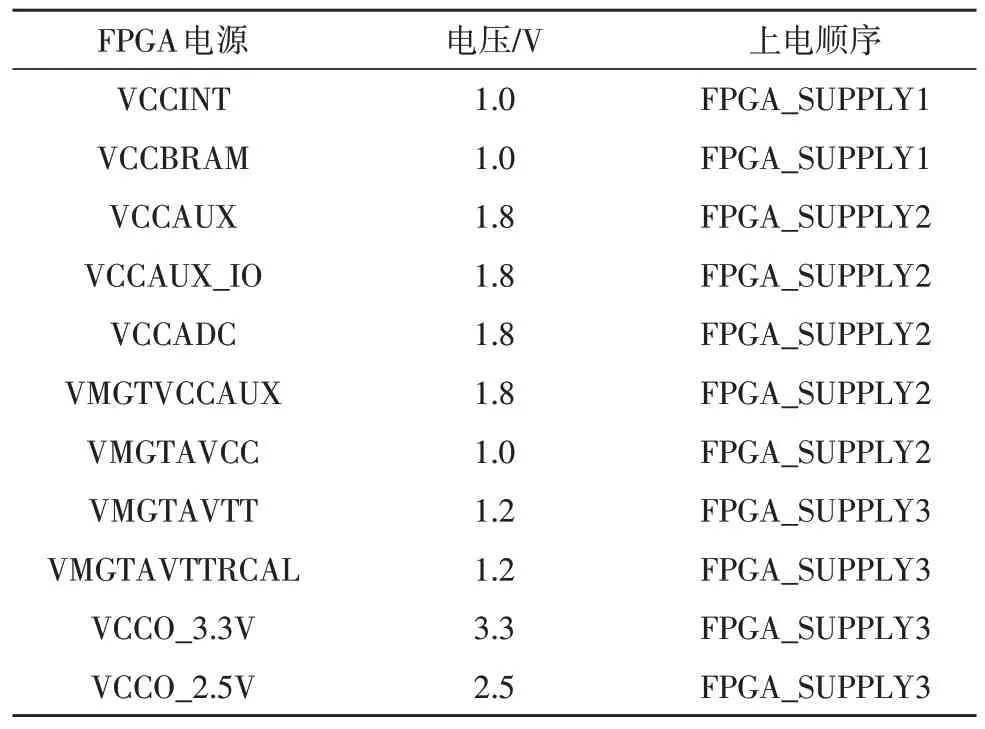

整個(gè)相機(jī)系統(tǒng)的電源可以大致分為兩個(gè)部分:FPGA電源和傳感器電源。FPGA共有11種電源,按上電順序被分為3組,如表1所示。上電時(shí),按照FPGA_SUPPLY1、FPGA_SUPPLY2、FPGA_SUPPLY3 的順序依次上電,下電時(shí)的順序與上電順序正好相反。

表1 FPGA電源

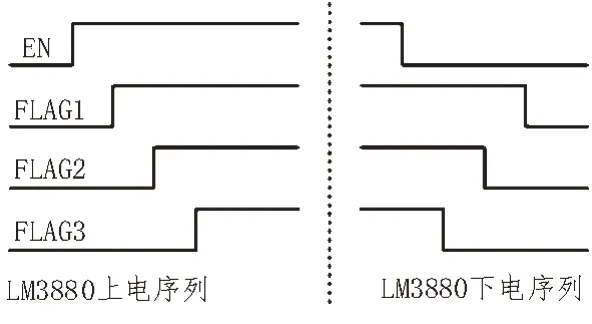

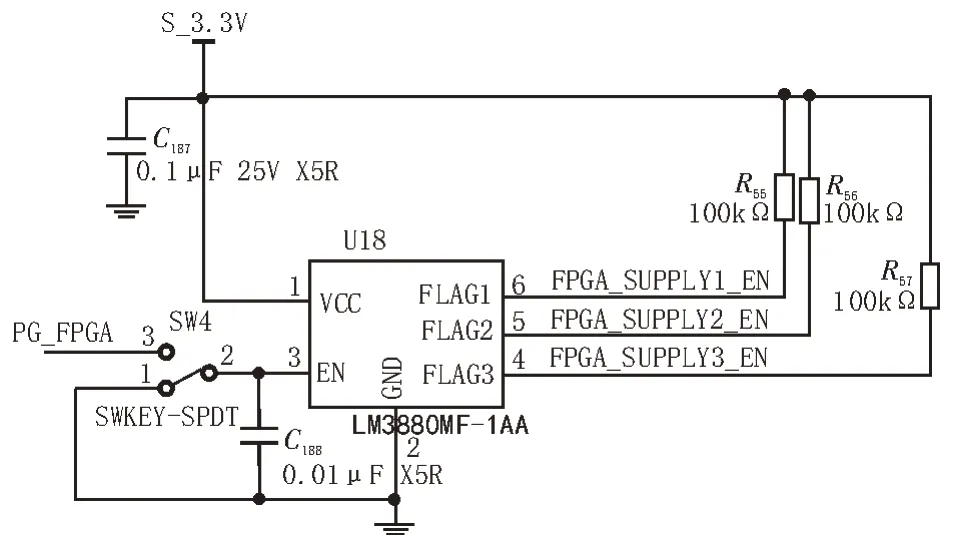

該相機(jī)選用了一款專用的電源時(shí)序控制芯片LM3880 來(lái)對(duì)FPGA 的電源進(jìn)行控制,其時(shí)序波形如圖3 所示,將圖中的FLAG 信號(hào)與FPGA 電源芯片的使能信號(hào)連接就能夠控制FPGA 電源的上電和下電順序,具體電路如圖4 所示。

圖3 LM3880時(shí)序波形

圖4 FPGA電源控制電路

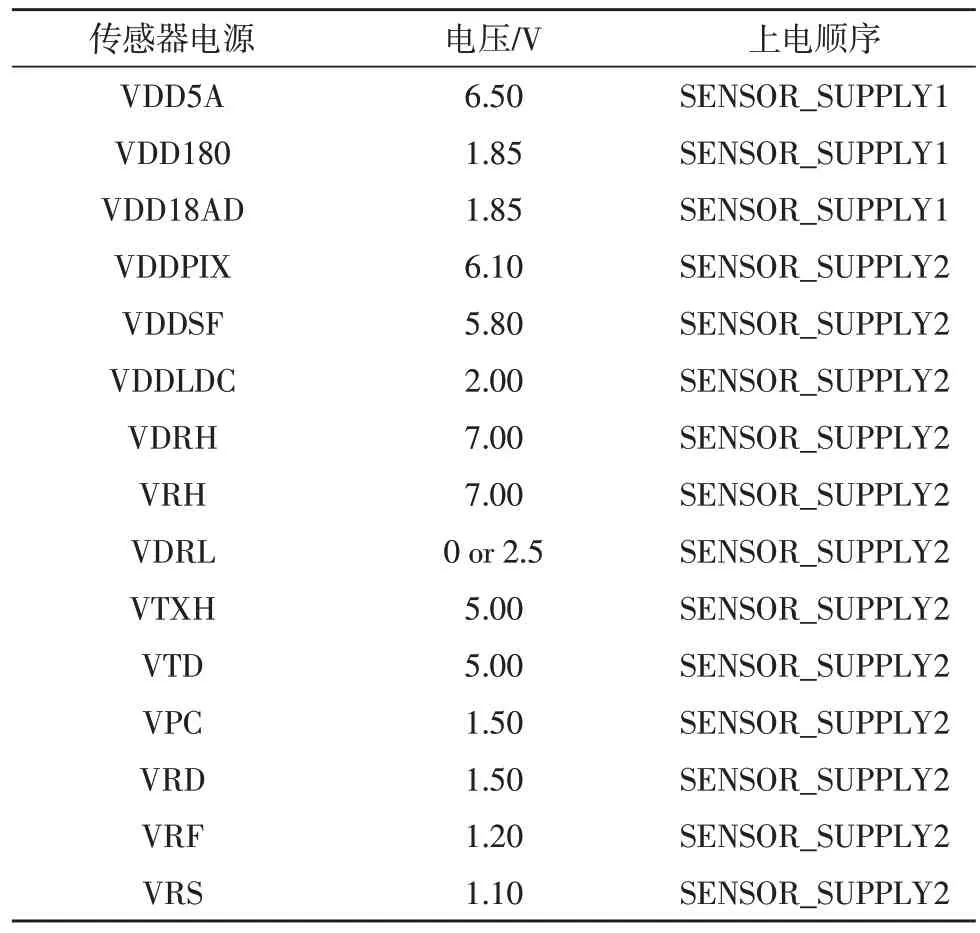

與FPGA 不同的是,傳感器只對(duì)其電源的上電順序有要求,表2 顯示了傳感器的15 種電源及其分組情況,在該相機(jī)系統(tǒng)中,傳感器電源的上電和下電都由FPGA 控制,不需要設(shè)置額外的控制電路。

表2 傳感器電源

2.2 電平轉(zhuǎn)換

傳感器共有53 對(duì)差分信號(hào)和51 個(gè)單端信號(hào),這些信號(hào)都需要連接到FPGA 上。對(duì)于差分信號(hào),可以使用LVDS25 電平標(biāo)準(zhǔn)直接與FPGA 的差分端口連接。而對(duì)于單端信號(hào),由于其高電平達(dá)到了5 V 以上,F(xiàn)PGA 沒(méi)有與之匹配的電平標(biāo)準(zhǔn),因此,需要使用電平轉(zhuǎn)換芯片將信號(hào)統(tǒng)一成LVCMOS33 的電平范圍,然后再與FPGA 的端口進(jìn)行連接。

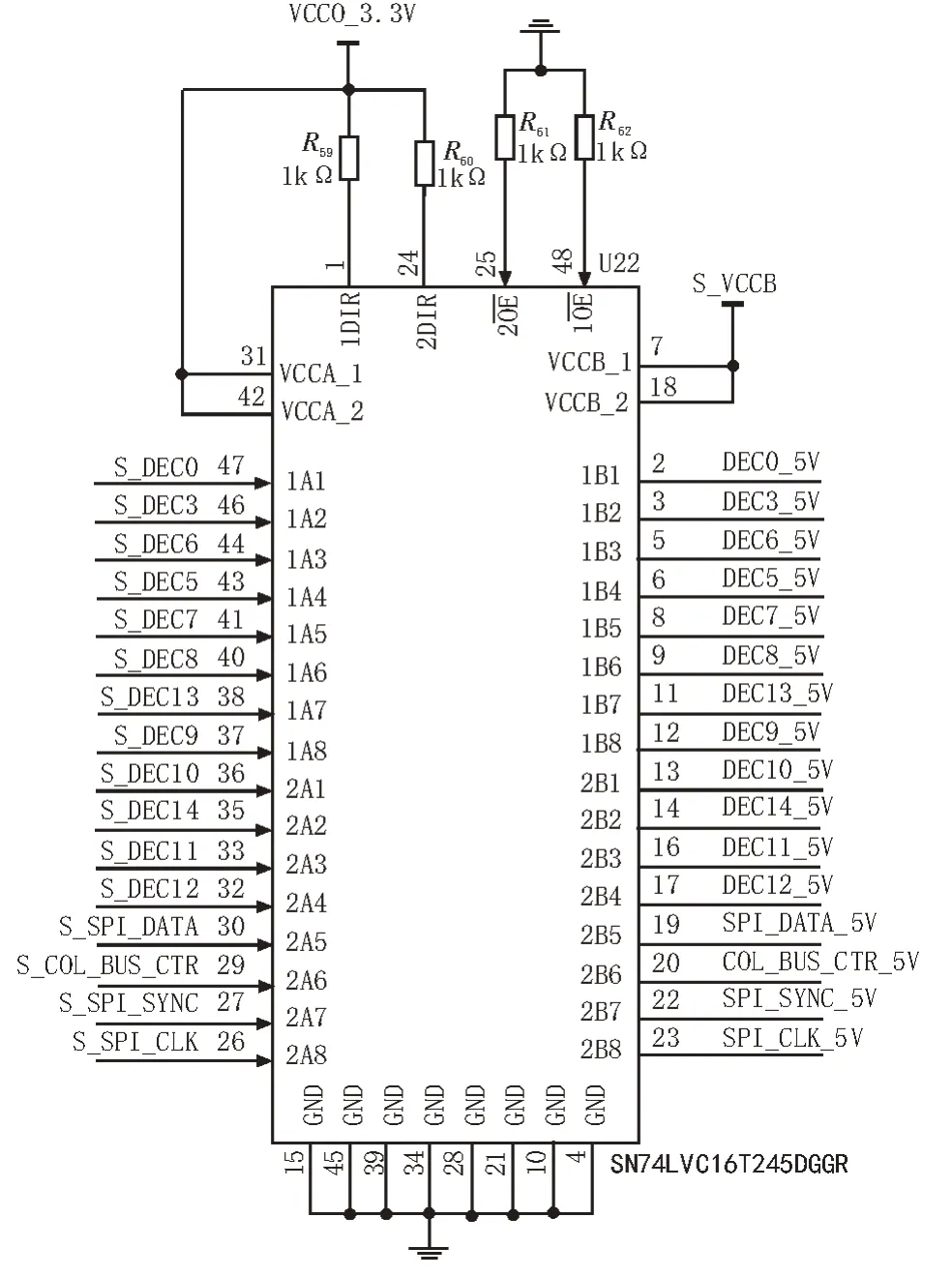

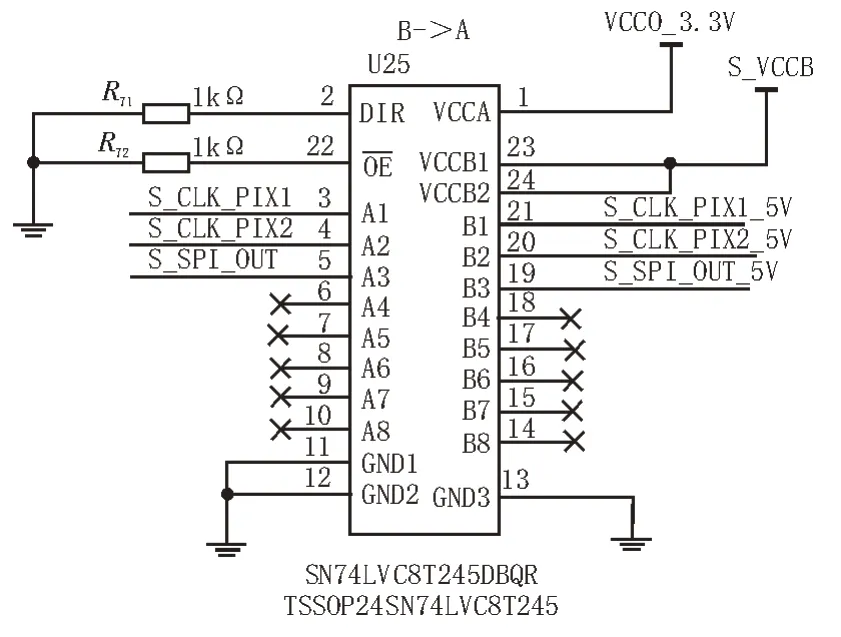

51 個(gè)單端信號(hào)包含48 個(gè)輸入信號(hào)和3 個(gè)輸出信號(hào),其中,48 個(gè)輸入信號(hào)是由FPGA 產(chǎn)生的傳感器控制信號(hào),因此,需要先將FPGA 的3.3 V 電平信號(hào)轉(zhuǎn)換成5 V 的電平信號(hào),然后才能連接到傳感器引腳。該相機(jī)使用了3 片16 bit 的SN74LVC16T245芯片來(lái)實(shí)現(xiàn)這一升壓轉(zhuǎn)換,具體電路如圖5 所示。3 個(gè)輸出信號(hào)包含兩個(gè)輸出時(shí)鐘和一個(gè)SPI 信號(hào),傳感器輸出信號(hào)的高電平為6.5 V,因此,需要先將這些信號(hào)轉(zhuǎn)換到3.3 V 的電平標(biāo)準(zhǔn),然后才能與FPGA 的端口連接。該相機(jī)使用了一片8 bit 的SN74LVC8T245 芯片來(lái)實(shí)現(xiàn)這一降壓轉(zhuǎn)換,具體電路如圖6 所示。

圖5 升壓轉(zhuǎn)換電路

圖6 降壓轉(zhuǎn)換電路

3 FPGA邏輯設(shè)計(jì)

FPGA 是整個(gè)相機(jī)系統(tǒng)的核心處理器,用于驅(qū)動(dòng)相機(jī)正常工作[9]。該設(shè)計(jì)用VHDL 語(yǔ)言編寫了相機(jī)的控制代碼,具體的功能模塊如圖7 所示,其中控制中心模塊接收PC 機(jī)通過(guò)UART 接口發(fā)送的控制指令,對(duì)指令進(jìn)行解析,然后驅(qū)動(dòng)相應(yīng)模塊工作,并將工作狀態(tài)回送給PC 機(jī);時(shí)鐘管理模塊產(chǎn)生相機(jī)系統(tǒng)所需要的不同頻率的時(shí)鐘;上電配置模塊產(chǎn)生傳感器上電過(guò)程中需要的時(shí)序信號(hào)和傳感器電源芯片的使能信號(hào);SPI 是FPGA 與sCMOS 的通信模塊[10],利用SPI 接口可以對(duì)傳感器內(nèi)部寄存器的值進(jìn)行讀寫;時(shí)序控制模塊產(chǎn)生傳感器曝光和讀出的驅(qū)動(dòng)信號(hào),并控制曝光和讀出的位置;圖像接收模塊接收傳感器輸出的LVDS 串行圖像數(shù)據(jù),并將其轉(zhuǎn)換為并行的12 bit 像素?cái)?shù)據(jù);圖像拼接模塊接收單個(gè)的像素?cái)?shù)據(jù)并將其拼接成一幅完整的圖像,然后將圖像數(shù)據(jù)通過(guò)Camera Link 接口傳輸?shù)絇C 機(jī)進(jìn)行顯示。

圖7 FPGA邏輯模塊

3.1 上電配置

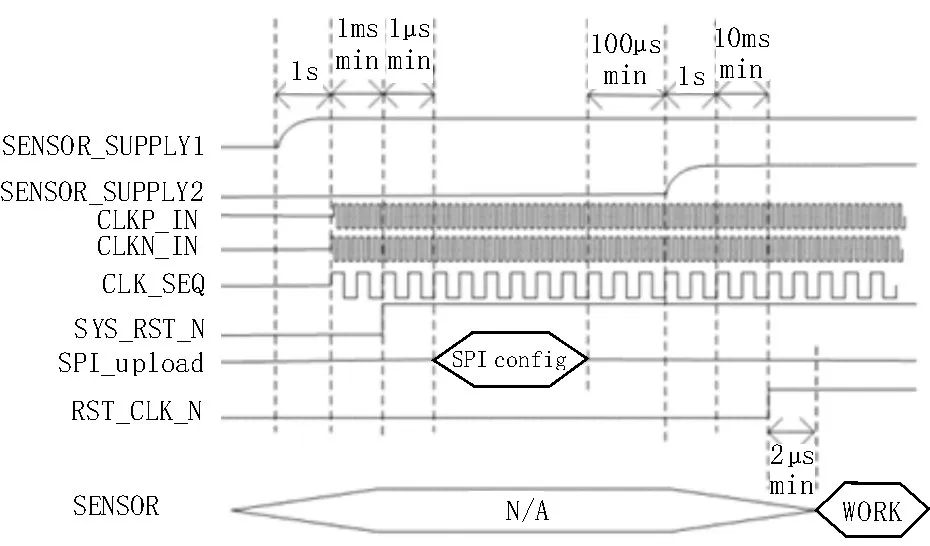

圖8 是傳感器的上電配置時(shí)序,其中SENSOR_SUPPLY1 和SENSOR_SUPPLY2 是傳感器的兩組電源;CLKP_IN、CLKN_IN 是傳感器的LVDS 輸入時(shí)鐘;CLK_SEQ 是FPGA 內(nèi)的邏輯時(shí)鐘,與傳感器的像素時(shí)鐘同頻;SYS_RST_N 是傳感器的系統(tǒng)復(fù)位信號(hào);SPI config 表示對(duì)傳感器的內(nèi)部寄存器進(jìn)行的配置;RST_CLK_N 是傳感器的時(shí)鐘復(fù)位信號(hào)。

圖8 傳感器上電配置

上電配置模塊接收到由控制中心發(fā)來(lái)的上電指令后,先產(chǎn)生第一組傳感器電源芯片的使能信號(hào),給SENSOR_SUPPLY1 上電,然后遵循延遲時(shí)間依次產(chǎn)生時(shí)鐘信號(hào)、系統(tǒng)復(fù)位信號(hào)和SPI 配置信號(hào)。等待傳感器配置完成之后,產(chǎn)生第二組傳感器電源芯片的使能信號(hào),當(dāng)?shù)诙M電源穩(wěn)定后,將時(shí)鐘復(fù)位信號(hào)拉高,2 μs 后傳感器即可開(kāi)始正常工作。

3.2 SPI配置

SPI(Serial Peripheral Interface)是一種全雙工串行通信接口[11],傳感器芯片上設(shè)置有四線SPI 接口,F(xiàn)PGA 可以通過(guò)SPI 接口對(duì)傳感器內(nèi)部寄存器的值進(jìn)行配置,從而控制傳感器的工作模式,同時(shí),傳感器內(nèi)部寄存器的值也可以通過(guò)SPI 接口讀出來(lái)。

3.3 時(shí)序控制

傳感器的時(shí)序控制涉及43 個(gè)信號(hào),其中28 個(gè)信號(hào)是傳感器的驅(qū)動(dòng)信號(hào),另外15個(gè)是decoder信號(hào),用于控制傳感器曝光和讀出的行位置。在STD 模式下,傳感器每次曝光和讀出一行需要占用430 個(gè)像素時(shí)鐘周期,雖然每次曝光和讀出的位置不同,但28 個(gè)驅(qū)動(dòng)信號(hào)的變化卻是相同的。在28 個(gè)驅(qū)動(dòng)信號(hào)中,只有16 個(gè)信號(hào)是變化的,其余的12個(gè)信號(hào)維持固定的電平不變,因此,該設(shè)計(jì)在FPGA 中創(chuàng)建了一個(gè)大小為430×16 的ROM IP 核,用于存儲(chǔ)這16個(gè)驅(qū)動(dòng)信號(hào),每次使用時(shí),只需按照時(shí)鐘周期計(jì)數(shù)將這些驅(qū)動(dòng)信號(hào)從ROM 中讀出即可。

HDR 模式下的時(shí)序控制波形與STD 模式下有所不同,但實(shí)現(xiàn)方法與STD模式相同,此處不再贅述。

3.4 圖像接收

傳感器共有50 對(duì)差分?jǐn)?shù)據(jù)通道,每25 對(duì)通道輸出一行圖像數(shù)據(jù),每個(gè)12 bit 像素都以高位在前、低位在后的串行數(shù)據(jù)格式輸出。根據(jù)傳感器數(shù)據(jù)輸出的特點(diǎn),該相機(jī)在FPGA 內(nèi)設(shè)計(jì)了包含串并轉(zhuǎn)換和對(duì)準(zhǔn)功能的圖像接收模塊。

串并轉(zhuǎn)換是將傳感器輸出的12 位串行數(shù)據(jù)轉(zhuǎn)換成12 位的并行數(shù)據(jù)。在FPGA 內(nèi),設(shè)置一個(gè)12 位的移位寄存器,將傳感器輸出的圖像數(shù)據(jù)依次向左移動(dòng)送入移位寄存器,每移動(dòng)12 位之后,就可以得到一個(gè)并行的12 位數(shù)據(jù)[12]。

串并轉(zhuǎn)換之后雖然得到了一個(gè)12 位的并行數(shù)據(jù),但是由于傳感器輸出和FPGA 數(shù)據(jù)接收之間存在延遲和差異,這個(gè)并行數(shù)據(jù)并不一定是一個(gè)正確的像素?cái)?shù)據(jù),因此,還需要對(duì)數(shù)據(jù)進(jìn)行對(duì)準(zhǔn)。設(shè)計(jì)中的對(duì)準(zhǔn)包括3 個(gè)部分:位對(duì)準(zhǔn)、字對(duì)準(zhǔn)和通道對(duì)準(zhǔn)。

對(duì)準(zhǔn)時(shí),需要將傳感器置于training 模式,在該模式下,傳感器會(huì)輸出已知的訓(xùn)練字,供FPGA 采樣[13]。位對(duì)準(zhǔn)的目的是使采樣時(shí)鐘在數(shù)據(jù)穩(wěn)定的位置進(jìn)行采樣[14],該設(shè)計(jì)使用XINLINX 的原語(yǔ)IDELAY2 對(duì)圖像數(shù)據(jù)進(jìn)行延遲,延遲時(shí)鐘為200 MHz。如果在連續(xù)的8 次延遲中,串并轉(zhuǎn)換之后的12 位數(shù)據(jù)都是一致的,就以第四次延遲之后的位置作為采樣點(diǎn),這樣可以避免采樣時(shí)鐘在數(shù)據(jù)邊沿采樣,保證采樣數(shù)據(jù)的準(zhǔn)確性。字對(duì)準(zhǔn)的目的是使所有通道數(shù)據(jù)的最高位對(duì)齊,保證串并轉(zhuǎn)換之后的12 位數(shù)據(jù)是一個(gè)正確的像素?cái)?shù)據(jù)。該設(shè)計(jì)使用了6 MHz 的像素時(shí)鐘對(duì)圖像數(shù)據(jù)進(jìn)行延遲,每次增加一個(gè)延遲時(shí)鐘,直到串并轉(zhuǎn)換之后的數(shù)據(jù)與訓(xùn)練字相同。通道對(duì)準(zhǔn)的目的是使各個(gè)通道的數(shù)據(jù)對(duì)齊,由于已經(jīng)完成了位對(duì)準(zhǔn)和字對(duì)準(zhǔn),所以只需要對(duì)比各個(gè)通道輸出的第一個(gè)像素的最高位就可以確定各個(gè)通道之間的延遲[15]。

3.5 圖像拼接

傳感器的像素時(shí)鐘為6 MHz,50個(gè)通道每秒可以輸出300 MHz 的像素?cái)?shù)據(jù)。該設(shè)計(jì)使用Camera Link的Medium 模式進(jìn)行數(shù)據(jù)傳輸,傳輸時(shí)鐘為75 MHz,每個(gè)時(shí)鐘周期內(nèi)可以傳輸4 個(gè)像素?cái)?shù)據(jù)[16]。具體的圖像拼接通過(guò)FIFO 進(jìn)行,圖像拼接完成之后,將4 路圖像數(shù)據(jù)和圖像使能信號(hào)連接至Camera Link 接口,由Camera Link 圖像采集卡采集圖像數(shù)據(jù)。

3.6 控制中心

控制中心是FPGA 與PC 機(jī)之間的通信模塊,在整個(gè)相機(jī)系統(tǒng)中扮演著“指揮官”的角色。PC 機(jī)通過(guò)串口向FPGA 發(fā)送指令幀,F(xiàn)PGA 接收到這些指令后就對(duì)指令進(jìn)行解析,然后驅(qū)動(dòng)FPGA 內(nèi)相應(yīng)的模塊工作,最后將工作狀態(tài)以指令幀的格式回送給PC 機(jī)。

指令幀的具體格式為<幀頭><命令字><數(shù)據(jù)字1><數(shù)據(jù)字2><數(shù)據(jù)字3><校驗(yàn)和><信息長(zhǎng)度><幀尾>。幀頭和幀尾都是固定的字節(jié)數(shù)據(jù),用于表示指令的開(kāi)始和結(jié)尾;數(shù)據(jù)字用于傳遞特定的數(shù)值,比如傳感器的曝光時(shí)間、請(qǐng)求的圖像幀數(shù)等;校驗(yàn)和用于驗(yàn)證指令本身的正確性,將命令字和所有數(shù)據(jù)字相加取低8 位即為校驗(yàn)和;信息長(zhǎng)度表示一個(gè)指令幀中除幀頭和幀尾之外的字節(jié)數(shù)。

該相機(jī)系統(tǒng)按照指令幀的格式,定義了PC 機(jī)與FPGA 之間的通信協(xié)議,并用MFC 編寫了相機(jī)控制軟件,利用該軟件已經(jīng)成功實(shí)現(xiàn)了對(duì)相機(jī)的控制。

4 相機(jī)設(shè)計(jì)結(jié)果

該相機(jī)在STD 和HDR 模式下均已順利成像,圖9是傳感器在STD模式下輸出的圖像,圖10和圖11分別是傳感器在HDR 模式下輸出的高增益圖像和低增益圖像(圖中白色虛線為圖像傳感器壞點(diǎn),屬正常現(xiàn)象)。在STD 模式下,相機(jī)的全分辨率幀頻是4.5 fps,在HDR 模式下,相機(jī)的全分辨率幀頻是2 fps。針對(duì)不同的應(yīng)用需求,可選擇不同的工作模式,當(dāng)需要更高幀頻時(shí),選擇STD 模式,當(dāng)需要合成高動(dòng)態(tài)范圍的圖像時(shí),選擇HDR 模式。

圖9 STD模式下的輸出圖像

圖10 HDR模式下輸出的高增益圖像

圖11 HDR模式下輸出的低增益圖像

5 結(jié)論

文中根據(jù)國(guó)產(chǎn)sCMOS 圖像傳感器GSENSE 6060BSI 的特點(diǎn),設(shè)計(jì)了相機(jī)的硬件電路、FPGA 控制代碼和相機(jī)的控制軟件。通過(guò)相機(jī)控制軟件發(fā)送指令給FPGA,由FPGA 產(chǎn)生傳感器的驅(qū)動(dòng)信號(hào)并接收傳感器產(chǎn)生的圖像數(shù)據(jù),最后通過(guò)圖像傳輸接口將圖像數(shù)據(jù)傳輸?shù)絇C機(jī)進(jìn)行顯示。經(jīng)調(diào)試,相機(jī)已經(jīng)順利輸出圖像,證明相機(jī)系統(tǒng)的各部分設(shè)計(jì)是合理的。

該相機(jī)采用Camera Link 接口輸出了圖像數(shù)據(jù),驗(yàn)證了相機(jī)軟件和硬件部分的可行性,但相機(jī)的幀頻沒(méi)有達(dá)到傳感器的最大幀頻26 fps。由于該相機(jī)系統(tǒng)的應(yīng)用場(chǎng)合對(duì)幀頻的要求較低,因此,這樣做是可行的。但是如果相機(jī)系統(tǒng)需要應(yīng)用在對(duì)幀頻要求較高的場(chǎng)合,Camera Link 就無(wú)法滿足相機(jī)的數(shù)據(jù)傳輸要求,此時(shí),應(yīng)使用USB3.0、光纖接口等傳輸速率更高的圖像傳輸方式。